Titulaires du brevet RU 2559705:

L'invention concerne le domaine de l'informatique, de l'automatisation et peut être utilisée dans diverses structures numériques et systèmes de contrôle automatique, de transmission d'informations, etc.

Dans divers systèmes de calcul et de contrôle, les décodeurs sont largement utilisés, mis en œuvre sur la base d'une logique transistor-transistor et couplée à l'émetteur, fonctionnant selon les lois de l'algèbre booléenne et ayant deux états logiques "0" et "1" en sortie, caractérisés par des potentiels bas et haut. L'architecture classique du décodeur a été publiée dans des articles et des livres, les microcircuits sont produits en série.

Un inconvénient majeur de cette classe de décodeurs est que ses éléments logiques, utilisant des signaux binaires potentiels, ont une structure à plusieurs niveaux qui ne peut pas ou être utilisée de manière inefficace dans les processus technologiques modernes à basse tension, ainsi que la non-linéarité des modes de fonctionnement des éléments et la criticité des paramètres de la structure des éléments logiques et des signaux d'entrée. Au final, cela conduit à une diminution des performances des décodeurs connus.

En tant que dispositifs de traitement d'informations numériques, des étages de transistor pour la conversion de variables logiques d'entrée (courants) sont également utilisés, mis en œuvre sur la base de miroirs de courant qui mettent en œuvre la fonction de traitement logique des variables de courant d'entrée.

Un inconvénient important des circuits connus de cette classe est qu'ils ne mettent pas en œuvre la fonction de conversion de deux signaux de courant d'entrée ayant quatre états "00", "01", "10", "11" en quatre signaux de courant de sortie. Cela ne permet pas sur sa base de créer une base complète pour le traitement du signal avec des variables de courant, fonctionnant sur les principes de l'algèbre linéaire.

Dans les travaux, ainsi que dans les monographies du co-auteur de cette application, il est montré que l'algèbre booléenne est un cas particulier d'une algèbre linéaire plus générale, dont la mise en œuvre pratique dans la structure des dispositifs informatiques et logiques d'une nouvelle génération d'automatisation nécessite la création d'une base d'éléments spéciaux, mise en œuvre sur la base de la logique avec une représentation interne à deux valeurs et à valeurs multiples signaux dans lesquels l'équivalent d'un signal logique standard est un quantum de courant Ι 0. Le dispositif revendiqué "Décodeur 2 à 4" se réfère à ce type de dispositifs logiques et fonctionne avec des signaux de courant d'entrée et génère un signal de courant de sortie.

Le prototype le plus proche du dispositif revendiqué est un dispositif logique "Décodeur 2 en 4", présenté dans le brevet US 5742154, contenant les première 1 et deuxième 2 entrées logiques du dispositif, les première 3, deuxième 4, troisième 5, quatrième 6 sorties logiques de courant du dispositif, première 7, deuxième 8 et troisième 9 transistors de sortie, dont les bases sont combinées et connectées à la première source de tension de polarisation 10, aux quatrième 11, cinquième 12 et sixième 13 transistors de sortie d'un type de conductivité différent, dont les bases sont combinées et connectées à la deuxième source de tension de polarisation 14, l'émetteur du premier transistor de sortie 7 connecté à l'émetteur du quatrième transistor à 11 sorties, l'émetteur du deuxième transistor à 8 sorties est connecté à l'émetteur du cinquième transistor à 12 sorties, l'émetteur du troisième transistor à 9 sorties est connecté à l'émetteur du sixième transistor à 13 sorties, les 3 premières sorties logiques de courant du dispositif sont connectées au collecteur du premier transistor à 7 sorties, le deuxième 4 sortie logique de courant des appareils a est connecté au collecteur du troisième transistor de sortie 9, le collecteur du quatrième 11 du transistor de sortie est connecté à la troisième sortie logique de 5 courant du dispositif, le collecteur du sixième transistor de sortie 13 est connecté à la quatrième 6 sortie logique de courant du dispositif, les premier 15 et deuxième 16 miroirs de courant, mis en correspondance avec le premier 17 bus alimentation, le troisième miroir de courant 18 correspondant à la deuxième ligne 19 de l'alimentation électrique, une source de courant de référence auxiliaire 20.

L'objectif principal de la présente invention est de créer un élément logique qui assure le décodage de l'état de deux variables logiques d'entrée et la formation de quatre signaux de sortie sous forme courante. Au final, cela permet d'augmenter la vitesse des dispositifs de conversion d'informations connus à l'aide du décodeur proposé et de créer une base d'éléments de dispositifs informatiques fonctionnant sur les principes de l'algèbre linéaire à valeurs multiples.

La tâche est résolue par le fait que dans le dispositif logique "Décodeur 2 à 4" (Fig.1), contenant les première 1 et deuxième 2 entrées logiques de l'appareil, les 3 premières, les secondes 4, les troisième 5, les quatrièmes 6, les sorties logiques actuelles de l'appareil, les 7 premières, les deuxième 8 et troisième 9 transistors de sortie, dont les bases sont combinées et connectées à la première 10 source de tension de polarisation, le quatrième 11, le cinquième 12 et le sixième 13 transistors de sortie d'un type de conductivité différent, dont les bases sont combinées et connectées à la deuxième source de tension de polarisation 14, l'émetteur de la première 7 sortie le transistor est connecté à l'émetteur du quatrième transistor de sortie ET, l'émetteur du deuxième transistor de sortie 8 est connecté à l'émetteur du cinquième transistor de sortie 12, l'émetteur du troisième transistor de sortie 9 est connecté à l'émetteur du sixième transistor de sortie 13, la première sortie logique à 3 courants du dispositif est connectée au collecteur du premier transistor de sortie 7, le deuxième 4 la sortie logique de courant de l'appareil est connectée au collecteur de la troisième 9 sortie autour du transistor, le collecteur du quatrième transistor de sortie 11 est connecté à la troisième sortie logique à 5 courants de l'appareil, le collecteur du sixième transistor à 13 sorties est connecté à la quatrième sortie logique à 6 courants de l'appareil, les premier 15 et deuxième 16 miroirs de courant, en correspondance avec le premier 17 bus de la source d'alimentation, le troisième 18 courant un miroir adapté au deuxième bus 19 de l'alimentation, une source auxiliaire du courant de référence 20, de nouveaux éléments et connexions sont fournis - la première 1 entrée logique du dispositif est connectée à l'entrée du troisième 18 miroir de courant, la deuxième 2 entrée logique du dispositif est connectée à l'entrée du premier 15 miroir de courant, la première 21 la sortie de courant du premier 15 miroir de courant est connectée aux émetteurs combinés des deuxième 8 et cinquième 12 transistors de sortie et à travers une source de courant de référence auxiliaire 20 est connectée au deuxième bus d'alimentation 19, la deuxième 22 sortie de courant du premier 15 miroir de courant est connectée aux émetteurs combinés des 7 premiers et quatrième 11 transistors de sortie transistor ov et est connecté à la première sortie de courant 23 du troisième miroir de courant 18, le collecteur du deuxième transistor de sortie 8 est connecté à l'entrée du deuxième miroir de courant 16, dont la sortie courant est connectée aux émetteurs combinés des troisième 9 et sixième 13 transistors de sortie et est connectée à la deuxième sortie 24 courant du troisième 18 courant des miroirs, et le collecteur du cinquième transistor de sortie 12 est connecté au deuxième bus 19 de l'alimentation.

Un schéma du dispositif logique prototype est représenté sur la Fig. 1. Sur la Fig. 2 montre un schéma du dispositif revendiqué selon la revendication 1 des revendications.

figure. 3 montre un schéma du dispositif revendiqué conformément à la clause 2, clause 3, clause 4 des revendications.

figure. 4 est un diagramme schématique de la Fig. 3 dans l'environnement de simulation informatique MC9 avec une implémentation spécifique des principales unités fonctionnelles (miroirs de courant, sources de courant de référence).

figure. 5 montre les résultats de la simulation informatique du circuit de la Fig. 4.

Le dispositif logique "Décodeur 2 par 4" de la Fig. 2 contient les première 1 et deuxième 2 entrées logiques de l'appareil, les première 3, deuxième 4, troisième 5, quatrième 6 sorties logiques de courant de l'appareil, les premier 7, deuxième 8 et troisième 9 transistors de sortie, dont les bases sont combinées et connectées à la première 10 source de tension de polarisation, quatrième 11, cinquième 12 et sixième 13 transistors de sortie d'un type différent de conductivité, dont les bases sont combinées et connectées à la deuxième source de tension de polarisation 14, l'émetteur du premier transistor de sortie 7 est connecté à l'émetteur du quatrième transistor de sortie 11, l'émetteur du deuxième transistor de sortie 8 est connecté à l'émetteur du cinquième transistor de sortie 12 transistor, l'émetteur du troisième transistor de sortie 9 est connecté à l'émetteur du sixième transistor de sortie 13, la première sortie logique à 3 courants de l'appareil est connectée au collecteur du premier transistor de sortie 7, la deuxième sortie logique à 4 courants du dispositif est connectée au collecteur du troisième transistor à 9 sorties, le collecteur du quatrième transistor à 11 sorties est connecté à le troisième 5 courant lo par la sortie logique du dispositif, le collecteur du sixième transistor de sortie 13 est connecté à la quatrième sortie logique 6 courant du dispositif, les premier 15 et deuxième 16 miroirs de courant, appariés au premier 17 bus de l'alimentation, le troisième 18 miroir de courant, apparié au deuxième bus 19 de l'alimentation, une source auxiliaire de la référence courant 20. La première 1 entrée logique du dispositif est connectée à l'entrée du troisième 18 miroir de courant, la deuxième 2 entrée logique du dispositif est connectée à l'entrée du premier 15 miroir de courant, la première 21 sortie de courant du premier 15 miroir de courant est connectée aux émetteurs combinés des deuxième 8 et cinquième 12 transistors de sortie et à travers une source de courant de référence auxiliaire 20 est connectée au deuxième bus d'alimentation 19, la deuxième sortie de courant 22 du premier 15 miroir de courant est connectée aux émetteurs combinés des premier 7 et quatrième 11 transistors de sortie et connectée à la première 23 sortie de courant du troisième 18 miroir de courant, le collecteur du deuxième 8 transistor de sortie est connecté de l'entrée la maison du deuxième 16 miroir de courant, dont la sortie de courant est connectée aux émetteurs combinés des troisième 9 et sixième 13 transistors de sortie et est connectée à la deuxième 24 sortie de courant du troisième 18 miroir de courant, et le collecteur du cinquième 12 transistor de sortie est connecté au deuxième 19 bus d'alimentation.

figure. 3 selon la revendication 2 des revendications, la première 1 entrée logique du dispositif est reliée à l'entrée du troisième 18 miroir de courant par le premier étage inverseur supplémentaire, réalisé sous la forme du premier 26 miroir de courant additionnel, adapté au premier 17 bus de l'alimentation.

figure. 3 selon la revendication 3 des revendications, le collecteur du quatrième 11 transistor de sortie est connecté à la troisième sortie logique 5 courant du dispositif par l'intermédiaire d'un deuxième étage inverseur supplémentaire réalisé sous la forme d'un deuxième miroir de courant supplémentaire 27 adapté au deuxième bus 19 de l'alimentation.

De plus, à la Fig. 3 selon la revendication 4 des revendications, le collecteur du sixième 13 transistor de sortie est connecté à la quatrième sortie logique 6 courant du dispositif par un troisième étage inverseur supplémentaire réalisé sous la forme d'un troisième miroir de courant additionnel 28 adapté au deuxième bus 19 de l'alimentation.

Considérons le fonctionnement du circuit décodeur proposé avec les entrées et sorties de courant de la Fig. 2.

Le décodeur 2 en 4 implémente des fonctions bien connues:

où A 0, A ¯ 0 sont des signaux directs et inverses à l'entrée 1 du dispositif de la fig. 2,

A 1, A ¯ 1 - signaux directs et inverses à l'entrée 2 du dispositif de la fig. 2.

Une caractéristique de leur implémentation en algèbre linéaire est l'utilisation de l'opération de différence tronquée à cette fin:

quelle table de vérité est donnée ci-dessous

Il résulte du tableau que des quatre combinaisons possibles des valeurs des variables d'entrée, la valeur unitaire de la fonction correspond à une seule combinaison correspondant à la condition A 0\u003e A 1. En spécifiant des variables d'entrée directes et inverses dans la table de vérité, on peut obtenir une valeur de fonction unique correspondant à l'une des combinaisons possibles de valeurs de variable d'entrée.

L'application de cette opération conduit à la représentation suivante des fonctions logiques du décodeur:

Ces opérations sont mises en œuvre comme suit.

Les signaux des variables d'entrée A 0 et A 1 à travers les entrées logiques 1 et 2 sont envoyés aux premiers 15 et troisième 18 miroirs de courant, à l'aide desquels ces signaux sont multipliés et leur signe change. Dans ce cas, le signal A 0 est transmis sous la forme d'un courant circulant (c'est-à-dire sous la forme de A 0) et à l'aide du troisième miroir de courant 18 est converti en un courant circulant (c'est-à-dire sous la forme -A 0), et A 1 est fourni sous forme directe sous la forme d'un courant entrant (c'est-à-dire sous la forme de -A 1) et à l'aide du premier miroir de courant 15 est converti en un courant sortant (c'est-à-dire sous la forme A 1).

Au point de jonction des sorties 22 du premier miroir de courant 15 et 23 du troisième miroir de courant 18, l'opération A 1 -A 0 est mise en oeuvre. Le signal de différence est appliqué aux émetteurs combinés des transistors 7 et 11, dont les modes de fonctionnement sont définis par les première 10 et seconde 14 sources de tension de polarisation.

Si le signal de différence est positif, c'est-à-dire A 0 -A 1\u003e 0, le transistor 7 est fermé et le transistor 11 est ouvert, et un quantum du courant circulant est donné à la sortie 5, correspondant à - (A 0 -A 1) \u003d A 1 -A 0, réalisant l'expression (2). Pour toute autre combinaison de valeurs de quanta de courant à la sortie 5, il n'y aura pas de courant.

Si A 0 -A 1 ≤ 0, alors le transistor 7 est ouvert, et le transistor 11 est fermé, et un quantum du courant circulant est émis vers la sortie 3, correspondant à A 0 -A 1, qui met en œuvre l'expression (3). Pour toute autre combinaison de valeurs de quanta de courant à la sortie 3, il n'y aura pas de courant.

Au point de jonction de la sortie 21 du premier miroir de courant et de la source auxiliaire de courant de référence 20, A 1 -1 est soustrait. Le signal de différence est appliqué aux émetteurs combinés des transistors 8 et 12, dont les modes de fonctionnement sont fixés par les première 10 et seconde 14 sources de tension de polarisation. Si le signal de différence est positif, c'est-à-dire A 1 -1\u003e 0, le transistor 8 est bloqué et le transistor 12 est passant. Si le signal de différence est inférieur ou égal à zéro, alors le transistor 8 est passant et le transistor 12 est bloqué.

Dans le premier cas, le signal traversant le transistor 12 est fermé à la masse. Dans le second cas, le quantum du courant différentiel sortant A 1 -1 à l'aide du troisième miroir de courant 16 est converti en quantum du courant sortant 1-A 1 et le quantum de courant entrant -A 0 en est soustrait. Le signal de différence est appliqué aux émetteurs combinés des transistors 9 et 13, dont les modes de fonctionnement sont fixés par les première 10 et seconde 14 sources de tension de polarisation. Si le signal de différence est positif, c'est-à-dire le transistor 9 est bloqué et le transistor 13 est passant. Dans ce cas, un signal de différence (1-A 1) -A 0 est émis vers la sortie 6, sous la forme d'un quantum de courant circulant, réalisant l'expression (4). Pour toute autre combinaison de valeurs de quanta de courant à la sortie 4, il n'y aura pas de courant.

La spécificité de ce dispositif est la présentation des signaux de sortie sous forme de quanta du courant entrant (aux sorties 3 et 4) et sortant (aux sorties 5 et 6). Dans le cas où tous les signaux de sortie de même direction sont nécessaires, le circuit décodeur représenté sur la Fig. 3. Sa différence avec le circuit de la Fig. 2 est l'utilisation de deux miroirs de courant supplémentaires 27 et 28, aux entrées desquels sont connectés les collecteurs des transistors 11 et 13, et les sorties sont les sorties 5 et 6 du décodeur. En conséquence, tous les signaux de sortie sont représentés par des quanta du courant entrant.

Comme on peut le voir à la lecture de la description ci-dessus, la mise en œuvre du dispositif "2 en 4" se fait sous forme de fonctions logiques standards selon les lois de l'algèbre linéaire en formant la différence de quanta de courant 10. La mise en œuvre d'éléments sur des miroirs de courant permet dans de nombreux cas de réduire la tension d'alimentation, et puisque tous les éléments du les circuits fonctionnent en mode actif, en supposant qu'il n'y a pas de saturation pendant le processus de commutation, les performances globales du dispositif augmentent. L'utilisation de valeurs stables des quanta de courant I 0, ainsi que la détermination du signal de sortie par la différence de ces courants permettent une petite dépendance du fonctionnement du circuit à des facteurs externes de déstabilisation (écart de la tension d'alimentation, effets de rayonnement et de température, interférences de mode commun, etc.).

Montré à la Fig. 9, fig. 10, les résultats de la simulation confirment les propriétés spécifiées des schémas revendiqués.

Ainsi, les solutions de circuits envisagées du dispositif logique "Décodeur 2 en 4" sont caractérisées par une représentation binaire courante du signal et peuvent être utilisées comme base pour le calcul et le contrôle de dispositifs utilisant l'algèbre linéaire, dont un cas particulier est l'algèbre booléenne.

BIBLIOGRAPHIE

1. Brevet US 6243319 B1, fig. 13.

2. Brevet US 5604712 A.

3. Brevet US 4514829 A.

4. Brevet US 20120020179 A1.

5. Brevet US 6920078 B2.

6. Brevet US 6324117 B1, fig. 3.

7. Demande de brevet US 20040018019 A1.

8. Brevet US 5568061 A.

9. Brevet US 5148480 A, fig. 4.

10. Brzozowski I., Zachara L., Kos A. Méthode de conception universelle des décodeurs n-à-2n // Conception mixte de circuits et de systèmes intégrés (MIXDES), 2013 Actes de la 20e Conférence internationale, 2013. - P. 279 -284, fig. 1.

11. Subramanyam M.V. Switching Theory and Logic Design / Firewall Media, 2011. Deuxièmement, - 783 s, Fig. 3.174.

12. SN74LVC1G139 Décodeur 2 à 4 lignes [ressource électronique]. URL: http://www.ti.com/lit/ds/symlink/sn741vc1g139.pdf.

13. Brevet US 8159304, fig. cinq.

14. Brevet américain n ° 5977829, fig. 1.

15. Brevet américain n ° 5789982, fig. 2.

16. Brevet américain n ° 5140282.

17. Brevet américain n ° 6 624 701, fig. 4.

18. Brevet américain n ° 6529078.

19. Brevet américain n ° 5734294.

20. Brevet américain n ° 5557220.

21. Brevet américain n ° 6624701.

22. Brevet RU n ° 2319296.

23. Brevet RU n ° 2436224.

24. Brevet RU n ° 2319296.

25. Brevet RU n ° 2321157.

26. Brevet US 6556075, fig. 2.

27. Brevet US 6556075, fig. 6.

28. Chernov N.I., Yugai V.Y., Prokopenko N.N., et al. - Rostov-sur-le-Don, 2013. - C.146-149.

29. Malyugin V. D. Implémentation de fonctions booléennes par polynômes arithmétiques // Automatisation et télémécanique, 1982. №4. S. 84-93.

30. Chernov N.I. Fondements de la théorie de la synthèse logique des structures numériques sur le domaine des nombres réels // Monographie. - Taganrog: TRTU, 2001 - 147 p.

31. Chernov N.I. Synthèse linéaire des structures numériques de ASOIU "// Tutoriel. - Taganrog: TRTU, 2004 - 118 p.

1. Décodeur 2 par 4, contenant les première (1) et deuxième (2) entrées logiques de l'appareil, les première (3), deuxième (4), troisième (5), quatrième (6) sorties logiques de courant de l'appareil, la première (7), les deuxième (8) et troisième (9) transistors de sortie, dont les bases sont combinées et connectées à la première (10) source de tension de polarisation, les quatrième (11), cinquième (12) et sixième (13) transistors de sortie d'un type de conductivité différent, dont les bases sont combinées et connecté à la deuxième (14) source de tension de polarisation, l'émetteur du premier (7) transistor de sortie est connecté à l'émetteur du quatrième (11) transistor de sortie, l'émetteur du deuxième (8) transistor de sortie est connecté à l'émetteur du cinquième (12) transistor de sortie, l'émetteur du troisième (9) transistor de sortie le transistor est connecté à l'émetteur du sixième (13) transistor de sortie, la première (3) sortie logique de courant du dispositif est connectée au collecteur du premier (7) transistor de sortie, la deuxième (4) sortie logique de courant du dispositif est connectée au collecteur du troisième (9) transistor de sortie, le collecteur Le quatrième (11) transistor de sortie est connecté à la troisième (5) sortie logique de courant du dispositif, le collecteur du sixième (13) transistor de sortie est connecté à la quatrième (6) sortie logique de courant du dispositif, les premier (15) et deuxième (16) miroirs de courant sont appariés avec le premier (17) bus de l'alimentation, le troisième (18) miroir de courant, adapté au deuxième (19) bus de l'alimentation, une source auxiliaire du courant de référence (20), caractérisé en ce que la première (1) entrée logique du dispositif est connectée à l'entrée du troisième (18) ) miroir de courant, la deuxième (2) entrée logique du dispositif est connectée à l'entrée du premier (15) miroir de courant, la première (21) sortie de courant du premier (15) miroir de courant est connectée aux émetteurs combinés des deuxième (8) et cinquième (12) transistors de sortie et à travers une source de courant de référence auxiliaire (20) est connectée au deuxième (19) bus d'alimentation, la deuxième (22) sortie de courant du premier (15) miroir de courant est connectée aux émetteurs combinés des première (7) et quatrième (11) sorties transistors et connecté à la première (23) sortie de courant du troisième (18) miroir de courant, le collecteur du deuxième (8) transistor de sortie est connecté à l'entrée du deuxième (16) miroir de courant, dont la sortie de courant est connectée aux émetteurs combinés des troisième (9) et sixième (13) des transistors de sortie et connectés à la deuxième (24) sortie de courant du troisième (18) miroir de courant, et le collecteur du cinquième (12) transistor de sortie est connecté au deuxième (19) bus d'alimentation.

2. Décodeur 2 par 4 selon la revendication 1, caractérisé en ce que la première (1) entrée logique du dispositif est reliée à l'entrée du troisième (18) miroir de courant par le premier étage inverseur supplémentaire réalisé sous la forme du premier (26) miroir de courant additionnel, apparié avec le premier (17) bus d'alimentation.

3. Décodeur 2 par 4 selon la revendication 1, caractérisé en ce que le collecteur du quatrième (11) transistor de sortie est connecté à la troisième (5) sortie logique de courant du dispositif par l'intermédiaire d'un deuxième étage inverseur supplémentaire, réalisé sous la forme d'un deuxième (27) miroir de courant supplémentaire, adapté avec le deuxième (19) bus d'alimentation.

4. Décodeur 2 par 4 selon la revendication 1, caractérisé en ce que le collecteur du sixième (13) transistor de sortie est connecté à la quatrième (6) sortie logique de courant du dispositif par l'intermédiaire d'un troisième étage inverseur supplémentaire, réalisé sous la forme d'un troisième (28) miroir de courant supplémentaire, adapté avec le deuxième (19) bus d'alimentation.

Brevets similaires:

SUBSTANCE: l'invention concerne des moyens de codage utilisant un livre de codes réduit à réinitialisation adaptative. Le résultat technique consiste à réduire la quantité d'informations transmises du côté réception vers le côté émission.

L'invention concerne la technologie informatique, à savoir le codage d'informations vidéo. Le résultat technique consiste à augmenter l'efficacité du codage et du décodage d'un flux binaire d'informations vidéo en divisant les données en couches d'entropie.

L'invention concerne un procédé de codage d'une séquence d'entiers, un dispositif de stockage et un signal porteur d'une telle séquence codée, ainsi qu'un procédé de décodage de cette séquence codée.

L'invention concerne un procédé de précodage, ainsi qu'un système et un procédé de construction d'un livre de codes de précodage dans un système à entrées multiples et sorties multiples (MIMO).

L'invention concerne le domaine de la technologie dans laquelle des signaux numérisés sont utilisés, et peuvent être appliqués dans des dispositifs de communication, enregistrement, enregistrement, lecture, conversion, codage et compression de signaux, systèmes de contrôle automatique.

L'invention concerne le domaine des télécommunications, à savoir le domaine des dispositifs cryptographiques et des procédés de vérification d'une signature numérique électronique (EDS). ...

L'invention concerne le domaine du traitement numérique du signal, en particulier la compression de données et l'amélioration du codage entropique de séquences vidéo. Le résultat technique est d'augmenter l'efficacité et de réduire la complexité de calcul du codage entropique. Le procédé de traitement d'un flux de données constitué d'une pluralité d'éléments syntaxiques est basé sur le remplacement d'éléments syntaxiques dont les valeurs ont une forte probabilité d'occurrence par des éléments syntaxiques dont les valeurs ont une faible probabilité. Un contexte est défini pour un élément de syntaxe et la probabilité d'occurrence des valeurs de ces éléments de syntaxe dans le modèle de flux de données qui ont un contexte spécifique est calculée. Remplacez les éléments de syntaxe du flux de données par un contexte spécifique si la probabilité d'occurrence calculée de la valeur de l'élément de syntaxe est supérieure à un seuil spécifié, par des éléments de syntaxe dont les valeurs ont une faible probabilité. 3 n. et 10 c.p. F-cristaux, 4 dwg., 2 tbl.

L'invention concerne les technologies de la communication et est destinée à mesurer le spectre des signaux acoustiques d'information. Le résultat technique est d'augmenter la précision de la mesure du spectre des signaux acoustiques d'information, d'étendre la fonctionnalité du dispositif en liant les valeurs instantanées du spectre aux intervalles de temps du signal acoustique réglables en durée. Pour cela, la méthode de mesure du spectre utilise une transformée cosinus discrète (DCT) au lieu d'une transformée de Fourier rapide (FFT), ce qui permet d'augmenter la précision de mesure du spectre des signaux acoustiques en augmentant la résolution, en diminuant le niveau des lobes latéraux de la transformée de fenêtre dans le spectre, et en réduisant les oscillations dans l'estimation de l'amplitude du spectre composants, et permet également de réduire la durée des segments du signal acoustique sur lesquels le spectre instantané est mesuré, tandis que la formation de deux signaux (principal et supplémentaire) au lieu d'un est effectuée et que le signal acoustique numérique supplémentaire est orthogonal par rapport au signal principal, les valeurs instantanées mesurées du spectre sont également liées , le module du spectre et la caractéristique phase-fréquence du signal aux segments du signal acoustique temporel réglables en position temporelle et en durée, sur lesquels ce spectre est mesuré. 2 n.p. f-ly, 8 dwg

L'invention concerne la communication sans fil. Le résultat technique est une augmentation de l'immunité au bruit, de la fiabilité et de l'efficacité de la communication, tandis que la consommation d'énergie peut être réduite. Pour cela, le procédé comprend: une étape S1, dans laquelle le maître génère un code de séquence par un codeur spécifique et transmet le code de séquence à chaque dispositif esclave en continu pendant une durée prédéterminée selon une requête de communication, le codeur spécifique étant un registre à décalage de rétroaction exécuté sur un polynôme spécifique, dont l'ordre et les coefficients sont corrélés à la demande de communication, alors que tous les coefficients et valeurs initiales ne sont pas égaux à 0 en même temps; la période de temps prédéterminée est supérieure ou égale à la somme de la période de sommeil et de la période de détection de l'esclave, qui est un cycle de sommeil et de réveil; l'étape S2, dans laquelle le dispositif esclave reçoit une partie continue du code de séquence dans la période de détection, décode le code de séquence par un décodeur correspondant au codeur, et effectue une opération correspondante selon le résultat du décodage. 2 n. et 10 c.p. f-ly, 5 dwg

L'invention concerne la technologie des communications et est destinée au codage et au décodage de signaux. Le résultat technique est d'améliorer la précision des signaux d'encodage et de décodage. Un procédé de codage de signal comprend l'obtention d'un signal de domaine fréquentiel en fonction d'un signal d'entrée; attribuer des bits prédéterminés au signal de domaine fréquentiel selon une règle d'attribution prédéterminée; ajuster l'attribution de bits pour le signal de domaine fréquentiel lorsque la fréquence la plus élevée du signal de domaine fréquentiel auquel les bits sont attribués dépasse une valeur prédéterminée; et coder le signal de domaine de fréquence selon l'attribution de bits pour le signal de domaine de fréquence. 4 n. et 16 c.p. f-ly, 9 malades.

L'invention concerne le domaine des télécommunications et a pour but de protéger les informations secrètes transmises. Le résultat technique est un haut niveau de sécurité des informations cryptées. Procédé de cryptage d'informations, comprenant la construction d'une table de correspondances de symboles et de leurs équivalents dans l'espace (00; FF) dans le système de nombres hexadécimaux, générant une nouvelle table de correspondances en changeant la table d'origine, en décalant la table d'origine, c'est-à-dire la chaîne de correspondance est décalée du nombre de caractères spécifié, les informations source sont codées et compressées à la taille souhaitée à l'aide de la table de codage Unicode appropriée. 2 onglet.

L'invention concerne le codage / décodage d'un signal numérique constitué de blocs séquentiels d'échantillons. Le résultat technique est d'améliorer la qualité du son encodé. Le codage consiste à appliquer une fenêtre de pondération à deux blocs de M échantillons consécutifs. En particulier, une telle fenêtre de pesée est asymétrique et contient quatre sections distinctes se poursuivant successivement le long des deux blocs précités, la première section augmentant pendant le premier intervalle de temps, la deuxième section ayant une valeur de pondération constante pendant le deuxième intervalle de temps, la troisième section décroissant avec le cours le troisième intervalle de temps et la quatrième section ont une valeur de pondération constante pendant le quatrième intervalle de temps. 6 n. et 11 c.p. F-cristaux, 10 malades.

L'invention concerne le domaine du traitement de signaux numériques, en particulier des procédés de codage-décodage d'images vidéo numériques. Le résultat technique est d'augmenter le taux de compression des images vidéo avec une légère diminution de la qualité de l'image décodée par rapport aux images qui ont une nature haute fréquence du spectre du signal. Un procédé de codage-décodage d'images vidéo numériques est proposé. Selon le procédé, dans le processus de codage, une composante haute fréquence supplémentaire est ajoutée ligne par ligne à la composante basse fréquence de la transformée en ondelettes pour lisser la fonction d'origine, qui est utilisée pour le codage, mais est supprimée du côté du décodage en utilisant un filtre passe-bas. De plus, le codage est mis en œuvre à l'aide d'une fonctionnelle avec deux objectifs d'augmenter le taux de compression des données et de maintenir la qualité de l'image décodée, et les caractéristiques du filtre décodeur sont prises en compte comme une limitation de la communication au stade du codage. 8 dwg, 3 tbl

L'invention concerne le domaine de la communication sans fil. Le résultat technique est d'améliorer la qualité de la communication en supprimant les interférences séquentielles entre les flux de signaux. Le procédé de précodage comprend: l'exécution d'un prétraitement de précodage sur un signal à transmettre, le prétraitement provoquant une augmentation de la puissance du signal à transmettre; sélection de l'algorithme de limitation de puissance selon la règle de sélection; effectuer une opération de limitation de puissance sur le signal prétraité selon l'algorithme de limitation de puissance sélectionné; et générer le signal pré-codé en fonction du signal limité en puissance. Un mode de réalisation de la présente invention décrit en outre un émetteur, un récepteur et un système de précodage. Dans la présente invention, l'influence défavorable exercée par l'opération de limitation de puissance sur la transmission de signal peut être réduite autant que possible tandis que la puissance d'émission est limitée en utilisant l'opération de limitation de puissance. 5 n. et 12 p.p. f-ly, 8 dwg

La présente invention concerne le domaine du codage et du décodage et a pour but de quantifier des vecteurs d'enveloppe de fréquence. EFFET: efficacité accrue de la quantification des vecteurs d'enveloppe de fréquence. Le procédé comprend: la division des N enveloppes de fréquence dans une trame en N1 vecteurs, où chaque vecteur dans les N1 vecteurs comprend M enveloppes de fréquence; quantifier le premier vecteur dans N1 vecteurs en utilisant le premier livre de codes pour obtenir un mot de code correspondant au premier vecteur quantifié, où ledit premier livre de codes est divisé en sections 2B1; déterminer, selon le mot de code correspondant au premier vecteur quantifié, que le premier vecteur quantifié est associé à la ième région dans les régions 2B1 dudit premier livre de codes; définir le deuxième livre de codes selon le livre de codes de la ième région; et quantifier le deuxième vecteur en N1 vecteurs sur la base dudit deuxième livre de codes. Dans des modes de réalisation de la présente invention, les enveloppes de fréquence sont divisées en une pluralité de vecteurs avec des dimensions plus petites, de sorte qu'une quantification vectorielle peut être effectuée sur les vecteurs d'enveloppe de fréquence en utilisant un livre de codes avec moins de bits. 2 n. et 6 c.p. f-ly, 3 dwg

Le groupe des inventions concerne le domaine du codage. Le résultat technique est d'améliorer l'efficacité de la compression des données. Le procédé de codage de données d'entrée (D1) comprend la définition de blocs sensiblement répétés de données et / ou de paquets de données dans au moins l'un des éléments de données d'entrée (D1), dans lequel les blocs de données et / ou les paquets de données comprennent une pluralité correspondante d'éléments, où les éléments comprennent une pluralité morceaux; déterminer si les éléments sont immuables à l'intérieur de blocs essentiellement répétitifs de données et / ou de paquets de données, et / ou déterminer que les éléments dans les blocs essentiellement répétitifs de données et / ou de paquets de données changent; coder les éléments inchangés en données codées (E2) en utilisant au moins un symbole correspondant ou au moins un bit correspondant, indiquant qu'il n'y a pas de changements dans les éléments inchangés par rapport à leurs éléments correspondants dans le bloc de données de référence et / ou le paquet de données; et coder les éléments modifiés en données codées (E2). 6 n. et 28 z.p. f-ly, 8 dwg

L'invention concerne les décodeurs. Le résultat technique consiste à augmenter la vitesse des dispositifs de conversion d'informations utilisant le décodeur de l'invention. La première entrée logique du dispositif est connectée à l'entrée du troisième miroir de courant, la deuxième entrée logique du dispositif est connectée à l'entrée du premier miroir de courant, la première sortie de courant du premier miroir de courant est connectée aux émetteurs combinés des deuxième et cinquième transistors de sortie et via une source de courant de référence auxiliaire est connectée au deuxième bus de la source d'alimentation, la deuxième sortie de courant du premier miroir de courant est connectée aux émetteurs combinés des premier et quatrième transistors de sortie et connectée à la première sortie de courant du troisième miroir de courant, le collecteur du deuxième transistor de sortie est connecté à l'entrée du deuxième miroir de courant, dont la sortie de courant est connectée aux émetteurs combinés des troisième et sixième transistors de sortie et est connectée avec la deuxième sortie de courant du troisième miroir de courant, et le collecteur du cinquième transistor de sortie est connecté au deuxième bus de l'alimentation. 3 C.p. f-ly, 5 dwg

3. Schéma fonctionnel, désignation graphique conventionnelle et table de vérité d'un décodeur complet pour 3 entrées.

4. Décodeurs linéaires: fonction de commutation, UGO et circuit.

5. Décodeurs pyramidaux: fonction de commutation, UGO et circuit.

6. Décodeurs rectangulaires à plusieurs étages: fonction de commutation, UGO et circuit.

7. Décodeurs cadencés et intégrés.

Décodeur est une unité opérationnelle combinatoire qui convertit un mot d'entrée en un signal à l'une de ses sorties.

Ainsi, un décodeur est un noeud dans lequel chaque combinaison de signaux d'entrée correspond à la présence d'un signal sur l'une des sorties.

La figure 4 montre un schéma fonctionnel d'un décodeur avec n entrées et 2 n -1 sorties.

Technique de synthèse du décodeur

Les conditions de fonctionnement d'un décodeur pour deux entrées peuvent être représentées par une table de vérité (tableau 3). Le nombre de sorties d'un tel décodeur est m \u003d 2 2 \u003d 4.

|

Tableau 3 |

||||||||||||||||||||||||||||||||||||

|

Tableau de vérité du décodeur 2 × 4

|

||||||||||||||||||||||||||||||||||||

Les fonctions de commutation des sorties du décodeur selon cette table de vérité sont écrites comme suit:

Nous transformons les expressions (4) pour l'implémentation dans la base NAND:

Des images conventionnelles du décodeur utilisé dans la construction de schémas fonctionnels sont représentées sur la figure 7, où a est la désignation générale du décodeur; b - désignation d'un décodeur matriciel. Les entrées du décodeur sont marquées avec des nombres décimaux représentant des poids binaires, des sorties - avec des images décimales des combinaisons de codes correspondantes.

Désignation des décodeurs: 155 ID1, 555ID6, etc.

3. Analyse du fonctionnement du scrambler

Objectif et principe de fonctionnement des codeurs.

L'examen de la question se fait en interrogeant les stagiaires depuis leur place et au tableau selon le plan suivant:

Rendez-vous

Table de vérité

Méthodes de synthèse des circuits

Exemples des schémas les plus simples

Questions discutées avec les stagiaires

Brouilleurs:

1. Objectif, logique de fonctionnement et classification des codeurs.

2. Schéma fonctionnel, désignation graphique conventionnelle et table de vérité du codeur pour n entrées.

3. Schéma fonctionnel, désignation graphique conventionnelle et table de vérité du codeur pour 4 entrées.

4. Synthèse de brouilleurs dans diverses bases.

5. Principes de construction des encodeurs prioritaires.

Brouilleur est une unité fonctionnelle d'un ordinateur numérique et est conçue pour convertir un code unitaire (un code dans lequel une seule variable prend une seule valeur) en un code de position (binaire).

En d'autres termes, l'embrouilleur remplit les fonctions opposées aux fonctions du décrypteur.

Un codeur complet possède 2 m entrées et m sorties. Dans ce cas, si un signal d'entrée est appliqué à l'un des circuits d'entrée du codeur, alors un mot correspondant au numéro du circuit excité est formé à ses sorties.

Synthèse d'un encodeur équivalent

Soit m \u003d 2, alors le nombre d'entrées du codeur est de quatre. Le tableau de fonctionnement d'un tel codeur sera le suivant (Tableau 4).

|

Tableau 4 |

||||||||||||||||||||||||||||||

|

Tableau d'état du codeur 4 × 2

Synthèse de brouilleur prioritaire Considérez le principe de fonctionnement du codeur «4 × 2 ". La table de vérité pour cet encodeur est présentée dans le tableau. 5. Il ressort du tableau que lors de la construction d'un codeur de priorité, les ensembles 1, 2, 4 et 8 sont utilisés; | ||||||||||||||||||||||||||||||

.

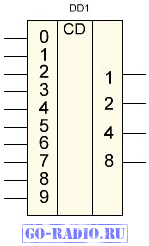

Microcircuit K176ID1, K561ID1

Le décodeur BCD partiel a 4 entrées pour recevoir le code binaire et 10 sorties pour son équivalent décimal.

Le niveau actif de l'entrée et de la sortie est élevé. Lorsqu'un code binaire compris entre 8 et 15 est appliqué au microcircuit, un niveau logique bas est défini sur toutes les sorties (le décryptage n'est pas effectué). Le microcircuit ne dispose pas d'entrées supplémentaires pour le stroboscope, cependant, l'extension de la profondeur de bits est facile à mettre en œuvre si vous sacrifiez les deux dernières décimales:

Dans le diagramme ci-dessus, le bit le plus significatif inversé du code d'entrée est utilisé comme signal d'échantillonnage pour DD2. Dans ce cas, les broches 4,5 (chiffres décimaux élevés 8,9) des microcircuits ne sont pas utilisées et le circuit est un décodeur décimal binaire à 4 bits complet.

Dans la figure suivante, en raison de l'utilisation d'un microcircuit séparé pour contrôler les décodeurs, le nombre de sorties est augmenté à 64 (code d'entrée 6 octets).

——————————————-

Microcircuit K176ID2

Décodeur-convertisseur. Conçu pour convertir le code binaire en code pour un indicateur à sept segments. Il n'y a pas de circuits pour contrôler la virgule décimale dans le microcircuit. En plus du décodeur lui-même, le microcircuit dispose d'un déclencheur de verrouillage qui vous permet de stocker les données actuelles.

Possède une entrée de données à quatre chiffres et sept sorties pour connecter un affichage numérique à sept segments. Les niveaux actifs de l'entrée et de la sortie sont élevés, mais si nécessaire, ils peuvent être inversés par un signal sur l'entrée de service S. A un niveau bas sur cette entrée, le signal de sortie actif est haut, avec "1" sur S - bas. Cela permet de connecter des matrices numériques à la fois avec une anode commune et une cathode commune sans inverseurs supplémentaires. Une autre entrée de service K est utilisée pour contrôler la matrice. "0" à l'entrée K active l'affichage, "1" éteint la matrice.

Et la troisième entrée de service C sert à verrouiller les informations entrant dans l'entrée du décodeur. Lorsque C est élevé, le signal est immédiatement décodé et envoyé à l'indicateur. Lorsqu'il passe à "0", le code d'entrée est verrouillé et affiché indépendamment des changements dans l'entrée jusqu'à ce que le niveau à l'entrée C soit à nouveau élevé. La mémorisation se produit sur un déclin de haut niveau.

Les commutateurs de sortie du microcircuit K176ID2 sont capables de résister à des courants de court-circuit numériquement égaux au niveau de la tension d'alimentation (en mA) et peuvent donc être chargés directement sur des voyants LED (par exemple, AL305, ALS324, ALS321) sans amplificateurs de courant supplémentaires.

Microcircuit K176IDZ

Analogue complet de K176ID2 en termes d'algorithme de brochage et de fonctionnement. La différence réside dans les commutateurs de sortie à drain ouvert. Cela permet de connecter directement les anodes d'indicateurs fluorescents qui nécessitent une tension relativement élevée (jusqu'à 15 V) pour leur alimentation à la sortie du décodeur. Lors de l'utilisation d'un microcircuit avec de tels indicateurs, un journal doit être envoyé à l'entrée de service S. "0".

——————————————-

Microcircuit 564ID4

Décodeur-convertisseur. Conçu pour convertir un code binaire en code pour un indicateur à sept segments (y compris LCD). Il n'y a pas de chaînes pour contrôler le point décimal.

La principale différence par rapport à K176ID2 est la présence d'une troisième sortie pour alimenter les commutateurs de sortie, qui supportent une tension jusqu'à 15 V.Pour l'alimentation antiphase de l'écran LCD, il existe un amplificateur spécial (entrée S, sortie P). Considérons ses travaux plus en détail sur l'exemple de connexion de l'indicateur LCD IZHKTs1-1 / 18.

La principale différence par rapport à K176ID2 est la présence d'une troisième sortie pour alimenter les commutateurs de sortie, qui supportent une tension jusqu'à 15 V.Pour l'alimentation antiphase de l'écran LCD, il existe un amplificateur spécial (entrée S, sortie P). Considérons ses travaux plus en détail sur l'exemple de connexion de l'indicateur LCD IZHKTs1-1 / 18.

Supposons que le décodeur lui-même, comme tous les nœuds précédents de l'appareil, soit alimenté par une tension de 5 V (broche 16), et que l'indicateur LCD nécessite une tension alternative d'une amplitude de 15 V. la broche 6 (entrée S) est un signal de niveau TTL (5 V) et une fréquence de 100 Hz. Ce signal va à la broche 1 (broche P) sans inversion, mais son amplitude augmente jusqu'à une tension de 15 V.

Supposons que le décodeur lui-même, comme tous les nœuds précédents de l'appareil, soit alimenté par une tension de 5 V (broche 16), et que l'indicateur LCD nécessite une tension alternative d'une amplitude de 15 V. la broche 6 (entrée S) est un signal de niveau TTL (5 V) et une fréquence de 100 Hz. Ce signal va à la broche 1 (broche P) sans inversion, mais son amplitude augmente jusqu'à une tension de 15 V.

Le même signal lorsque le niveau est actif (logique 1) inverse les signaux de la sortie du décodeur (similaire à 176ID2,3). Les commutateurs de sortie du microcircuit étant alimentés par une source de 15 V, le niveau sur eux passera de 0 à 15 V à une fréquence de 100 Hz, et en antiphase avec le signal P. Ainsi, une tension alternative sera présente sur les segments actifs de l'indicateur, et 0 sur les inactifs.

Il est à noter que le décodeur est complet - c.-à-d. capable d'afficher non seulement les nombres de 0 à 9, mais aussi les symboles "L", "H", "P", "A", "-" correspondant au code binaire 10-14. Avec le code 15, tous les segments sont supprimés.

Bien que l'objectif principal du microcircuit soit de contrôler l'indicateur LCD, sa puissance de sortie est suffisante pour allumer la matrice LED (à une tension d'alimentation allant jusqu'à 10 V - même sans résistances de limitation de courant). En modifiant le niveau à l'entrée S, il est possible d'alimenter les matrices à la fois avec une anode commune et une cathode commune. La sortie P n'est pas utilisée dans ce cas.

——————————————-

Microcircuit 564ID5

Le décodeur diffère du 564ID4 en l'absence de la sortie P et possède un registre de verrouillage à quatre bits similaire à K176ID2.

Le registre est commandé par l'entrée C: "1" - passage direct du code au décodeur puis aux sorties pour connecter les segments indicateurs, "0" - informations de verrouillage pour l'affichage. Dans ce mode, le microcircuit ne répond pas aux modifications du code binaire en entrée. Le verrouillage de l'information se produit au moment d'une baisse du niveau à l'entrée C.

Une caractéristique intéressante des décodeurs K176ID2, K176ID3, 564ID4 et 564ID5 est la même disposition des broches d'entrée et de sortie du même nom.

——————————————-

Microcircuit KR1561ID6

Un boîtier de microcircuit contient deux décodeurs décimaux binaires indépendants pour deux entrées et quatre sorties. Chaque décodeur est équipé d'une entrée de déclenchement.

Les niveaux d'entrée et de sortie actifs sont élevés et les entrées fermées sont faibles. A "0" à l'entrée S, le décodeur fonctionne (à la sortie, l'équivalent décimal du code d'entrée apparaît), à "1" - toutes les sorties sont mises à "0".

Les niveaux d'entrée et de sortie actifs sont élevés et les entrées fermées sont faibles. A "0" à l'entrée S, le décodeur fonctionne (à la sortie, l'équivalent décimal du code d'entrée apparaît), à "1" - toutes les sorties sont mises à "0".

Microcircuit KR1561ID7

Un analogue complet du KR1561ID6 en termes de câblage et d'algorithme de fonctionnement, mais des onduleurs sont installés aux sorties des deux décodeurs (le niveau de sortie actif est bas).

En raison de la présence de sorties inverses, le microcircuit est idéal pour piloter la plupart des décodeurs CMOS lorsqu'ils sont en cascade. Dans la figure ci-dessous, dans le circuit de commande du groupe K561ID1, un décodeur du microcircuit KR1561ID7 a été utilisé, ce qui a permis de construire un décodeur avec 32 sorties sur seulement cinq boîtiers.

En raison de la présence de sorties inverses, le microcircuit est idéal pour piloter la plupart des décodeurs CMOS lorsqu'ils sont en cascade. Dans la figure ci-dessous, dans le circuit de commande du groupe K561ID1, un décodeur du microcircuit KR1561ID7 a été utilisé, ce qui a permis de construire un décodeur avec 32 sorties sur seulement cinq boîtiers.

Pour construire un décodeur complet pour 8 sorties vers le microcircuit KR1561ID6 (code de sortie - direct) ou KR1561ID7 (code de sortie - inverse), il suffit d'ajouter un seul onduleur:

——————————————-

Les dispositifs logiques sont divisés en deux classes: combinatoires et séquentielles.

L'appareil s'appelle combinatoiresi ses signaux de sortie à un certain moment dans le temps sont uniquement déterminés par les signaux d'entrée se produisant à ce moment dans le temps.

Sinon, l'appareil est appelé une machine à états séquentiels ou finis (machine numérique, machine avec mémoire). Les appareils séquentiels ont toujours des éléments de mémoire. L'état de ces éléments dépend de l'historique des signaux d'entrée. Les signaux de sortie des appareils série sont déterminés non seulement par les signaux disponibles aux entrées à un instant donné, mais également par l'état des éléments de mémoire. Ainsi, la réponse d'un équipement série à certains signaux d'entrée dépend de l'historique de son fonctionnement.

Parmi les dispositifs combinatoires et séquentiels, il existe des dispositifs typiques qui sont les plus largement utilisés dans la pratique.

Brouilleurs

Un codeur est un dispositif combinatoire qui convertit les nombres décimaux en un système de nombres binaires, et chaque entrée peut se voir attribuer un nombre décimal, et un ensemble de signaux logiques de sortie correspond à un certain code binaire. L'encodeur est parfois appelé «codeur» et est utilisé, par exemple, pour convertir des nombres décimaux saisis sur le clavier d'un clavier en nombres binaires.

Si le nombre d'entrées est si grand que toutes les combinaisons possibles de signaux de sortie sont utilisées dans le codeur, alors un tel codeur est dit complet, sinon tout, alors incomplet. Le nombre d'entrées et de sorties dans un codeur complet est lié par le rapport n \u003d 2 m, où n est le nombre d'entrées, m est le nombre de sorties.

Ainsi, pour convertir le code du clavier en un nombre binaire à quatre chiffres, il suffit de n'utiliser que 10 entrées, alors que le nombre total d'entrées possibles sera de 16 (n \u003d 2 4 \u003d 16), donc un encodeur 10 × 4 (de 10 à 4) sera incomplet ...

Prenons un exemple de construction d'un encodeur pour convertir un code d'unité à dix chiffres (nombres décimaux de 0 à 9) en un code binaire. Dans ce cas, on suppose que le signal correspondant à une unité logique n'est fourni qu'à une seule entrée à la fois. La désignation conventionnelle d'un tel codeur et la table de correspondance des codes sont illustrées à la Fig. 3.35.

En utilisant cette table de recherche, nous écrirons des expressions logiques, y compris dans la somme logique les variables d'entrée qui correspondent à l'unité d'une variable de sortie. Ainsi, à la sortie de 1, il y aura un "1" logique lorsque le "1" logique est soit à l'entrée X 1, soit X 3, ou X 5, ou X 7, ou X 9, c'est-à-dire 1 \u003d X 1 + X 3 + X 5 + X 7 + X 9

De même, on obtient y 2 \u003d X 2 + X 3 + X 6 + X 7 y 3 \u003d X 4 + X 5 + X 6 + X 7 y 4 \u003d X 8 + X 9

Représentons sur la fig. 3.36 le schéma d'un tel codeur utilisant des éléments OR.  En pratique, un encodeur prioritaire est souvent utilisé. Dans de tels codeurs, le code numérique binaire correspond au numéro le plus élevé de l'entrée à laquelle le signal "1" est appliqué, c'est-à-dire qu'il est autorisé à envoyer des signaux à plusieurs entrées du codeur prioritaire, et il définit le code du nombre correspondant à l'entrée principale en sortie.

En pratique, un encodeur prioritaire est souvent utilisé. Dans de tels codeurs, le code numérique binaire correspond au numéro le plus élevé de l'entrée à laquelle le signal "1" est appliqué, c'est-à-dire qu'il est autorisé à envoyer des signaux à plusieurs entrées du codeur prioritaire, et il définit le code du nombre correspondant à l'entrée principale en sortie.

Prenons comme exemple (Fig. 3.37) un codeur de priorité (codeur de priorité) K555IVZ de la série de microcircuits K555 (TTLSh).

Le codeur dispose de 9 entrées inversées, désignées par PR l,…, PR 9. PR est synonyme de priorité. Le codeur dispose de quatre sorties inverses B l, ..., B 8. L'abréviation B signifie "bus" (de l'anglais. Bus). Les chiffres déterminent la valeur du niveau actif (zéro) dans le bit correspondant du nombre binaire. Par exemple, B 8 signifie que zéro sur cette sortie correspond au nombre 8. Il s'agit évidemment d'un codeur incomplet.

Si toutes les entrées ont une unité logique, toutes les sorties ont également une unité logique, qui correspond au nombre 0 dans ce que l'on appelle le code inverse (1111). Si au moins une entrée a un zéro logique, alors l'état des signaux de sortie est déterminé par le plus grand nombre d'entrée, qui a un zéro logique, et ne dépend pas des signaux aux entrées ayant un nombre inférieur.

Par exemple, si l'entrée PR 1 est un zéro logique et que toutes les autres entrées sont un un logique, alors les sorties ont les signaux suivants: B 1 - 0, B 2 - 1, B 4 - 1, B 8 - 1, qui correspond au nombre 1 en code inverse (1110).

Si l'entrée PR 9 est zéro logique, alors, quels que soient les autres signaux d'entrée, les sorties ont les signaux suivants: V 1 - 0, V 2 - 1, V 4 - 1, V 8 - 0, qui correspond au nombre 9 dans le code inverse (0110) ...

Le but principal de l'encodeur est de convertir le numéro de la source du signal en un code (par exemple, le numéro d'un bouton enfoncé sur un clavier).

Décodeurs

Un appareil combiné est appelé, qui convertit un code binaire à n bits en un signal logique qui apparaît en sortie, dont le nombre décimal correspond au code binaire. Le nombre d'entrées et de sorties dans ce que l'on appelle le décodeur complet est lié par le rapport m \u003d 2 n, où n est le nombre d'entrées et m est le nombre de sorties. Si un nombre incomplet de sorties est utilisé dans le fonctionnement d'un décodeur, alors un tel décodeur est appelé incomplet. Ainsi, par exemple, un décodeur avec 4 entrées et 16 sorties sera complet, et s'il n'y avait que 10 sorties, il serait incomplet.

Tournons-nous, par exemple, vers le décodeur K555ID6 de la série K555 (Fig. 3.38).

Le décodeur dispose de 4 entrées directes, désignées par А 1, ..., А 8. L'abréviation A signifie «adresse» (de l'adresse anglaise). Ces entrées sont appelées adressables. Les nombres déterminent les valeurs du niveau actif (unité) dans le bit correspondant du nombre binaire. Le décodeur dispose de 10 sorties inverses Y 0, ..., Y 9. Les chiffres définissent le nombre décimal correspondant au nombre binaire donné sur les entrées. Evidemment, ce décodeur est incomplet.

La valeur du niveau actif (zéro) a la sortie, dont le nombre est égal au nombre décimal, déterminé par le nombre binaire à l'entrée. Par exemple, si toutes les entrées ont des zéros logiques, alors la sortie Y 0 est un zéro logique et sur les autres sorties il y en a un logique. Si l'entrée A 2 est une entrée logique et que les autres entrées sont un zéro logique, alors la sortie Y 2 est un zéro logique et les autres sorties sont un zéro logique. Si l'entrée est un nombre binaire supérieur à 9 (par exemple, toutes les entrées sont une, ce qui correspond au binaire 1111 et au décimal 15), alors toutes les sorties sont une logique.

Le décodeur est l'un des dispositifs logiques les plus utilisés. Il est utilisé pour construire divers dispositifs combinatoires.

Les chiffreurs et décodeurs considérés sont des exemples des convertisseurs de code les plus simples.

Convertisseurs de code

En général, ils appellent des appareils conçus pour convertir un code en un autre et effectuent souvent des conversions de code non standard. Les convertisseurs de code sont désignés par X / Y.

Considérons les caractéristiques de l'implémentation du convertisseur en utilisant l'exemple d'un convertisseur de code à trois éléments en un code à cinq éléments. Supposons qu'il soit nécessaire de mettre en œuvre la table de correspondance des codes illustrée à la Fig. 3.39.

Ici, N désigne un nombre décimal correspondant au code binaire d'entrée. Les convertisseurs de code créent souvent un schéma décodeur-crypteur. Le décodeur convertit le code d'entrée en un nombre décimal, puis le décodeur forme le code de sortie. Le schéma du convertisseur, créé selon ce principe, est illustré à la Fig. 3.40, où un codeur à diode matricielle est utilisé. Le principe de fonctionnement d'un tel convertisseur est assez simple. Par exemple, quand à toutes les entrées du décodeur il y a un "O" logique, alors un "1" logique apparaît à sa sortie 0, ce qui conduit à l'apparition de "1" aux sorties de 4 et 5, c'est-à-dire que la première ligne de la table de correspondance des codes est implémentée.

L'industrie produit un grand nombre de crypteurs, décodeurs et des convertisseurs de code, tels qu'un décodeur à portes 4 × 16 (K555IDZ), un convertisseur de code pour piloter une matrice LED 7 × 5 (K155ID8), un convertisseur de code pour contrôler un indicateur à barres (K155ID15), etc.

L'un des éléments très importants de la technologie numérique, et en particulier dans les ordinateurs et les systèmes de contrôle, sont les chiffreurs et les décodeurs.

Lorsque nous entendons le mot brouilleur ou décodeur, des phrases de films d'espionnage viennent à l'esprit. Quelque chose comme: décrypter l'envoi et crypter la réponse.

Il n'y a rien de mal à cela, car des crypteurs et des décrypteurs sont utilisés dans les machines de cryptage de nos résidences et de l'étranger.

Brouilleurs.

Ainsi, un codeur (codeur) est un dispositif électronique, dans ce cas un microcircuit, qui convertit le code d'un système numérique en le code d'un autre système. Les plus répandus en électronique sont les brouilleurs qui convertissent un code décimal de position en un code binaire parallèle. C'est ainsi que le codeur peut être indiqué sur le schéma de principe.

Par exemple, imaginons que nous tenions entre nos mains une calculatrice ordinaire, que tout écolier utilise maintenant.

Étant donné que toutes les actions de la calculatrice sont effectuées avec des nombres binaires (rappelez-vous les bases de l'électronique numérique), après le clavier, il y a un encodeur qui convertit les nombres saisis sous forme binaire.

Tous les boutons de la calculatrice sont reliés au fil commun et, en appuyant, par exemple, sur le bouton 5 à l'entrée de l'encodeur, on obtiendra immédiatement la forme binaire de ce nombre à sa sortie.

Bien sûr, l'encodeur de la calculatrice a un plus grand nombre d'entrées, car en plus des nombres, il est nécessaire d'y entrer plus de symboles arithmétiques.Par conséquent, non seulement les nombres sous forme binaire, mais également les commandes sont supprimées des sorties du codeur.

Si l'on considère la structure interne du codeur, alors il est facile de s'assurer qu'il est exécuté sur les éléments logiques de base les plus simples.

Tous les dispositifs de contrôle qui fonctionnent en logique binaire, mais pour la commodité de l'opérateur ont un clavier décimal, utilisent des encodeurs.

Décodeurs.

Les décodeurs appartiennent au même groupe, mais ils fonctionnent exactement le contraire. Ils convertissent le code binaire parallèle en décimal positionnel. La désignation graphique conventionnelle sur le diagramme peut être la suivante.

Ou comme ça.

Si nous parlons plus en détail des décodeurs, alors il faut dire qu'ils peuvent convertir un code binaire en différents systèmes numériques (décimal, hexadécimal, etc.). Tout dépend de l'objectif et de la fonction spécifiques du microcircuit.

L'exemple le plus simple... Vous avez vu plus d'une fois un indicateur numérique à sept segments, par exemple une LED. Il affiche des chiffres décimaux et des nombres auxquels nous nous sommes habitués depuis l'enfance (1, 2, 3, 4 ...). Mais, comme vous le savez, l'électronique numérique fonctionne avec des nombres binaires qui représentent une combinaison de 0 et 1. Qu'est-ce qui a converti le code binaire en décimal et appliqué le résultat à l'affichage numérique à sept segments? Vous avez probablement déjà deviné que le décodeur l'a fait.

Le fonctionnement du décodeur peut être évalué en direct si vous assemblez un circuit simple, qui consiste en un microcircuit de décodeur K176ID2 et un indicateur LED à sept segments, également appelé «huit». Jetez un œil au schéma, il est plus facile de comprendre comment fonctionne le décodeur. Vous pouvez utiliser une maquette sans soudure pour assembler rapidement votre circuit.

Pour référence. Le microcircuit K176ID2 a été développé pour contrôler un indicateur LED à 7 segments. Ce microcircuit est capable de convertir du code binaire à partir de 0000 avant 1001 , qui correspond à des chiffres décimaux de 0 à 9 (une décade). Le reste, les combinaisons plus anciennes ne sont tout simplement pas affichées. Les conclusions C, S, K sont auxiliaires.

Le microcircuit K176ID2 a quatre entrées (1, 2, 4, 8). Ils sont parfois également désignés J0 - D3... Un code binaire parallèle (par exemple 0001) est appliqué à ces entrées. Dans ce cas, le code binaire a 4 bits. Le microcircuit convertit le code de telle sorte qu'aux sorties ( a - g), des signaux apparaissent sous forme de chiffres décimaux et de nombres sur l'affichage à sept segments, auquel nous sommes habitués. Étant donné que le décodeur K176ID2 est capable d'afficher des chiffres décimaux compris entre 0 et 9, nous ne les verrons que sur l'indicateur.

4 interrupteurs à bascule (S1 - S4) sont connectés aux entrées du décodeur K176ID2, à l'aide desquels un code binaire parallèle peut être envoyé au décodeur. Par exemple, lors de la fermeture de l'interrupteur à bascule S1 une unité logique est fournie à la 5ème broche du microcircuit. Si vous ouvrez les contacts de l'interrupteur à bascule S1 - cela correspondra au zéro logique. À l'aide d'interrupteurs à bascule, nous pouvons régler manuellement la logique 1 ou 0 aux entrées du microcircuit.Je pense que tout est clair avec cela.

Le schéma montre comment le code 0101 est envoyé aux entrées du décodeur DD1. L'écran LED affichera le chiffre 5. Si vous fermez uniquement l'interrupteur à bascule S4, l'écran affichera le chiffre 8. Pour écrire un nombre de 0 à 9 dans le code binaire, quatre chiffres suffisent: un 3 * 8 + un 2 * 4 + un 1 * 2 + un 0 * 1où a 0 - a 3, sont des nombres du système numérique (0 ou 1).

Représentons le nombre 0101 sous forme décimale 0101 = 0*8 + 1*4 + 0*2 + 1*1 = 4 + 1 = 5 ... Regardons maintenant le diagramme et voyons que le poids du chiffre correspond au chiffre par lequel 0 ou 1 est multiplié dans la formule.

Un décodeur basé sur la technologie TTL - K155ID1 a été utilisé à un moment donné pour contrôler un indicateur numérique à décharge de gaz des types IN8, IN12, qui étaient très demandés dans les années 70, car les indicateurs LED basse tension étaient encore très rares.

Tout a changé dans les années 80. Il a été possible d'acheter librement des matrices LED à sept segments (indicateurs) et un boom dans l'assemblage d'horloges électroniques balayé parmi les radioamateurs. Les montres électroniques faites maison n'étaient pas assemblées pour la maison uniquement par des paresseux.