Власники патенту RU 2559705:

Винахід відноситься до області обчислювальної техніки, автоматики і може використовуватися в різних цифрових структурах і системах автоматичного управління, Передачі інформації і т.п.

У різних обчислювальних і керуючих системах широко використовуються дешифратори, реалізовані на основі транзисторних-транзисторної і емітерний-зв'язаної логіки, що працюють за законами булевої алгебри і мають по виходу два логічних стану «0» і «1», що характеризуються низьким і високим потенціалами. Класична архітектура дешифратора опублікована в статтях і книгах, серійно випускаються мікросхеми.

Істотний недолік дешифраторів даного класу полягає в тому, що його логічні елементи, використовуючи потенційні виконавчі сигнали, мають багатоярусної структурою, яку неможливо або неефективно використовувати на сучасних низьковольтних техпроцесах, а також нелінійністю робочих режимів елементів і критичністю параметрів структури логічних елементів і вхідних сигналів. В кінцевому підсумку це призводить до зниження швидкодії відомих дешифраторів.

Як пристрої обробки цифрової інформації використовуються також транзисторні каскади перетворення вхідних логічних змінних (струмів), реалізовані на основі струмових дзеркал, що реалізують функцію логічної обробки вхідних струмових змінних.

Істотний недолік відомих схем даного класу полягає в тому, що вони не реалізують функцію перетворення двох вхідних струмових сигналів, що мають чотири стану «00», «01», «10», «11», в чотири вихідних струмових сигналу. Це не дозволяє на його основі створити повний базис засобів обробки сигналів з струмовими змінними, що функціонують на принципах лінійної алгебри.

У роботах, а також монографіях співавтора справжньою заявки показано, що булева алгебра є окремим випадком більш загальної лінійної алгебри, практична реалізаціяякої в структурі обчислювальних і логічних пристроїв автоматики нового покоління вимагає створення спеціальної елементної бази, яка реалізується на основі логіки з двозначним і багатозначним внутрішнім поданням сигналів, в якій еквівалентом стандартного логічного сигналу є квант струму Ι 0. Заявляється пристрій «Дешифратор 2 в 4» ставиться до цього типу логічних пристроїв і працює з вхідними струмовими сигналами і формує вихідний струмовий сигнал.

Найближчим прототипом заявляється пристрою є логічне пристрій «Дешифратор 2 в 4», представлене в патенті US 5742154, що містить перший 1 і другий 2 логічні входи пристрою, перший 3, другий 4, третій 5, четвертий 6 струмові логічні виходи пристрою, перший 7, другий 8 і третій 9 вихідні транзистори, бази яких об'єднані і підключені до першого 10 джерела напруги зсуву, четвертий 11, п'ятий 12 і шостий 13 вихідні транзистори іншого типу провідності, бази яких об'єднані і підключені до другого 14 джерела напруги зсуву, емітер першого 7 вихідного транзистора з'єднаний з емітером четвертого 11 вихідного транзистора, емітер другого 8 вихідного транзистора з'єднаний з емітером п'ятого 12 вихідного транзистора, емітер третього 9 вихідного транзистора з'єднаний з емітером шостого 13 вихідного транзистора, перший 3 струмовий логічний вихід пристрою пов'язаний з колектором першого 7 вихідного транзистора, другий 4 струмовий логічний вихід пристроїв а пов'язаний з колектором третього 9 вихідного транзистора, колектор четвертого 11 вихідного транзистора пов'язаний з третім 5 струмовим логічним виходом пристрою, колектор шостого 13 вихідного транзистора пов'язаний з четвертим 6 струмовим логічним виходом пристрою, перше 15 і друге 16 струмові дзеркала, узгоджені з першої 17 шиною джерела живлення, третє 18 струмове дзеркало, узгоджене з другої 19 шиною джерела живлення, допоміжне джерело опорного струму 20.

Основне завдання пропонованого винаходу полягає в створенні логічного елемента, що забезпечує дешифрацию стану двох вхідних логічних змінних і формування в струмового формі чотирьох вихідних сигналів. В кінцевому підсумку це дозволяє підвищити швидкодію відомих пристроїв перетворення інформації з використанням заявляється дешифратора і створити елементну базуобчислювальних пристроїв, що працюють на принципах багатозначною лінійної алгебри.

Поставлена задача вирішується тим, що в логічному пристрої «Дешифратор 2 в 4» (фіг. 1), що містить перший 1 і другий 2 логічні входи пристрою, перший 3, другий 4, третій 5, четвертий 6 струмові логічні виходи пристрою, перший 7, другий 8 і третій 9 вихідні транзистори, бази яких об'єднані і підключені до першого 10 джерела напруги зсуву, четвертий 11, п'ятий 12 і шостий 13 вихідні транзистори іншого типу провідності, бази яких об'єднані і підключені до другого 14 джерела напруги зсуву, емітер першого 7 вихідного транзистора з'єднаний з емітером четвертого І вихідного транзистора, емітер другого 8 вихідного транзистора з'єднаний з емітером п'ятого 12 вихідного транзистора, емітер третього 9 вихідного транзистора з'єднаний з емітером шостого 13 вихідного транзистора, перший 3 струмовий логічний вихід пристрою пов'язаний з колектором першого 7 вихідного транзистора, другий 4 струмовий логічний вихід пристрою пов'язаний з колектором третього 9 виходног про транзистора, колектор четвертого 11 вихідного транзистора пов'язаний з третім 5 струмовим логічним виходом пристрою, колектор шостого 13 вихідного транзистора пов'язаний з четвертим 6 струмовим логічним виходом пристрою, перше 15 і друге 16 струмові дзеркала, узгоджені з першої 17 шиною джерела живлення, третє 18 струмове дзеркало, узгоджене з другої 19 шиною джерела живлення, допоміжне джерело опорного струму 20, передбачені нові елементи і зв'язку - перший 1 логічний вхід пристрою пов'язаний зі входом третього 18 струмового дзеркала, другий 2 логічний вхід пристрою з'єднаний зі входом першого 15 струмового дзеркала, перший 21 струмовий вихід першого 15 струмового дзеркала з'єднаний з об'єднаними емітерами другого 8 і п'ятого 12 вихідних транзисторів і через допоміжне джерело опорного струму 20 пов'язаний з другої 19 шиною джерела живлення, другий 22 струмовий вихід першого 15 струмового дзеркала з'єднаний з об'єднаними емітерами першого 7 і четвертого 11 вихідних транзистор ів і підключений до першого 23 токовому виходу третього 18 струмового дзеркала, колектор другого 8 вихідного транзистора пов'язаний зі входом другого 16 струмового дзеркала, струмовий вихід якого підключений до об'єднаних емітерів третього 9 і шостого 13 вихідних транзисторів і пов'язаний з другим 24 струмовим виходом третього 18 токового дзеркала, причому колектор п'ятого 12 вихідного транзистора пов'язаний з другої 19 шиною джерела живлення.

Схема логічного пристрою-прототипу показана на фіг. 1. На фіг. 2 представлена схема заявляється пристрою відповідно до п. 1 формули винаходу.

На фіг. 3 представлена схема заявляється пристрою відповідно до п. 2, п. 3, п. 4 формули винаходу.

На фіг. 4 приведена принципова схемафіг. 3 в середовищі комп'ютерного моделюванняМС9 з конкретним виконанням основних функціональних вузлів (струмових дзеркал, джерел опорного струму).

На фіг. 5 представлені результати комп'ютерного моделювання схеми фіг. 4.

Логічне пристрій «Дешифратор 2 на 4» фіг. 2 містить перший 1 і другий 2 логічні входи пристрою, перший 3, другий 4, третій 5, четвертий 6 струмові логічні виходи пристрою, перший 7, другий 8 і третій 9 вихідні транзистори, бази яких об'єднані і підключені до першого 10 джерела напруги зсуву, четвертий 11, п'ятий 12 і шостий 13 вихідні транзистори іншого типу провідності, бази яких об'єднані і підключені до другого 14 джерела напруги зсуву, емітер першого 7 вихідного транзистора з'єднаний з емітером четвертого 11 вихідного транзистора, емітер другого 8 вихідного транзистора з'єднаний з емітером п'ятого 12 вихідного транзистора, емітер третього 9 вихідного транзистора з'єднаний з емітером шостого 13 вихідного транзистора, перший 3 струмовий логічний вихід пристрою пов'язаний з колектором першого 7 вихідного транзистора, другий 4 струмовий логічний вихід пристрою пов'язаний з колектором третього 9 вихідного транзистора, колектор четвертого 11 вихідного транзистора пов'язаний з третім 5 струмовим ло гическим виходом пристрою, колектор шостого 13 вихідного транзистора пов'язаний з четвертим 6 струмовим логічним виходом пристрою, перше 15 і друге 16 струмові дзеркала, узгоджені з першої 17 шиною джерела живлення, третє 18 струмове дзеркало, узгоджене з другої 19 шиною джерела живлення, допоміжне джерело опорного струму 20. перший 1 логічний вхід пристрою пов'язаний зі входом третього 18 струмового дзеркала, другий 2 логічний вхід пристрою з'єднаний зі входом першого 15 струмового дзеркала, перший 21 струмовий вихід першого 15 струмового дзеркала з'єднаний з об'єднаними емітерами другого 8 і п'ятого 12 вихідних транзисторів і через допоміжне джерело опорного струму 20 пов'язаний з другої 19 шиною джерела живлення, другий 22 струмовий вихід першого 15 струмового дзеркала з'єднаний з об'єднаними емітерами першого 7 і четвертого 11 вихідних транзисторів і підключений до першого 23 токовому виходу третього 18 струмового дзеркала, колектор другого 8 вихідного транзистора пов'язаний зі вхо будинок другого 16 струмового дзеркала, струмовий вихід якого підключений до об'єднаних емітерів третього 9 і шостого 13 вихідних транзисторів і пов'язаний з другим 24 струмовим виходом третього 18 струмового дзеркала, причому колектор п'ятого 12 вихідного транзистора пов'язаний з другої 19 шиною джерела живлення.

На фіг. 3 відповідно до п. 2 формули винаходу перший 1 логічний вхід пристрою пов'язаний зі входом третього 18 струмового дзеркала через перший додатковий інвертується каскад, виконаний у вигляді першого 26 додаткового струмового дзеркала, узгодженого з першої 17 шиною джерела живлення.

На фіг. 3 відповідно до п. 3 формули винаходу колектор четвертого 11 вихідного транзистора пов'язаний з третім 5 струмовим логічним виходом пристрою через другий додатковий інвертується каскад, виконаний у вигляді другого 27 додаткового струмового дзеркала, узгодженого з другої 19 шиною джерела живлення.

Крім цього, на фіг. 3 відповідно до п. 4 формули винаходу колектор шостого 13 вихідного транзистора пов'язаний з четвертим 6 струмовим логічним виходом пристрою через третій додатковий інвертується каскад, виконаний у вигляді третього 28 додаткового струмового дзеркала, узгодженого з другої 19 шиною джерела живлення.

Розглянемо роботу пропонованої схеми дешифратора з струмовими входами і виходами фіг. 2.

Дешифратор 2 в 4 реалізує відомі функції:

де А 0, A ¯ 0 - прямий і інверсний сигнали на вході 1 пристрою фіг. 2,

A 1, A ¯ 1 - прямий і інверсний сигнали на вході 2 пристрої фіг. 2.

Особливістю їх реалізації в лінійної алгебри є використання для цієї мети операції усіченої різниці:

таблиця істинності якої наведена нижче

З таблиці випливає, що з чотирьох можливих поєднань значень вхідних змінних середнє арифметичне значення функції відповідає тільки одному поєднанню, відповідному умові А 0> А 1. Ставлячи в таблицю істинності прямі і інверсні вхідні змінні, можна отримати середнє арифметичне значення функції, що відповідає кожному з можливих поєднань значень вхідних змінних.

Застосування цієї операції призводить до наступного поданням логічних функцій дешифратора:

Реалізація цих операцій проводиться таким чином.

Сигнали вхідних змінних А 0 і А 1 через логічні входи 1 і 2 надходять на перше 15 і третє 18 струмові дзеркала, за допомогою яких відбувається розмноження зазначених сигналів і зміна їх знака. При цьому сигнал А 0 передається у вигляді випливає струму (тобто у вигляді А 0) і за допомогою третього струмового дзеркала 18 перетворюється на впадає струм (тобто до виду -А 0), а А 1 надходить в прямій формі у вигляді впадає струму (тобто у вигляді -A 1) і за допомогою першого струмового дзеркала 15 перетворюється в витікаючий струм (тобто до виду А 1).

У точці з'єднання виходів 22 першого струмового дзеркала 15 і 23 третього струмового дзеркала 18 реалізується операція А 1 -A 0. Різницевий сигнал подається на об'єднані емітери транзисторів 7 і 11, режими роботи яких задаються першим 10 і другим 14 джерелами напруги зсуву.

Якщо різницевий сигнал позитивний, тобто А 0 -А 1> 0, транзистор 7 закритий, а транзистор 11 відкритий і на вихід 5 видається квант впадає струму, відповідний - (A 0 -А 1) = А 1 -A 0, який реалізує вираз (2). При будь-яких інших сполученнях значень квантів струму на виході 5 ток буде відсутній.

Якщо ж А 0 -А 1 ≤0, то транзистор 7 відкритий, а транзистор 11 закритий і на вихід 3 видається квант випливає струму, відповідний А 0 -А 1, який реалізує вираз (3). При будь-яких інших сполученнях значень квантів струму на виході 3 струм буде відсутній.

У точці з'єднання виходу 21 першого струмового дзеркала і допоміжне джерело опорного струму 20 виробляється віднімання А 1 -1. Різницевий сигнал подається на об'єднані емітери транзисторів 8 і 12, режими роботи яких задаються першим 10 і другим 14 джерелами напруги зсуву. Якщо різницевий сигнал позитивний, тобто А 1 -1> 0, транзистор 8 закритий, а транзистор 12 відкритий. Якщо різницевий сигнал менше або дорівнює нулю, то транзистор 8 відкритий, а транзистор 12 закритий.

У першому випадку сигнал через транзистор 12 замикається на «землю». У другому випадку квант випливає разностного струму A 1 -1 за допомогою третього струмового дзеркала 16 перетворюється в квант випливає струму 1-A 1 і з нього віднімається впадає квант струму -A 0. Різницевий сигнал подається на об'єднані емітери транзисторів 9 і 13, режими роботи яких задаються першим 10 і другим 14 джерелами напруги зсуву. Якщо різницевий сигнал позитивний, тобто транзистор 9 закритий, а транзистор 13 відкритий. При цьому на вихід 6 видається різницевий сигнал (1-A 1) -A 0, у вигляді випливає кванта струму, який реалізує вираз (4). При будь-яких інших сполученнях значень квантів струму на виході 4 ток буде відсутній.

специфікою даного пристроює уявлення вихідних сигналів у вигляді квантів впадає (на виходах 3 і 4) і що випливає (на виходах 5 і 6) струму. Для випадку, коли необхідні всі вихідні сигнали одного напрямку, може використовуватися схема дешифратора, наведена на фіг. 3. Її відмінністю від схеми на фіг. 2 є використання двох додаткових струмових дзеркал 27 і 28, до входів яких підключені колектори транзисторів 11 і 13, а виходи є виходами 5 і 6 дешифратора. В результаті всі вихідні сигнали представлені квантами впадає струму.

Як видно з наведеного опису, реалізація пристрою «Дешифратор 2 в 4» проводиться у вигляді стандартних логічних функцій за законами лінійної алгебри шляхом формуванням різниці квантів струму 10. Реалізація елементів на струмових дзеркалах дозволяє в багатьох випадках знизити напругу живлення, а так як всі елементи наведеної схеми працюють в активному режимі, який передбачає відсутність насичення в процесі перемикань, підвищується загальну швидкодію пристрою. Використання стабільних значень квантів струму I 0, а також визначення вихідного сигналу різницею цих струмів забезпечує малу залежність функціонування схеми від зовнішніх дестабілізуючих факторів (девіація напруги живлення, радіаційне і температурне впливу, синфазна перешкода і ін.).

Показання на фіг. 9, фіг. 10 результати моделювання підтверджують зазначені властивості заявлених схем.

Таким чином, розглянуті схемотехнічні рішення логічного пристрою «Дешифратор 2 в 4» характеризуються двійковим струмовим поданням сигналу і можуть бути покладені в основу обчислювальних і керуючих пристроїв, що використовують лінійну алгебру, окремим випадком якої є булева алгебра.

БІБЛІОГРАФІЯ

1. Патент US 6243319 В1, fig. 13.

2. Патент US 5604712 А.

3. Патент US 4514829 А.

4. Патент US 20120020179 A1.

5. Патент US 6920078 В2.

6. Патент US 6324117 В1, fig. 3.

7. Патентна заявка US 20040018019 A1.

8. Патент US 5568061 А.

9. Патент US 5148480 A, fig. 4.

10. Brzozowski I., Zachara L., Kos A. Universal design method of n-to-2n decoders // Mixed Design of Integrated Circuits and Systems (MIXDES), 2013 Proceedings of the 20th International Conference, 2013. - C. 279 -284, Fig. 1.

11. Subramanyam M.V. Switching Theory and Logic Design / Firewall Media, 2011. Second, - 783 c, Fig. 3.174.

12. SN74LVC1G139 2-to-4 Line Decoder [Електронний ресурс]. URL: http://www.ti.com/lit/ds/symlink/sn741vc1g139.pdf.

13. Патент US 8159304, fig. 5.

14. Патент US №5977829, fig. 1.

15. Патент US №5789982, fig. 2.

16. Патент US №5140282.

17. Патент US №6624701, fig. 4.

18. Патент US №6529078.

19. Патент US №5734294.

20. Патент US №5557220.

21. Патент US №6624701.

22. Патент RU №2319296.

23. Патент RU №2436224.

24. Патент RU №2319296.

25. Патент RU №2321157.

26. Патент US 6556075, fig. 2.

27. Патент US 6556075, fig. 6.

28. Chernov N.I., Yugai V.Y., Prokopenko N.N., і ін. Basic Concept of Linear Synthesis of Multi-Valued Digital Structures in Linear Spaces // 11th East-West Design & Test Symposium (EWDTS 2013). - Rostov-on-Don, 2013. - C. 146-149.

29. Малюгин В.Д. Реалізація булевих функцій арифметичними поліномами // Автоматика і телемеханіка, 1982. №4. С. 84-93.

30. Чернов Н.І. Основи теорії логічного синтезу цифрових структур над полем дійсних чисел // Монографія. - Таганрог: ТРТУ, 2001. - 147 с.

31. Чернов Н.І. Лінійний синтез цифрових структур АСОИУ »// Навчальний посібник. - Таганрог: ТРТУ, 2004 г. - 118 с.

1. Дешифратор 2 на 4, що містить перший (1) і другий (2) логічні входи пристрою, перший (3), другий (4), третій (5), четвертий (6) струмові логічні виходи пристрою, перший (7), другий (8) і третій (9) вихідні транзистори, бази яких об'єднані і підключені до першого (10) джерела напруги зсуву, четвертий (11), п'ятий (12) і шостий (13) вихідні транзистори іншого типу провідності, бази яких об'єднані і підключені до другого (14) джерела напруги зсуву, емітер першого (7) вихідного транзистора з'єднаний з емітером четвертого (11) вихідного транзистора, емітер другого (8) вихідного транзистора з'єднаний з емітером п'ятого (12) вихідного транзистора, емітер третього (9) вихідного транзистора з'єднаний з емітером шостого (13) вихідного транзистора, перший (3) струмовий логічний вихід пристрою пов'язаний з колектором першого (7) вихідного транзистора, другий (4) струмовий логічний вихід пристрою пов'язаний з колектором третього (9) вихідного транзистора, колле ктор четвертого (11) вихідного транзистора пов'язаний з третім (5) струмовим логічним виходом пристрою, колектор шостого (13) вихідного транзистора пов'язаний з четвертим (6) струмовим логічним виходом пристрою, перше (15) і друге (16) струмові дзеркала, узгоджені з першій (17) шиною джерела живлення, третє (18) струмове дзеркало, узгоджене з другої (19) шиною джерела живлення, допоміжне джерело опорного струму (20), який відрізняється тим, що перший (1) логічний вхід пристрою пов'язаний зі входом третього (18 ) струмового дзеркала, другий (2) логічний вхід пристрою з'єднаний зі входом першого (15) струмового дзеркала, перший (21) струмовий вихід першого (15) струмового дзеркала з'єднаний з об'єднаними емітерами другого (8) і п'ятого (12) вихідних транзисторів і через допоміжне джерело опорного струму (20) пов'язаний з другої (19) шиною джерела живлення, другий (22) струмовий вихід першого (15) струмового дзеркала з'єднаний з об'єднаними емітерами першого (7) і четвертого (11) вихідних транзисторів і підключений до першого (23) токовому виходу третього (18) струмового дзеркала, колектор другого (8) вихідного транзистора пов'язаний зі входом другого (16) струмового дзеркала, струмовий вихід якого підключений до об'єднаних емітерів третього (9) і шостого (13) вихідних транзисторів і пов'язаний з другим (24) струмовим виходом третього (18) струмового дзеркала, причому колектор п'ятого (12) вихідного транзистора пов'язаний з другої (19) шиною джерела живлення.

2. Дешифратор 2 на 4 по п. 1, який відрізняється тим, що перший (1) логічний вхід пристрою пов'язаний зі входом третього (18) струмового дзеркала через перший додатковий інвертується каскад, виконаний у вигляді першого (26) додаткового струмового дзеркала, узгодженого з першій (17) шиною джерела живлення.

3. Дешифратор 2 на 4 по п. 1, який відрізняється тим, що колектор четвертого (11) вихідного транзистора пов'язаний з третім (5) струмовим логічним виходом пристрою через другий додатковий інвертується каскад, виконаний у вигляді другого (27) додаткового струмового дзеркала, узгодженого з другої (19) шиною джерела живлення.

4. Дешифратор 2 на 4 по п. 1, який відрізняється тим, що колектор шостого (13) вихідного транзистора пов'язаний з четвертим (6) струмовим логічним виходом пристрою через третій додатковий інвертується каскад, виконаний у вигляді третього (28) додаткового струмового дзеркала, узгодженого з другої (19) шиною джерела живлення.

Схожі патенти:

Винахід відноситься до засобів кодування з використанням скороченою кодової книги з адаптивної установкоюв початкове положення. Технічний результат полягає в зниженні обсягу інформації, що передається від приймальної сторони передавальної стороні.

Винахід відноситься до обчислювальної техніки, А саме до кодування відеоінформації. Технічний результат полягає в підвищення ефективності кодування і декодування бітового потоку відеоінформації за рахунок поділу даних на ентропійних шари.

Винахід відноситься до способу кодування послідовності цілих чисел, до пристрою зберігання і до сигналу, переносящему таку кодовану послідовність, а також до способу декодування цієї кодованої послідовності.

Винахід відноситься до способу попереднього кодування, а також до системи і способу побудови кодової книги попереднього кодування в системі з багатьма входами і багатьма виходами (MIMO).

Винахід відноситься до області техніки, в якій використовуються оцифровані сигнали, і може бути застосований в пристроях зв'язку, реєстрації, записи, відтворення, перетворення, кодування і стиснення сигналів, системах автоматичного управління.

Винахід відноситься до області електрозв'язку, а саме до області криптографічних пристроїв і способів перевірки електронної цифрового підпису(ЕЦП). .

Винахід відноситься до області обробки цифрових сигналів, зокрема до стиснення даних і поліпшення ентропійного кодування видеопоследовательностей. Технічним результатом є підвищення ефективності і зниження обчислювальної складностіентропійного кодування. Спосіб обробки потоку даних, що складається з безлічі синтаксичних елементів, заснований на заміні синтаксичних елементів, значення яких мають високу ймовірність появи, синтаксичними елементами, значення яких мають низьку ймовірність. Визначають для синтаксичного елемента контекст і обчислюють ймовірність появи значень тих синтаксичних елементів в моделі потоку даних, які мають певний контекст. Замінюють синтаксичні елементи потоку даних, що мають певний контекст, якщо обчислена ймовірність появи значення синтаксичного елементу вище заданого порогу, на синтаксичні елементи, значення яких мають низьку ймовірність. 3 н. і 10 з.п. ф-ли, 4 іл., 2 табл.

Винахід відноситься до техніки зв'язку і призначений для вимірювання спектра інформаційних акустичних сигналів. Технічний результат - підвищення точності вимірювання спектра інформаційних акустичних сигналів, розширення функціональних можливостейпристрою за рахунок прив'язки миттєвих значень спектра до регульованих по тривалості відрізків тимчасового акустичного сигналу. Для цього в способі вимірювання спектра використовують дискретно-косинусное перетворення (ДКП) замість швидкого перетворення Фур'є (ШПФ), що дозволяє підвищити точність вимірювання спектра акустичних сигналів за рахунок збільшення роздільної здатності, зменшення в спектрі рівня бічних пелюсток перетворення вікна і зменшення осциляції оцінки амплітуди спектральних складових, а також дозволяє зменшити тривалість відрізків акустичного сигналу, на яких вимірюється миттєвий спектр, при цьому здійснюється формування замість одного двох сигналів (основного і додаткового), причому додатковий цифровий акустичний сигнал є ортогональним по відношенню до основного, здійснюється також прив'язка вимірюваних миттєвих значень спектра , модуля спектра і фазочастотной характеристики сигналу до регульованим за тимчасовим положенням і за тривалістю відрізків тимчасового акустичного сигналу, на яких цей спектр вимірюється. 2 н.п. ф-ли, 8 мул.

Винахід відноситься до бездротового зв'язку. Технічний результат - підвищення завадостійкості, надійності і ефективності зв'язку, тоді як споживання енергії може бути знижено. Для цього спосіб включає: етап S1, на якому головний пристрій генерує код послідовності за допомогою специфічного кодера і передає код послідовності кожного підлеглого пристрою безперервно протягом заданого періоду часу згідно із запитом зв'язку, причому специфічний кодер є регістром зсуву з зворотним зв'язком, Виконаним по конкретному многочлену, порядок і коефіцієнти якого співвіднесені із запитом зв'язку, тоді як всі коефіцієнти і початкові значеннянерівні 0 в один і той же час; заданий період часу більше суми періоду сну і періоду виявлення підлеглого пристрою або дорівнює їй, що становить цикл сну і приведення в робочий стан; етап S2, на якому підлеглий пристрій приймає безперервну частину коду послідовності в період виявлення, декодує код послідовності за допомогою декодера, відповідного кодеру, і виконує відповідну операцію згідно результату декодування. 2 н. і 10 з.п. ф-ли, 5 мул.

Винахід відноситься до техніки зв'язку і призначений для кодування і декодування сигналів. Технічний результат - підвищення точності кодування і декодування сигналів. Спосіб кодування сигналів включає в себе отримання сигналу частотної області згідно вхідного сигналу; виділення попередньо визначених бітів сигналу частотної області згідно з попередньо визначеним правилом виділення; регулювання виділення бітів для сигналу частотної області, коли найбільша частота сигналу частотної області, яким виділяються біти, перевищує попередньо певне значення; і кодування сигналу частотної області згідно виділенню бітів для сигналу частотної області. 4 н. і 16 з.п. ф-ли, 9 мул.

Винахід відноситься до області телекомунікацій і призначене для захисту переданої секретної інформації. Технічний результат - високий рівень захищеності зашифрованої інформації. Спосіб шифрування інформації, що включає побудову таблиці відповідностей символів і їх еквівалентів в просторі (00; FF) в шестерічной системі числення, генерування нової таблицівідповідностей шляхом зміни оригінальної таблиці, здійснюючи зрушення таблиці оригіналу, тобто на вказане число символів зсувається рядок відповідностей, кодування вихідної інформації і стиснення її до бажаного обсягу з використанням відповідної таблиці кодування Unicode. 2 табл.

Винахід відноситься до кодування / декодування цифрового сигналу, що складається з послідовних блоків вибірок. Технічний результат полягає в підвищенні якості кодованого звуку. Кодування містить застосування взвешивающего вікна для двох блоків з М послідовних вибірок. Зокрема, таке зважувальне вікно є асиметричним і містить чотири окремих ділянки, Що тривають послідовно за двома згаданими вище блокам, при цьому перша ділянка зростає протягом першого часового інтервалу, другий ділянку має постійне зважувальне значення протягом другого часового інтервалу, третя ділянка зменшується з плином третього часового інтервалу і четвертий ділянка має постійне зважувальне значення протягом четвертого тимчасового інтервалу. 6 н. і 11 з.п. ф-ли, 10 іл.

Винахід відноситься до області цифрової обробки сигналів, зокрема до способів кодування-декодування цифрових відеозображень. Технічним результатом є підвищення коефіцієнта компресії відеозображень при незначному зниженні якості декодованого зображення стосовно до зображень, які мають високочастотний характер спектра сигналу. Запропоновано спосіб кодування-декодування цифрових відеозображень. Згідно способу в процесі кодування до низькочастотного компоненту вейвлет-перетворення для згладжування вихідної функції через підрядник підмішують додатковий високочастотний компонент, який використовують для кодування, але пригнічують на стороні декодування за допомогою використання фільтра нижніх частот. Причому кодування реалізують при використанні функціоналу з двома цілями підвищення коефіцієнта компресії даних і збереження якості декодіруемой зображення, а характеристики фільтра декодера враховують як обмеження зв'язку на стадії кодування. 8 мул., 3 табл.

Винахід відноситься до області техніки бездротового зв'язку. Технічний результат - підвищення якості зв'язку за рахунок придушення послідовних перешкод між потоками сигналів. Спосіб попереднього кодування включає в себе: виконання попередньої обробки попереднього кодування для сигналу, який повинен передаватися, причому попередня обробка викликає збільшення потужності сигналу, який повинен передаватися; вибір алгоритму обмеження потужності згідно з правилом вибору; виконання операції обмеження потужності для попередньо обробленого сигналу відповідно до обраного алгоритму обмеження потужності; і формування попередньо кодованого сигналу відповідно до сигналу з обмеженою потужністю. Варіант здійснення даного винаходу додатково розкриває передавальний пристрій, приймальний пристрій і систему попереднього кодування. Даний винахід несприятливий вплив, який чиниться за допомогою операції обмеження потужності на передачу сигналів, може зменшуватися в міру можливості в той час, коли потужність передачі обмежена за допомогою використання операції обмеження потужності. 5 н. і 12 з.п. ф-ли, 8 мул.

Винахід стосується області кодування і декодування і призначене для квантування векторів огинають частот. Технічний результат - підвищення ефективності квантування векторів огинають частот. Спосіб включає в себе: поділ N огинають частот в одному кадрі на N1 векторів, де кожен вектор в N1 векторах включає в себе M огинають частот; квантування першого вектора в N1 векторах за допомогою використання першої кодової книги для отримання кодового слова, відповідного квантованим першому вектору, де згадана перша кодова книга поділяється на 2B1 ділянок; визначення згідно кодовим словом, відповідному квантованим першому вектору, що квантований перший вектор асоціюється з iим ділянкою в 2B1 ділянках згаданої першої кодової книги; визначення другої кодової книги згідно кодової книзі Iго ділянки; і квантування другого вектора в N1 векторах на основі згаданої другої кодової книги. У варіантах здійснення даного винаходу огинають частот поділяються на безліч векторів з меншими розмірами, так що квантування векторів може бути виконано в відношенні векторів огинають частот за допомогою використання кодової книги з меншою кількістю бітів. 2 н. і 6 з.п. ф-ли, 3 мул.

Група винаходів відноситься до області кодування. Технічним результатом є підвищення ефективності стиснення даних. Спосіб кодування вхідних даних (D1) включає визначення по суті повторюваних блоків даних і / або пакетів даних щонайменше в одному з фрагментів вхідних даних (D1), при цьому блоки даних і / або пакети даних включають відповідне безліч елементів, де елементи включають безліч бітів; визначення, чи є елементи незмінними всередині по суті повторюваних блоків даних і / або пакетів даних, і / або визначення, що елементи всередині по суті повторюваних блоків даних і / або пакетів даних змінюються; кодування незмінних елементів в кодовані дані (Е2) з використанням щонайменше одного відповідного символу або щонайменше одного відповідного біта, що вказує на відсутність змін в незмінних елементах в порівнянні з відповідними їм елементами в опорному блоці даних і / або пакеті даних; і кодування змінених елементів в кодовані дані (Е2). 6 н. і 28 з.п. ф-ли, 8 мул.

Винахід відноситься до дешифратора. Технічний результат полягає в підвищенні швидкодії пристроїв перетворення інформації з використанням заявляється дешифратора. Перший логічний вхід пристрою пов'язаний зі входом третього струмового дзеркала, другий логічний вхід пристрою з'єднаний зі входом першого струмового дзеркала, перший струмовий вихід першого струмового дзеркала з'єднаний з об'єднаними емітерами другого і п'ятого вихідних транзисторів і через допоміжне джерело опорного струму пов'язаний з другої шиною джерела живлення, другий струмовий вихід першого струмового дзеркала з'єднаний з об'єднаними емітерами першого і четвертого вихідних транзисторів і підключений до першого токовому виходу третього струмового дзеркала, колектор другого вихідного транзистора пов'язаний зі входом другого струмового дзеркала, струмовий вихід якого підключений до об'єднаних емітерів третього і шостого вихідних транзисторів і пов'язаний з другим струмовим виходом третього струмового дзеркала, причому колектор п'ятого вихідного транзистора пов'язаний з другої шиною джерела живлення. 3 з.п. ф-ли, 5 мул.

3. Функціональна схема, умовне графічне позначення і таблиця істинності повного дешифратора на 3 входи.

4. Лінійні дешифратори: перемикальна функція, УДО та схема.

5. Пірамідальні дешифратори: перемикальна функція, УДО та схема.

6. Багатоступеневі дешифратори прямокутного типу: перемикальна функція, УДО та схема.

7. Тактируемого і дешифратори інтегрального виконання.

дешифратор - це комбінаційний операційний вузол, що перетворює вхідний слово в сигнал на одному з його виходів.

Таким чином, дешифратором називається вузол, в якому кожної комбінації вхідних сигналів відповідає наявність сигналу на одному з виходів.

На рис.4 представлена функціональна схема дешифратора, що має n входів і 2 n -1 виходів.

Методика синтезу дешифраторів

Умови роботи дешифратора на два входи можна уявити таблицею істинності (табл.3). Кількість виходів такого дешифратора m = 2 + 2 = 4.

|

Таблиця 3 |

||||||||||||||||||||||||||||||||||||

|

Таблиця істинності дешифратора 2 × 4

|

||||||||||||||||||||||||||||||||||||

Переключательние функції для виходів дешифратора згідно цієї таблиці істинності запишуться в такий спосіб:

Перетворимо вираження (4) для реалізації в базисі І-НЕ:

Умовні зображення дешифратора, що застосовуються при побудові функціональних схем, Показані на рис.7, де а - загальне позначення дешифратора; б - позначення матричного дешифратора. Входи дешифратора позначаються десятковими числами, які зображують виконавчі ваги, виходи - десятковими зображеннями відповідних кодових комбінацій.

Позначення дешифраторів: 155 ВД 1, 555ВД 6 і т.д.

3. Аналіз роботи шифраторів

Призначення і принцип дії шифраторів.

Розгляд питання здійснюється шляхом опитування учнів з місць і біля дошки у відповідності з наступним планом:

· Призначення

· Таблиця істинності

· Способи синтезу схем

· Приклади найпростіших схем

Питання розглядаються з учнями

шифратори:

1. Призначення, логіка функціонування і класифікація шифраторів.

2. Функціональна схема, умовне графічне позначення і таблиця істинності шифратора на n входів.

3. Функціональна схема, умовне графічне позначення і таблиця істинності шифратора на 4 входи.

4. Синтез шифраторів в різних базисах.

5. Принципи побудови пріоритетних шифраторів.

шифратор являє собою функціональний вузол цифрової ЕОМ і призначений для перетворення унітарної коду (код, в якому лише одна змінна приймає одиничне значення) в деякий (двійковий) позиційний код.

Іншими словами, шифратор виконує функції, зворотні функціям дешифратора.

Повний шифратор має 2 m входів і m виходів. При цьому, якщо подано вхідний сигнал на одну з вхідних ланцюгів шифратора, то на його виходах формується слово, що відповідає номеру збудженої ланцюга.

Синтез рівнозначного шифратора

Нехай m = 2, тоді число входів шифратора дорівнює чотирьом. Таблиця функціонування такого шифратора матиме такий вигляд (табл.4).

|

Таблиця 4 |

||||||||||||||||||||||||||||||

|

Таблиця станів шифратора 4 × 2

Синтез пріоритетного шифратора Розглянемо принцип функціонування шифратора «4 × 2 ». Таблиця істинності для даного шифратора представлена в табл. 5. З таблиці видно, що при побудові пріоритетного шифратора використовуються 1,2.4 і 8 набори, для інших наборів функція набуває байдуже значення - Ф. | ||||||||||||||||||||||||||||||

.

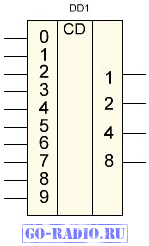

Мікросхема К176ІД1, К561ІД1

Неповний двійковій-десятковий дешифратор має 4 входи для прийому двійкового коду і 10 виходів його десяткового еквівалента.

Активний рівень і входу і виходу - високий. При подачі на мікросхему двійкового коду в діапазоні 8-15 на всіх виходах встановлюється низький логічний рівень (дешифрування не проводиться). Додаткових входів для стробування мікросхема не має, проте, розширення розрядності нескладно реалізувати, якщо пожертвувати двома останніми десятковими розрядами:

У наведеній схемі в якості стробирующего сигналу для DD2 використовується інвертований старший розряд вхідного коду. При цьому висновки 4,5 (старші десяткові розряди 8,9) мікросхем не використовуються, а схема являє собою повний двійковій-десятковий дешифратор на 4 біта.

На наступному малюнку за рахунок використання окремої мікросхеми для керування дешифраторами число виходів збільшено до 64 (6-ти байтний вхідний код).

——————————————-

мікросхема К176ІД2

Дешифратор-перетворювач. Призначений для перетворення двійкового коду в код для семисегментний індикатора. Ланцюгів для управління десятковою крапкою в мікросхемі не передбачено. Крім власне дешифратора мікросхема має тригер-засувку, що дозволяє запам'ятовувати поточні дані.

Має чотирьохрозрядний вхід даних і сім виходів для підключення семисегментного цифрового індикатора. Активні рівні входу і виходу високі, але при необхідності можуть інвертуватися сигналом по службового входу S. При низькому рівні на цьому вході активний вихідний сигнал високий, при «1» на S - низький. Це дозволяє підключати цифрові матриці як із загальним анодом, так і з загальним катодом без додаткових інверторів. Ще один службовий вхід До служить для управлінням матриці. «0» на вході До дозволяє відображення, «1» гасить матрицю.

І третій службовий вхід С служить для замикання інформації, що надходить на вхід дешифратора. При високому рівні на С сигнал негайно дешифрується і подається на індикатор. При зміні його на «0» вхідний код замикається і відображається незалежно від змін на вході до тих пір, поки рівень на вході С знову не стане високим. Запам'ятовування відбувається по спаду високого рівня.

Вихідні ключі мікросхеми К176ІД2 в змозі витримувати струми короткого замикання чисельно рівні рівню напруги живлення (в мА) і тому можуть бути навантажені безпосередньо на світлодіодні індикатори (наприклад, АЛ305, АЛС324, АЛС321) без додаткових підсилювачів струму.

мікросхема К176ІДЗ

Повний аналог К176ІД2 по розташуванню висновків і алгоритму роботи. Відмінність полягає в вихідних ключах, виконаних за схемою з відкритим стоком. Це дозволяє безпосередньо підключати до виходу дешифратора аноди люмінесцентних індикаторів, що вимагають для свого харчування щодо високої напруги (до 15 В). При використанні мікросхеми спільно з такими індикаторами на службовий вхід S потрібно подати лог. «0».

——————————————-

мікросхема 564ІД4

Дешифратор-перетворювач. Призначений для перетворення двійкового коду в код для семисегментного (в тому числі і РК) індикатора. Ланцюгів для управління десятковою крапкою немає.

Основна відмінність від К176ІД2 - наявність третього виведення для харчування вихідних ключів, які витримують напругу до 15 В. Для протівофазного харчування РКІ існує спеціальний підсилювач (вхід S, вихід Р). Розглянемо його роботу докладніше на прикладі підключення РК індикатора ІЖКЦ1-1 / 18.

Основна відмінність від К176ІД2 - наявність третього виведення для харчування вихідних ключів, які витримують напругу до 15 В. Для протівофазного харчування РКІ існує спеціальний підсилювач (вхід S, вихід Р). Розглянемо його роботу докладніше на прикладі підключення РК індикатора ІЖКЦ1-1 / 18.

Припустимо, сам дешифратор як і всі попередні вузли приладу харчується напругою 5 В (вивод16), а ЖК індикатору потрібно змінна напругаамплітудою 15 В. Для організації харчування РКІ чинимо так: на висновок 7 подаємо 15 В (третій висновок харчування), а на вивід 6 (вхід S) сигнал рівня ТТЛ (5 В) і частотою 100 Гц. Цей сигнал проходить до висновку 1 (висновок Р) без інверсії, але амплітуда його збільшується до напруги 15 В.

Припустимо, сам дешифратор як і всі попередні вузли приладу харчується напругою 5 В (вивод16), а ЖК індикатору потрібно змінна напругаамплітудою 15 В. Для організації харчування РКІ чинимо так: на висновок 7 подаємо 15 В (третій висновок харчування), а на вивід 6 (вхід S) сигнал рівня ТТЛ (5 В) і частотою 100 Гц. Цей сигнал проходить до висновку 1 (висновок Р) без інверсії, але амплітуда його збільшується до напруги 15 В.

Цей же сигнал при активному рівні (лог.1) інвертує сигнали з виходу дешифратора (аналогічно 176ІД2,3). Оскільки вихідні ключі мікросхеми живляться від джерела 15 В, то рівень на них буде змінюватися від 0 до 15 В з частотою 100 Гц, причому в протифазі з сигналом Р. Таким чином на активних сегментах індикатора буде присутній змінна напруга, на неактивних - 0.

Варто зауважити, що дешифратор є повним - тобто в змозі відображати не тільки цифри від 0 до 9, але і символи «L», «Н», «Р», «А», «-» відповідно до двійкового коду 10-14. При коді 15 всі сегменти гасяться.

Хоча основне призначення мікросхеми - управління ЖК індикатором, її вихідної потужності достатньо для запалювання світлодіодної матриці (при напрузі живлення до 10 В - навіть без токоограничивающих резисторів). Змінюючи рівень на вході S, можна живити матриці як із загальним анодом, так і з загальним катодом. Вихід Р при цьому не використовується.

——————————————-

мікросхема 564ІД5

Дешифратор відрізняється від 564ІД4 відсутністю виходу Р і має чотирьохрозрядний регістр-засувку, аналогічну К176ІД2.

Управління регістром здійснюється по входу С: «1» - пряме проходження коду на дешифратор і далі на виходи для підключення сегментів індикатора, «0» - замиканні інформації для відображення. У такому режимі мікросхема не реагує на зміну двійкового коду на вході. Замиканні інформації відбувається в момент спаду рівня на вході С.

Цікава особливість дешифраторів К176ІД2, К176ІД3, 564ІД4 і 564ІД5 - однакова розводка однойменних висновків входу і виходу.

——————————————-

мікросхема КР1561ІД6

Один корпус мікросхеми містить два незалежних двійковій-десяткових дешифратора на два входи і чотири виходи. Кожен дешифратор забезпечений входом стробирования.

Активні рівні входу і виходу - високі, входу стробування - низький. При «0» на вході S дешифратор працює (на виході з'являється десятковий еквівалент вхідного коду), при «1» - все виходи встановлюються в «0».

Активні рівні входу і виходу - високі, входу стробування - низький. При «0» на вході S дешифратор працює (на виході з'являється десятковий еквівалент вхідного коду), при «1» - все виходи встановлюються в «0».

мікросхема КР1561ІД7

Повний аналог КР1561ІД6 з розведення та алгоритму функціонування, але на виходах обох дешифраторів стоять інвертори (активний рівень виходу - низький).

Через наявність інверсних виходів мікросхема ідеально підходить для управління більшістю КМОП дешифраторів при їх каскадному включенні. На малюнку нижче у схемі управління групою К561ІД1 застосований один дешифратор мікросхеми КР1561ІД7, що дозволило побудувати дешифратор з 32 виходами всього на п'яти корпусах.

Через наявність інверсних виходів мікросхема ідеально підходить для управління більшістю КМОП дешифраторів при їх каскадному включенні. На малюнку нижче у схемі управління групою К561ІД1 застосований один дешифратор мікросхеми КР1561ІД7, що дозволило побудувати дешифратор з 32 виходами всього на п'яти корпусах.

Для побудови повного дешифратора на 8 виходів до мікросхемі КР1561ІД6 (вихідний код - прямий) або КР1561ІД7 (вихідний код - інверсний) досить додати всього один інвертор:

——————————————-

Логічні пристрої поділяють на два класи: комбінаційні і послідовних.

пристрій називають комбінаційною, Якщо його вихідні сигнали в певний момент часу однозначно визначаються вхідними сигналами, що мають місце в цей момент часу.

В іншому випадку пристрій називають послідовних або кінцевим автоматом (цифровим автоматом, автоматом з пам'яттю). У послідовних пристроях обов'язково є елементи пам'яті. Стан цих елементів залежить від передісторії надходження вхідних сигналів. Вихідні сигнали послідовних пристроїв визначаються не тільки сигналами, наявними на входах в даний моментчасу, але і станом елементів пам'яті. Таким чином, реакція послідовних пристрою на певні вхідні сигнали залежить від передісторії його роботи.

Серед як комбінаційних, так і послідовних пристроїв виділяються типові, найбільш широко використовувані на практиці.

шифратори

Шифратор - це комбінаційний пристрій, що перетворює десяткові числа в двійкову систему числення, причому кожному входу може бути поставлено у відповідність десяткове число, а набір вихідних логічних сигналів відповідає певному двійкового коду. Шифратор іноді називають «кодером» (від англ. Coder) і використовують, наприклад, для перекладу десяткових чисел, набраних на клавіатурі кнопкового пульта управління, в двійкові числа.

Якщо кількість входів настільки велике, що в шифраторі використовуються всі можливі комбінації сигналів на виході, то такий шифратор називається повним, якщо не все, то неповним. Число входів і виходів в повному шифраторі пов'язано співвідношенням n = 2 m, де n- число входів, m- число виходів.

Так, для перетворення коду кнопкового пульта в чотирирозрядний двійкове число досить використовувати лише 10 входів, в той час як повне число можливих входів дорівнюватиме 16 (n = 2 4 = 16), тому шифратор 10 × 4 (з 10 в 4) буде неповним .

Розглянемо приклад побудови шифратора для перетворення десятирозрядний одиничного коду (десяткових чисел від 0 до 9) в двійковий код. При цьому передбачається, що сигнал, відповідний логічній одиниці, в кожен момент часу подається тільки на один вхід. Умовне позначеннятакого шифратора і таблиця відповідності коду наведені на рис. 3.35.

використовуючи дану таблицювідповідності, запишемо логічні вирази, Включаючи в логічну суму ті вхідні змінні, які відповідають одиниці деякої вихідної змінної. Так, на виході у 1 буде логічна «1» тоді, коли логічна «1» буде або на вході Х 1, або Х 3, або Х 5, або Х 7, або X 9, т. Е. У 1 = Х 1 + Х 3 + Х 5 + Х 7 + X 9

Аналогічно отримуємо у 2 = Х 2 + Х 3 + Х 6 + X 7 у 3 = Х 4 + Х 5 + Х 6 + Х 7 у 4 = Х 8 + X 9

Уявімо на рис. 3.36 схему такого шифратора, використовуючи елементи АБО.  На практиці часто використовують шифратор з пріоритетом. У таких Шифратори код двійкового числа відповідає найвищому номеру входу, на який подано сигнал «1», т. Е. На пріоритетний шифратор допускається подавати сигнали на кілька входів, а він виставляє на виході код числа, відповідного старшому входу.

На практиці часто використовують шифратор з пріоритетом. У таких Шифратори код двійкового числа відповідає найвищому номеру входу, на який подано сигнал «1», т. Е. На пріоритетний шифратор допускається подавати сигнали на кілька входів, а він виставляє на виході код числа, відповідного старшому входу.

Розглянемо як приклад (рис. 3.37) шифратор з пріоритетом (пріоритетний шифратор) К555ІВЗ серії мікросхем К555 (ТТЛШ).

Шифратор має 9 інверсних входів, позначених через PR l, ..., PR 9. Абревіатура PR позначає «пріоритет». Шифратор має чотири інверсних виходу B l, ..., B 8. Абревіатура B означає «шина» (від англ. Bus). Цифри визначають значення активного рівня (нуля) у відповідному розряді двійкового числа. Наприклад, B 8 позначає, що нуль на цьому виході відповідає числу 8. Очевидно, що це неповний шифратор.

Якщо на всіх входах - логічна одиниця, то на всіх виходах також логічна одиниця, що відповідає числу 0 в так званому інверсному коді (1111). Якщо хоча б на одному вході є логічний нуль, то стан вихідних сигналів визначається найбільшим номером входу, на якому є логічний нуль, і не залежить від сигналів на входах, що мають менший номер.

Наприклад, якщо на вході PR 1 - логічний нуль, а на всіх інших входах - логічна одиниця, то на виходах є наступні сигнали: В 1 - 0, В 2 - 1, В 4 - 1, В 8 - 1, що відповідає числу 1 в інверсному коді (1110).

Якщо на вході PR 9 логічний нуль, то незалежно від інших вхідних сигналів на виходах є наступні сигнали: В 1 - 0, В 2 - 1, В 4 - 1, В 8 - 0, що відповідає числу 9 в інверсному коді (0110) .

Основне призначення шифратора - перетворення номера джерела сигналу в код (наприклад, номери натиснутою кнопки деякої клавіатури).

дешифратори

Називається комбінаційний пристрій, Перетворює n-розрядний двійковий код в логічний сигнал, що з'являється на тому виході, десятковий номер якого відповідає бінарного коду. Число входів і виходів в так званому повному дешифраторі пов'язано співвідношенням m = 2 n, де n- число входів, а m- число виходів. Якщо в роботі дешифратора використовується неповне число виходів, то такий дешифратор називається неповним. Так, наприклад, дешифратор, який має 4 входи і 16 виходів, буде повним, а якби виходів було тільки 10, то він був би неповним.

Звернемося для прикладу до дешифратор К555ІД6 серії К555 (рис. 3.38).

Дешифратор має 4 прямих входу, позначених через А 1, ..., А 8. Абревіатура A позначає «адреса» (від англ.address). Зазначені входи називають адресними. Цифри визначають значення активного рівня (одиниці) у відповідному розряді двійкового числа. Дешифратор має 10 інверсних виходів Y 0, ..., Y 9. Цифри визначають десяткове число, що відповідає заданому двійковому числу на входах. Очевидно, що цей дешифратор неповний.

Значення активного рівня (нуля) має той вихід, номер якого дорівнює десятковому числу, що визначається двійковим числом на вході. Наприклад, якщо на всіх входах - логічні нулі, то на виході Y 0 - логічний нуль, а на інших виходах - логічна одиниця. Якщо на вході А 2 - логічна одиниця, а на інших входах - логічний нуль, то на виході Y 2 - логічний нуль, а на інших виходах - логічна одиниця. Якщо на вході - двійкове число, що перевищує 9 (наприклад, на всіх входах одиниці, що відповідає двійковому числу 1111 та десятковому числу 15), то на всіх виходах - логічна одиниця.

Дешифратор - одне з широко використовуваних логічних пристроїв. Його застосовують для побудови різних комбінаційних пристроїв.

Розглянуті шифратори і дешифратори є прикладами найпростіших перетворювачів кодів.

перетворювачі кодів

У загальному випадку, називають пристрої, призначені для перетворення одного коду в інший, при цьому часто вони виконують нестандартні перетворення кодів. Перетворювачі кодів позначають через X / Y.

Розглянемо особливості реалізації перетворювача на прикладі перетворювача Трьохелементний коду в пятіелементной. Припустимо, що необхідно реалізувати таблицю відповідності кодів, наведену на рис. 3.39.

Тут через N позначено десяткове число, відповідне вхідного двійкового коду. Перетворювачі кодів часто створюють за схемою дешифратор - шифратор. Дешифратор перетворює вхідний код в деякий десяткове число, а потім шифратор формує вихідний код. Схема перетворювача, створеного за таким принципом, наведена на рис. 3.40, де використаний матричний діодний шифратор. Принцип роботи такого перетворювача досить простий. Наприклад, коли на всіх входах дешифратора логічний «О», то на його виході 0 з'являється логічна «1», що призводить до появи «1» на виходах у 4 і у 5, т. Е. Реалізується перший рядок таблиці відповідності кодів.

промисловість випускає велике число шифраторів, дешифраторіві перетворювачів кодів, таких як дешифратор 4 × 16 з стробированием (К555ІДЗ), перетворювач коду для управління світлодіодною матрицею 7 × 5 (К155ІД8), перетворювач коду для управління шкальні індикатором (К155ІД15) і ін.

Одними з дуже важливих елементів цифрової техніки, а особливо в комп'ютерах і системах управління є шифратори і дешифратори.

Коли ми чуємо слово шифратор або дешифратор, то в голову приходять фрази з шпигунських фільмів. Щось на кшталт: розшифруйте депешу і зашифруйте відповідь.

В цьому немає нічого неправильного, так як в шифрувальних машинах наших і зарубіжних резидентур використовуються шифратори і дешифратори.

Шифратори.

Таким чином, шифратор (кодер), це електронний пристрій, В даному випадку мікросхема, яка перетворює код однієї системи числення в код іншої системи. Найбільшого поширення в електроніці отримали шифратори, що перетворюють позиційний десятковий код, в паралельний двійковий. Ось так шифратор може позначатися на принциповій схемі.

Наприклад, уявімо, що ми тримаємо в руках звичайний калькулятор, яким зараз користується будь-який школяр.

Оскільки всі дії в калькуляторі виконуються з двійковими числами (згадаємо основи цифрової електроніки), то після клавіатури варто шифратор, який перетворює вводяться числа в двійкову форму.

Всі кнопки калькулятора з'єднуються із загальним проводом і, натиснувши, наприклад, кнопку 5 на вході шифратора, ми відразу одержимо двійкову форму даного числа на його виході.

Звичайно ж, шифратор калькулятора має більше число входів, так як крім цифр в нього потрібно ввести ще якісь символи арифметичних дій, тому з виходів шифратора знімаються не тільки числа в двійковій формі, а й команди.

Якщо розглянути внутрішню структуру шифратора, то нескладно переконатися, що він виконаний на найпростіших базових логічних елементах.

У всіх пристроях управління, які працюють на двійковій логіці, але для зручності оператора мають десяткову клавіатуру, використовуються шифратори.

Дешифратори.

Дешифратори відносяться до тієї ж групи, тільки працюють з точністю до навпаки. Вони перетворять паралельний двійковий код в позиційний десятковий. Умовне графічне позначення на схемі може бути таким.

Або таким.

Якщо говорити про дешифратора більш повно, то варто сказати, що вони можуть перетворювати двійковий код в різні системи числення (десяткову, шестнадцатиричную та ін.). Все залежить від конкретної мети і призначення мікросхеми.

найпростіший приклад. Ви не раз бачили цифровий семисегментний індикатор, наприклад, світлодіодний. На ньому відображаються десяткові цифри і числа до яких ми звикли з дитинства (1, 2, 3, 4 ...). Але, як відомо, цифрова електроніка працює з двійковими числами, які представляють комбінацію 0 і 1. Що ж перетворило двійкового коду в десятковий і подало результат на цифровий семисегментний індикатор? Напевно, ви вже здогадалися, що це зробив дешифратор.

Роботу дешифратора можна оцінити вживу, якщо зібрати нескладну схему, яка складається з мікросхеми-дешифратора К176ІД2і світлодіодного семисегментний індикатора, який ще називають «вісімкою». Погляньте на схему, по ній легше розібратися, як працює дешифратор. Для швидкої збірки схеми можна використовувати беспаечное макетну плату.

Для довідки. Мікросхема К176ІД2 розроблялася для управління 7-ми сегментним світлодіодним індикатором. Ця мікросхема здатна перетворити двійковий код від 0000 до 1001 , Що відповідає десятковим цифрам від 0 до 9 (одна декада). Інші, більш старші комбінації просто не відображаються. Висновки C, S, K є допоміжними.

У мікросхеми К176ІД2 є чотири входи (1, 2, 4, 8). Їх ще іноді позначають D0 - D3. На ці входи подається паралельний двійковий код (наприклад, 0001). В даному випадку, двійковий код має 4 розряду. Мікросхема перетворює код так, що на виходах ( a - g) З'являються сигнали, які і формують на семисегментний індикаторі десяткові цифри і числа, до яких ми звикли. Так як дешифратор К176ІД2 здатний відобразити десяткові цифри в інтервалі від 0 до 9, то на індикаторі ми побачимо тільки їх.

До входів дешифратора К176ІД2 підключені 4 тумблера (S1 - S4), за допомогою яких на дешифратор можна подати паралельний двійковий код. Наприклад, при замиканні перемикача S1на 5 висновок мікросхеми подається логічна одиниця. Якщо ж розімкнути контакти тумблера S1- це буде відповідати логічному нулю. За допомогою перемикачів ми зможемо вручну встановлювати на входах мікросхеми логічний 1 або 0. Думаю, з цим все зрозуміло.

На схемі показано, як на входи дешифратора DD1 поданий код 0101. На світлодіодному індикаторівідобразиться цифра 5. Якщо замкнути тільки тумблер S4, то на індикаторі відобразиться цифра 8. Щоб записати число від 0 до 9 в двійковому кодідосить чотирьох розрядів: a 3 * 8 + a 2 * 4 + a 1 * 2 + a 0 * 1, де a 0 - a 3, - це цифри з системи числення (0 або 1).

Уявімо число 0101 в десятковому вигляді 0101 = 0*8 + 1*4 + 0*2 + 1*1 = 4 + 1 = 5 . Тепер поглянемо на схему і побачимо, що вага розряду відповідає цифрі, на яку множиться 0 або 1 у формулі.

Дешифратор на базі технології ТТЛ - К155ІД1 використовувався свого часу для управління газорозрядним цифровим індикатором типу ІН8, ІН12, які були дуже затребувані в 70-і роки, так як світлодіодні низьковольтні індикатори ще були дуже великою рідкістю.

Все змінилося в 80-і роки. Можна було вільно придбати семисегментні світлодіодні матриці (індикатори) і серед радіоаматорів прокотився бум збірки електронного годинника. саморобні електронний годинникне зібрав для будинку тільки ледачий.