صاحبان پتنت RU 2559705:

این اختراع مربوط به حوزه فناوری کامپیوتر، اتوماسیون است و می تواند در ساختارها و سیستم های دیجیتال مختلف استفاده شود کنترل خودکار، انتقال اطلاعات و غیره

در سیستم های محاسباتی و کنترلی مختلف، رمزگشاها به طور گسترده ای مورد استفاده قرار می گیرند که بر اساس منطق ترانزیستور-ترانزیستور و منطق جفت امیتر اجرا می شوند، مطابق با قوانین جبر بولی عمل می کنند و دارای دو حالت منطقی "0" و "1" در خروجی هستند. با پتانسیل کم و زیاد مشخص می شود. معماری کلاسیک رمزگشا در مقالات و کتاب ها منتشر شده است، ریزتراشه ها در حال تولید انبوه هستند.

نقطه ضعف قابل توجه این دسته از رمزگشاها این است که عناصر منطقی آن، با استفاده از سیگنال های باینری بالقوه، ساختاری چند لایه دارند که استفاده از آن در فرآیندهای فنی ولتاژ پایین مدرن غیرممکن یا ناکارآمد است و همچنین غیرخطی بودن حالت های عملیاتی عناصر و بحرانی بودن پارامترهای ساختار عناصر منطقی و سیگنال های ورودی. در نهایت، این منجر به کاهش عملکرد رمزگشاهای شناخته شده می شود.

به عنوان دستگاههایی برای پردازش اطلاعات دیجیتال، آبشارهای ترانزیستوری برای تبدیل متغیرهای منطقی ورودی (جریانها) نیز استفاده میشوند که بر اساس آینههای جاری اجرا میشوند که عملکرد پردازش منطقی متغیرهای جریان ورودی را اجرا میکنند.

یک اشکال قابل توجه مدارهای شناخته شده این کلاس این است که آنها عملکرد تبدیل دو سیگنال جریان ورودی با چهار حالت "00"، "01"، "10"، "11" را به چهار سیگنال جریان خروجی اجرا نمی کنند. این اجازه نمی دهد بر اساس آن یک پایه کامل از ابزارهای پردازش سیگنال با متغیرهای فعلی که بر اساس اصول جبر خطی کار می کنند ایجاد کنید.

در آثار و همچنین تک نگاری های نویسنده مشترک این برنامه، نشان داده شده است که جبر بولی یک مورد خاص از یک جبر خطی عمومی تر است، اجرای عملیکه در ساختار دستگاه های محاسباتی و منطقی، اتوماسیون نسل جدید مستلزم ایجاد یک پایگاه المان ویژه است که بر اساس منطق با نمایش داخلی سیگنال های دو ارزشی و چند ارزشی پیاده سازی شده است که در آن کوانتومی فعلی Ι 0 معادل یک سیگنال منطقی استاندارد است. دستگاه ادعا شده "رمزگشا 2 تا 4" به این نوع دستگاه های منطقی اشاره دارد و با سیگنال های جریان ورودی کار می کند و سیگنال جریان خروجی تولید می کند.

نزدیکترین نمونه اولیه دستگاه ادعا شده، دستگاه منطقی "رمزگشا 2 تا 4" است که در ثبت اختراع ایالات متحده 5742154 ارائه شده است که شامل 1 و 2 ورودی منطقی اول دستگاه، 3 اول، 4 دوم، 5 سوم، چهارم 6 خروجی منطقی جریان دستگاه، 7 ترانزیستور اول، 8 دوم و سوم 9 ترانزیستور خروجی که پایه های آنها با هم ترکیب شده و به منبع ولتاژ 10 بایاس اول، ترانزیستورهای 11 چهارم، 12 پنجم و 13 خروجی ششم متصل شده اند. یک نوع رسانایی متفاوت که پایه های آن ترکیب شده و به منبع ولتاژ 14 بایاس دوم متصل شده است، امیتر ترانزیستور 7 خروجی اول متصل به امیتر ترانزیستور 11 خروجی چهارم، امیتر ترانزیستور 8 خروجی دوم است. متصل به امیتر ترانزیستور 12 خروجی پنجم، امیتر ترانزیستور 9 خروجی سوم به امیتر ترانزیستور 13 خروجی ششم متصل است، 3 خروجی منطقی جریان اول دستگاه به کلکتور 7 خروجی اول متصل است. ترانزیستور، 4 دستگاه خروجی منطقی جریان دوم a به کلکتور ترانزیستور 9 خروجی سوم، کلکتور ترانزیستور 11 خروجی چهارم به خروجی منطقی 5 جریان سوم دستگاه متصل است، کلکتور ترانزیستور 13 خروجی ششم به منطق 6 جریان چهارم متصل است. خروجی دستگاه، 15 آینه اول و 16 آینه دوم با منبع تغذیه 17 باس اول، آینه سوم 18 جریان، با باس منبع تغذیه 19 دوم، منبع جریان مرجع کمکی 20 مطابقت دارد.

هدف اصلی اختراع پیشنهادی ایجاد یک عنصر منطقی است که رمزگشایی حالت دو متغیر منطقی ورودی و تشکیل چهار سیگنال خروجی به شکل فعلی را فراهم می کند. در نهایت، این به شما امکان می دهد عملکرد دستگاه های تبدیل اطلاعات شناخته شده را با استفاده از رمزگشای پیشنهادی افزایش داده و ایجاد کنید. پایه عنصردستگاه های محاسباتی که بر اساس اصول جبر خطی چند ارزشی کار می کنند.

مشکل با این واقعیت حل می شود که در دستگاه منطقی "رمزگشا 2 تا 4" (شکل 1) که شامل 1 و 2 ورودی منطقی اول دستگاه است، 3 اول، 4 دوم، 5 سوم، چهارم 6 خروجی منطقی جریان دستگاه، 7 ترانزیستور اول، دوم 8 و سوم 9 ترانزیستور خروجی که پایه های آنها با هم ترکیب شده و به منبع ولتاژ 10 بایاس اول، ترانزیستور 11 چهارم، 12 پنجم و ششم 13 ترانزیستور خروجی یک رسانایی متفاوتی که پایه های آن ترکیب شده و به منبع ولتاژ 14 بایاس دوم متصل می شود، امیتر ترانزیستور 7 خروجی اول به امیتر ترانزیستور چهارم خروجی AND متصل است، امیتر ترانزیستور 8 خروجی دوم متصل به امیتر ترانزیستور 12 خروجی پنجم، امیتر ترانزیستور 9 خروجی سوم به امیتر ترانزیستور 13 خروجی ششم متصل است، 3 خروجی منطقی جریان اول دستگاه به کلکتور 7 خروجی اول متصل است. ترانزیستور، خروجی منطقی 4 جریان دوم دستگاه به کلکتور خروجی 9 سوم متصل است. در مورد ترانزیستور، کلکتور ترانزیستور 11 خروجی چهارم به خروجی منطقی 5 جریان سوم دستگاه متصل است، کلکتور ترانزیستور خروجی 13 ششم به خروجی منطقی 6 جریان چهارم دستگاه، 15 اول و دوم 16 آینه جریان مطابق با باس 17 منبع تغذیه اول، آینه سوم 18 جریان، مطابق با باس منبع تغذیه 19 دوم، منبع جریان مرجع کمکی 20، عناصر و اتصالات جدید ارائه شده است - 1 ورودی منطقی اول دستگاه است. به ورودی آینه 18 جریان سوم متصل می شود، 2 ورودی منطقی دوم دستگاه به ورودی 15 آینه جریان اول وصل می شود، 21 اول خروجی جریان 15 آینه جریان اول به قطره چکان های ترکیبی وصل می شود. ترانزیستور 12 خروجی دوم 8 و پنجم و از طریق منبع جریان مرجع کمکی 20 به باس منبع تغذیه 19 دوم وصل می شود، خروجی 22 جریان دوم از آینه 15 جریان اول به امیترهای ترکیبی 7 اول و 11 چهارم متصل می شود. ترانزیستور خروجی ov و به 23 خروجی جریان اول آینه 18 جریان سوم وصل می شود، کلکتور ترانزیستور 8 خروجی دوم به ورودی آینه 16 جریان دوم وصل می شود که خروجی جریان آن به امیترهای ترکیبی وصل می شود. ترانزیستور سوم 9 و ششم 13 خروجی و به 24 خروجی جریان دوم 18 آینه جریان سوم و کلکتور ترانزیستور 12 خروجی پنجم به باس 19 دوم منبع تغذیه متصل است.

طرح واحد منطقی نمونه اولیه در شکل نشان داده شده است. 1. در شکل. 2 نمودار دستگاه ادعا شده را مطابق با بند 1 ادعاها نشان می دهد.

در شکل. 3 نموداری از دستگاه مورد ادعا را مطابق با بند 2 بند 3 بند 4 ادعاها نشان می دهد.

در شکل. 4 داده شده است مدارشکل. 3 در محیط شبیه سازی رایانهای MS9 با اجرای خاصی از واحدهای عملکردی اصلی (آینه های فعلی، منابع جریان مرجع).

در شکل. 5 نتایج شبیه سازی کامپیوتری مدار شکل. 4.

دستگاه منطقی "رمزگشا 2 تا 4" از شکل. 2 شامل 1 و 2 ورودی منطقی اول دستگاه، 3 اول، 4 دوم، 5 سوم، 6 خروجی منطقی جریان چهارم دستگاه، 7 اول، 8 دوم و 9 ترانزیستور خروجی سوم، پایههای آنها به منبع ولتاژ 10 بایاس اول، ترانزیستورهای 11، پنجم 12 و ششم خروجی با نوع رسانایی متفاوت که پایههای آنها ترکیب شده و به منبع ولتاژ بایاس 14 دوم متصل شدهاند، متصل میشوند. امیتر ترانزیستور 7 خروجی اول به امیتر ترانزیستور 11 خروجی چهارم، امیتر ترانزیستور 8 خروجی دوم به امیتر ترانزیستور 12 خروجی پنجم وصل شده است، امیتر ترانزیستور 9 خروجی سوم به امیتر ترانزیستور 13 خروجی ششم، 3 خروجی منطقی جریان اول دستگاه به کلکتور 7 ترانزیستور خروجی اول متصل می شود، 4 خروجی منطقی جریان دوم دستگاه به کلکتور 9 ترانزیستور خروجی سوم متصل می شود. ، کلکتور ترانزیستور خروجی 11 چهارم به سومین جریان 5 لو متصل است خروجی منطقی دستگاه، کلکتور ترانزیستور 13 خروجی ششم به خروجی منطقی 6 جریان چهارم دستگاه متصل می شود، آینه 15 جریان اول و 16 جریان دوم با باس منبع تغذیه 17 اول مطابقت دارد، آینه 18 جریان سوم مطابقت دارد. با باس منبع تغذیه 19 دوم، یک منبع مرجع کمکی جریان 20. 1 ورودی منطقی اول دستگاه به ورودی آینه سوم جریان 18 وصل می شود، 2 ورودی منطقی دوم دستگاه به ورودی دستگاه متصل می شود. آینه 15 جریان اول، خروجی 21 جریان اول آینه 15 جریان اول به امیترهای ترکیبی 8 ترانزیستور خروجی دوم و پنجم 12 ترانزیستور و از طریق منبع جریان مرجع کمکی 20 به باس منبع تغذیه 19 دوم وصل می شود. خروجی 22 جریان دوم آینه 15 جریان اول به امیترهای ترکیبی 7 و 11 ترانزیستور خروجی چهارم وصل می شود و به خروجی 23 جریان اول آینه 18 جریان سوم وصل می شود، کلکتور ترانزیستور 8 خروجی دوم با ورودی متصل است خانه آینه 16 جریان دوم که خروجی جریان آن به امیترهای ترکیبی ترانزیستور سوم 9 و 13 خروجی ششم وصل شده و به خروجی 24 جریان دوم آینه 18 جریان سوم و کلکتور ترانزیستور 12 خروجی پنجم به باس منبع تغذیه 19 دوم متصل است.

در شکل. 3 مطابق با بند 2 ادعاها، اولین ورودی منطقی 1 دستگاه از طریق اولین مرحله وارونگی اضافی به ورودی سومین آینه 18 جریانی متصل می شود، که در قالب 26 آینه جریان اضافی اول ساخته شده است، مطابق با اولین اتوبوس منبع تغذیه 17.

در شکل. 3، مطابق بند 3 ادعا، کلکتور ترانزیستور 11 خروجی چهارم از طریق دومین مرحله وارونگی اضافی به سومین خروجی منطقی 5 جریان دستگاه متصل می شود، که به صورت آینه دوم 27 جریان اضافی ساخته شده است. مطابق با اتوبوس منبع تغذیه 19 دوم.

علاوه بر این، در شکل. 3، مطابق بند 4 ادعا، کلکتور ترانزیستور 13 خروجی ششم از طریق سومین مرحله وارونگی اضافی به چهارمین خروجی منطقی 6 جریان دستگاه متصل می شود که به صورت آینه سوم 28 جریان اضافی ساخته شده است. مطابق با اتوبوس منبع تغذیه 19 دوم.

عملکرد مدار رمزگشای پیشنهادی را با ورودی ها و خروجی های جریان در شکل 1 در نظر بگیرید. 2.

رمزگشای 2 تا 4 عملکردهای شناخته شده ای را اجرا می کند:

که در آن A 0 , A ¯ 0 - سیگنال های مستقیم و معکوس در ورودی 1 دستگاه شکل. 2،

A 1 , A ¯ 1 - سیگنال های مستقیم و معکوس در ورودی 2 دستگاه شکل. 2.

یکی از ویژگی های پیاده سازی آنها در جبر خطی استفاده از عملیات تفاضل کوتاه برای این منظور است:

که جدول صدق آن در زیر آورده شده است

از جدول بر می آید که از چهار ترکیب ممکن از مقادیر متغیرهای ورودی، یک مقدار منفرد از تابع تنها با یک ترکیب مربوط به شرط A 0 >A 1 مطابقت دارد. با تعیین متغیرهای ورودی مستقیم و معکوس در جدول حقیقت، می توان یک مقدار واحد از تابع مربوط به هر یک از ترکیبات ممکن از مقادیر متغیرهای ورودی را به دست آورد.

اعمال این عملیات منجر به نمایش زیر از عملکردهای منطقی رمزگشا می شود:

اجرای این عملیات به شرح زیر است.

سیگنال های متغیرهای ورودی A 0 و A 1 از طریق ورودی های منطقی 1 و 2 به 15 آینه اول و 18 سوم جریان جریان داده می شود که از طریق آنها سیگنال های مشخص شده ضرب شده و علامت آنها تغییر می کند. در این حالت، سیگنال A 0 به شکل یک جریان خروجی (یعنی به شکل A 0) منتقل می شود و با استفاده از آینه سوم جریان 18، به جریان ورودی (یعنی به شکل -A) تبدیل می شود. 0) و A 1 به صورت مستقیم به شکل جریان ورودی (یعنی به شکل -A 1) می آید و با کمک اولین آینه جریان 15 به جریان خروجی (یعنی به شکل) تبدیل می شود. از A 1).

در نقطه اتصال خروجی های 22 آینه جریان اول 15 و 23 آینه سوم جریان 18 عملیات A 1 -A 0 اجرا می شود. سیگنال تفاوت به فرستنده های ترکیبی ترانزیستورهای 7 و 11 اعمال می شود که حالت های عملیاتی آنها توسط منابع ولتاژ بایاس 10 و 14 دوم تنظیم می شود.

اگر سیگنال تفاوت مثبت باشد، به عنوان مثال. 0 -A 1 > 0، ترانزیستور 7 بسته است، و ترانزیستور 11 باز است و خروجی 5 کوانتومی از جریان ورودی مربوط به -(A 0 -A 1)=A 1 -A 0 داده می شود که اجرا می کند. عبارت (2). برای هر ترکیب دیگری از مقادیر کوانتومی فعلی، در خروجی 5 جریانی وجود نخواهد داشت.

اگر A 0 -A 1 ≤0، آنگاه ترانزیستور 7 باز است و ترانزیستور 11 بسته است و به خروجی 3 کوانتومی از جریان خروجی مربوط به A 0 -A 1 داده می شود که عبارت (3) را اجرا می کند. برای هر ترکیب دیگری از مقادیر کوانتومی فعلی، در خروجی 3 جریانی وجود نخواهد داشت.

در نقطه اتصال خروجی 21 اولین آینه جریان و منبع جریان مرجع کمکی 20، A 1 -1 کم می شود. سیگنال تفاوت به فرستندههای ترکیبی ترانزیستورهای 8 و 12 اعمال میشود که حالتهای عملیاتی آنها توسط منابع ولتاژ بایاس 10 و 14 دوم تنظیم میشود. اگر سیگنال تفاوت مثبت باشد، به عنوان مثال. 1 -1>0، ترانزیستور 8 بسته است و ترانزیستور 12 باز است. اگر سیگنال اختلاف کمتر یا مساوی صفر باشد، ترانزیستور 8 باز و ترانزیستور 12 بسته است.

در حالت اول، سیگنال از طریق ترانزیستور 12 به زمین بسته می شود. در حالت دوم، کوانتوم جریان دیفرانسیل خروجی A 1 -1 با کمک آینه سوم جریان 16 به کوانتوم جریان خروجی 1-A 1 تبدیل می شود و کوانتوم جریان ورودی -A 0 از آن کم می شود. سیگنال تفاوت به فرستنده های ترکیبی ترانزیستورهای 9 و 13 اعمال می شود که حالت های عملکرد آنها توسط منابع ولتاژ بایاس 10 و 14 دوم تنظیم می شود. اگر سیگنال تفاوت مثبت باشد، به عنوان مثال. ترانزیستور 9 بسته و ترانزیستور 13 باز است. در همان زمان، یک سیگنال اختلاف (1-A 1)-A 0 به خروجی 6 به شکل یک کوانتوم جریان خروجی، که بیان (4) را پیاده سازی می کند، خروجی می شود. برای هر ترکیب دیگری از مقادیر کوانتومی فعلی، در خروجی 4 جریانی وجود نخواهد داشت.

اختصاصی این دستگاهنمایش سیگنال های خروجی به صورت کوانتومی جریان ورودی (در خروجی های 3 و 4) و خروجی (در خروجی های 5 و 6) است. برای مواردی که همه سیگنال های خروجی در یک جهت مورد نیاز هستند، مدار رمزگشا نشان داده شده در شکل. 3. تفاوت آن با نمودار در شکل. 2 استفاده از دو آینه جریان اضافی 27 و 28 است که به ورودی های آنها کلکتورهای ترانزیستورهای 11 و 13 وصل شده اند و خروجی ها خروجی های 5 و 6 رمزگشا هستند. در نتیجه، تمام سیگنال های خروجی با کوانتوم های جریان ورودی نشان داده می شوند.

همانطور که از توضیحات بالا مشخص است، اجرای دستگاه "رسیور 2 تا 4" در قالب توابع منطقی استاندارد طبق قوانین جبر خطی با تشکیل تفاضل کوانتای فعلی 10 انجام می شود. اجرای عناصر در آینه های فعلی در بسیاری از موارد امکان کاهش ولتاژ تغذیه را فراهم می کند و از آنجایی که تمام عناصر مدارهای کاهش یافته در حالت فعال کار می کنند که عدم اشباع در هنگام سوئیچینگ را فرض می کند، عملکرد کلی دستگاه افزایش می یابد. استفاده از مقادیر پایدار کوانتای جریان I 0 و همچنین تعیین سیگنال خروجی با اختلاف این جریان ها، وابستگی اندک عملکرد مدار را به عوامل بی ثبات کننده خارجی تضمین می کند (انحراف ولتاژ تغذیه، اثرات تشعشع و دما، تداخل حالت معمول و غیره).

نشان داده شده در شکل. 9، شکل. 10 نتیجه شبیه سازی ویژگی های مشخص شده مدارهای پیشنهادی را تایید می کند.

بنابراین، راه حل های مدار در نظر گرفته شده دستگاه منطقی "رمزگشا 2 تا 4" با نمایش جریان دودویی سیگنال مشخص می شود و می تواند به عنوان مبنایی برای محاسبه و کنترل دستگاه های با استفاده از جبر خطی مورد استفاده قرار گیرد، که مورد خاص آن جبر بولی است. .

کتابشناسی - فهرست کتب

1. ثبت اختراع US 6243319 B1، شکل. سیزده.

2. ثبت اختراع US 5604712 A.

3. ثبت اختراع US 4514829 A.

4. ثبت اختراع US 20120020179 A1.

5. ثبت اختراع US 6920078 B2.

6. ثبت اختراع US 6324117 B1، شکل. 3.

7. درخواست ثبت اختراع US 20040018019 A1.

8. ثبت اختراع US 5568061 A.

9. ثبت اختراع US 5148480 A، شکل. 4.

10. Brzozowski I., Zachara L., Kos A. روش طراحی جهانی رمزگشاهای n-to-2n // طراحی مختلط مدارها و سیستم های مجتمع (MIXDES)، 2013 مجموعه مقالات بیستمین کنفرانس بین المللی، 2013 - ص 279 -284 شکل. یکی

11. سوبرامانیام ام.و. نظریه سوئیچینگ و طراحی منطق / رسانه فایروال، 2011. دوم، - 783 c، شکل. 3.174.

12. رمزگشای 2 به 4 خط SN74LVC1G139 [منبع الکترونیکی]. آدرس اینترنتی: http://www.ti.com/lit/ds/symlink/sn741vc1g139.pdf.

13. ثبت اختراع US 8159304، شکل. 5.

14. ثبت اختراع ایالات متحده شماره 5977829، شکل. یکی

15. ثبت اختراع ایالات متحده شماره 5789982، شکل. 2.

16. ثبت اختراع ایالات متحده به شماره 5140282.

17. ثبت اختراع ایالات متحده شماره 6624701، شکل. 4.

18. ثبت اختراع ایالات متحده به شماره 6529078.

19. ثبت اختراع ایالات متحده به شماره 5734294.

20. ثبت اختراع ایالات متحده به شماره 5557220.

21. ثبت اختراع ایالات متحده به شماره 6624701.

22. ثبت اختراع RU شماره 2319296.

23. ثبت اختراع RU شماره 2436224.

24. ثبت اختراع RU شماره 2319296.

25. ثبت اختراع RU شماره 2321157.

26. ثبت اختراع US 6556075، شکل. 2.

27. ثبت اختراع US 6556075، شکل. 6.

28. Chernov N.I.، Yugai V.Y.، Prokopenko N.N.، و همکاران. - Rostov-on-Don، 2013. - C. 146-149.

29. Malyugin V.D. تحقق توابع بولی توسط چندجمله ای های حسابی // اتوماسیون و تله مکانیک، 1982. شماره 4. ص 84-93.

30. Chernov N.I. مبانی تئوری سنتز منطقی ساختارهای دیجیتال در زمینه اعداد واقعی // مونوگراف. - تاگانروگ: TRTU، 2001. - 147 ص.

31. Chernov N.I. سنتز خطی ساختارهای دیجیتال ASOIU // آموزش. - تاگانروگ: TRTU، 2004 - 118 ص.

1. رسیور 2 تا 4 حاوی اولین (1) و دوم (2) ورودی منطقی دستگاه، خروجی های منطقی جریان اول (3)، دوم (4)، سوم (5)، چهارم (6) خروجی های منطقی دستگاه. ترانزیستورهای خروجی اول (7)، دوم (8) و سوم (9) که پایه های آنها با هم ترکیب شده و به منبع ولتاژ بایاس اول (10) چهارم (11)، پنجم (12) و ششم متصل شده است. (13) ترانزیستورهای خروجی با رسانایی متفاوت که پایه های آنها ترکیب شده و به منبع ولتاژ بایاس دوم (14) متصل می شود، امیتر اولین (7) ترانزیستور خروجی به امیتر چهارم (11) متصل می شود. ) ترانزیستور خروجی، امیتر ترانزیستور خروجی دوم (8) به امیتر ترانزیستور پنجم (12) خروجی وصل شده است، امیتر ترانزیستور خروجی سوم (9) به امیتر ترانزیستور ششم (13) متصل است. ترانزیستور خروجی، اولین (3) خروجی منطقی جریان دستگاه به کلکتور اولین (7) ترانزیستور خروجی وصل شده است، دومین (4) خروجی منطقی جریان دستگاه به کلکتور سوم (9) متصل می شود. ترانزیستور خروجی، کول ضریب چهارمین (11) ترانزیستور خروجی به سومین (5) خروجی منطقی جریان دستگاه، کلکتور ترانزیستور خروجی ششم (13) به چهارمین (6) خروجی منطقی جریان دستگاه متصل است. آینه های جریان اول (15) و دوم (16) با گذرگاه منبع تغذیه اول (17)، آینه سوم (18) جریان با گذرگاه منبع تغذیه دوم (19)، منبع جریان مرجع کمکی (20) مطابقت دارند. با مشخصه این که اولین (1) ورودی منطقی دستگاه به ورودی سومین (18) آینه جریان متصل است، دومین (2) ورودی منطقی دستگاه به ورودی اولین (15) جریان متصل است. آینه، اولین (21) خروجی جریان اولین (15) آینه جریان به امیترهای ترکیبی ترانزیستورهای خروجی دوم (8) و پنجم (12) و از طریق منبع جریان مرجع کمکی (20) به باس منبع تغذیه دوم (19)، خروجی جریان دوم (22) آینه جریان اول (15) به قطره چکان های ترکیبی خروجی اول (7) و چهارم (11) متصل می شود. ترانزیستورها و به اولین (23) خروجی جریان سومین (18) آینه جریان، کلکتور دومین (8) ترانزیستور خروجی به ورودی آینه جریان دوم (16) متصل است که جریان خروجی آن به امیترهای ترکیبی ترانزیستورهای خروجی سوم (9) و ششم (13) متصل می شود و به خروجی جریان دوم (24) آینه سوم (18) جریان و کلکتور ترانزیستور خروجی پنجم (12) متصل می شود. به باس منبع تغذیه دوم (19) متصل است.

2. رسیور 2 تا 4 طبق ادعای 1، مشخص می شود که اولین (1) ورودی منطقی دستگاه از طریق اولین مرحله وارونه اضافی به ورودی آینه سوم (18) جریان متصل می شود که به شکل اولین (26) آینه جریان اضافی، مطابق با اولین (17) ریل منبع تغذیه.

3. رسیور 2 تا 4 طبق ادعای 1، مشخص می شود که کلکتور چهارمین (11) ترانزیستور خروجی به سومین (5) خروجی منطقی جریان دستگاه از طریق یک مرحله وارونه اضافی دوم، ساخته شده به شکل دومین (27) آینه جریان اضافی، مطابق با دومین (19) ریل منبع تغذیه.

4. رسیور 2 تا 4 طبق ادعای 1، مشخص می شود که کلکتور ترانزیستور خروجی ششم (13) به چهارمین (6) خروجی منطقی جریان دستگاه از طریق سومین مرحله وارونگی اضافی، ساخته شده به شکل سومین (28) آینه جریان اضافی، مطابق با دومین (19) ریل منبع تغذیه.

اختراعات مشابه:

این اختراع مربوط به ابزارهای رمزگذاری با استفاده از کتاب کد کاهش یافته است نصب تطبیقیبه موقعیت شروع نتیجه فنی شامل کاهش مقدار اطلاعات ارسال شده از سمت گیرنده به سمت فرستنده است.

اختراع مربوط به علوم کامپیوتر، یعنی به کدگذاری اطلاعات ویدیویی. نتیجه فنی شامل افزایش کارایی کدگذاری و رمزگشایی جریان بیت اطلاعات ویدیویی با تقسیم داده ها به لایه های آنتروپی است.

این اختراع به روشی برای رمزگذاری دنباله ای از اعداد صحیح، به دستگاه ذخیره سازی و سیگنالی که چنین توالی رمزگذاری شده ای را حمل می کند، و همچنین به روشی برای رمزگشایی این دنباله رمزگذاری شده مربوط می شود.

این اختراع به یک روش کدگذاری پیشکد و یک سیستم و روش برای ساخت کتاب کد پیشکدینگ در یک سیستم چند خروجی ورودی چندگانه (MIMO) مربوط میشود.

این اختراع مربوط به حوزه فناوری است که از سیگنال های دیجیتالی استفاده می کند و می تواند در دستگاه های ارتباطی، ضبط، ضبط، پخش، تبدیل، رمزگذاری و فشرده سازی سیگنال ها، سیستم های کنترل خودکار استفاده شود.

این اختراع مربوط به حوزه مخابرات است، یعنی به حوزه دستگاه های رمزنگاری و روش های بررسی الکترونیکی امضای دیجیتالی(EDS). .

این اختراع به زمینه پردازش سیگنال دیجیتال، به ویژه فشرده سازی داده ها و بهبود کدگذاری آنتروپی توالی های ویدئویی مربوط می شود. نتیجه فنی افزایش کارایی و کاهش است پیچیدگی محاسباتیکدگذاری آنتروپی روشی برای پردازش یک جریان داده متشکل از چندین عنصر نحوی مبتنی بر جایگزینی عناصر نحوی است که مقادیر آنها احتمال وقوع بالایی دارند با عناصر نحوی که مقادیر آنها دارای احتمال کم هستند. زمینه برای عنصر نحوی تعیین می شود و احتمال وقوع مقادیر آن عناصر نحوی در مدل جریان داده که دارای زمینه خاصی هستند محاسبه می شود. عناصر نحوی جریان داده با زمینه خاصی جایگزین می شوند، اگر احتمال محاسبه شده وقوع مقدار عنصر نحوی بالاتر از یک آستانه معین باشد، با عناصر نحوی که مقادیر آنها احتمال کمی دارند، جایگزین می شوند. 3 n. و 10 z.p. f-ly, 4 ill., 2 tab.

این اختراع مربوط به فناوری ارتباطات است و برای اندازه گیری طیف سیگنال های صوتی اطلاعاتی در نظر گرفته شده است. EFFECT: بهبود دقت اندازه گیری طیف سیگنال های صوتی اطلاعاتی، گسترش عملکرددستگاه ها با پیوند دادن مقادیر لحظه ای طیف به بخش های طول قابل تنظیم سیگنال صوتی موقت. برای این کار از تبدیل کسینوس گسسته (DCT) در روش اندازه گیری طیف به جای تبدیل فوریه سریع (FFT) استفاده می شود که این امکان را فراهم می کند تا با افزایش وضوح، دقت اندازه گیری طیف سیگنال های صوتی را افزایش دهیم. کاهش سطح لبه های جانبی تبدیل پنجره در طیف، و کاهش نوسان اجزای تخمینی دامنه طیفی، و همچنین به شما امکان می دهد مدت زمان بخش های سیگنال صوتی را که طیف لحظه ای بر روی آنها اندازه گیری می شود، در حین شکل گیری کاهش دهید. دو سیگنال به جای یک (اصلی و اضافی)، و سیگنال صوتی دیجیتال اضافی نسبت به سیگنال اصلی متعامد است، مقادیر لحظه ای اندازه گیری شده طیف نیز به هم مرتبط هستند، مدول طیف و مشخصه فرکانس فاز. از سیگنال به بخش هایی از سیگنال صوتی زمانی که از نظر موقعیت زمانی و مدت قابل تنظیم هستند، که این طیف بر اساس آن اندازه گیری می شود. 2 n.p. f-ly, 8 بیمار.

اختراع مربوط به ارتباطات بی سیم. نتیجه فنی افزایش ایمنی نویز، قابلیت اطمینان و راندمان ارتباطی است، در حالی که مصرف انرژی را می توان کاهش داد. برای این، روش شامل: مرحله S1، که در آن دستگاه اصلی یک کد دنباله ای را با استفاده از یک رمزگذار خاص تولید می کند، و کد دنباله را به طور مداوم برای یک دوره زمانی از پیش تعیین شده بر اساس یک درخواست ارتباطی، به هر دستگاه Slave ارسال می کند. رمزگذار خاص یک شیفت رجیستر با است بازخوردروی یک چند جمله ای خاص انجام می شود که ترتیب و ضرایب آن با درخواست اتصال همبستگی دارد، در حالی که همه ضرایب و مقادیر اولیهدر همان زمان برابر با 0 نیستند. دوره زمانی از پیش تعیین شده بزرگتر یا مساوی با مجموع دوره خواب و دوره تشخیص برده است که چرخه خواب و بیداری را تشکیل می دهد. مرحله S2، که در آن دستگاه Slave بخشی پیوسته از کد دنباله را در دوره تشخیص دریافت می کند، کد دنباله را توسط رمزگشای مربوط به رمزگذار رمزگشایی می کند و با توجه به نتیجه رمزگشایی، عملیات مناسب را انجام می دهد. 2 n. و 10 z.p. f-ly، 5 بیمار.

این اختراع مربوط به فناوری ارتباطات است و برای رمزگذاری و رمزگشایی سیگنال ها در نظر گرفته شده است. نتیجه فنی افزایش دقت در رمزگذاری و رمزگشایی سیگنال ها است. روش رمزگذاری سیگنال شامل به دست آوردن سیگنال حوزه فرکانس با توجه به سیگنال ورودی است. تخصیص بیت های از پیش تعیین شده به سیگنال حوزه فرکانس طبق قانون تخصیص از پیش تعیین شده. تنظیم تخصیص بیت برای سیگنال حوزه فرکانس زمانی که بالاترین فرکانس سیگنال حوزه فرکانس که بیت ها به آن تخصیص داده می شوند از مقدار از پیش تعیین شده فراتر رود. و رمزگذاری سیگنال حوزه فرکانس با توجه به تخصیص بیت برای سیگنال دامنه فرکانس. 4 n. و 16 z.p. f-ly, 9 بیمار.

این اختراع مربوط به حوزه مخابرات است و برای محافظت از اطلاعات مخفی ارسال شده در نظر گرفته شده است. نتیجه فنی سطح بالایی از امنیت اطلاعات رمزگذاری شده است. روشی برای رمزگذاری اطلاعات، از جمله ساخت جدولی از مطابقت نمادها و معادل های آنها در فضای (00; FF) در سیستم هگزادسیمال، تولید میز جدیدمنطبق با تغییر جدول اصلی با جابجایی جدول اصلی، i.e. خط مکاتبات با تعداد مشخص شده کاراکتر، رمزگذاری اطلاعات اصلی و فشرده سازی آن به حجم مورد نظر با استفاده از جدول رمزگذاری یونیکد مناسب منتقل می شود. 2 برگه.

این اختراع مربوط به کدگذاری/رمزگشایی یک سیگنال دیجیتال متشکل از بلوک های متوالی از نمونه ها است. نتیجه فنی بهبود کیفیت صدای کدگذاری شده است. رمزگذاری شامل اعمال یک پنجره وزن دهی به دو بلوک M نمونه متوالی است. به طور خاص، چنین پنجره وزن دهی نامتقارن است و شامل چهار است قطعه های فردیبه صورت متوالی در دو بلوک ذکر شده در بالا ادامه مییابد، به طوری که بخش اول در بازه زمانی اول افزایش مییابد، بخش دوم دارای مقدار وزنی ثابت در بازه زمانی دوم است، بخش سوم در بازه زمانی سوم کاهش مییابد، و بخش چهارم دارای مقدار وزنی ثابت است. یک مقدار وزن ثابت در بازه زمانی چهارم. 6 n. و 11 z.p. f-ly, 10 بیمار.

این اختراع به زمینه پردازش سیگنال دیجیتال، به ویژه روشهای رمزگذاری/رمزگشایی تصاویر ویدئویی دیجیتال مربوط میشود. نتیجه فنی افزایش نسبت فشرده سازی تصاویر ویدئویی با کاهش جزئی در کیفیت تصویر رمزگشایی شده در رابطه با تصاویری است که دارای طبیعت فرکانس بالا از طیف سیگنال هستند. روشی برای رمزگذاری/رمزگشایی تصاویر ویدئویی دیجیتال پیشنهاد شده است. طبق روش، در فرآیند کدگذاری، یک جزء فرکانس بالا اضافی خط به خط به جزء فرکانس پایین تبدیل موجک اضافه میشود تا عملکرد اصلی را هموار کند، که برای رمزگذاری استفاده میشود، اما در سمت رمزگشایی سرکوب میشود. با استفاده از فیلتر پایین گذر علاوه بر این، رمزگذاری با استفاده از یک تابع با دو هدف افزایش نسبت فشرده سازی داده ها و حفظ کیفیت تصویر رمزگشایی شده اجرا می شود و ویژگی های فیلتر رمزگشا به عنوان یک محدودیت ارتباطی در مرحله رمزگذاری در نظر گرفته می شود. 8 بیمار، 3 برگه.

این اختراع مربوط به حوزه فناوری ارتباطات بی سیم است. EFFECT: بهبود کیفیت ارتباطات با سرکوب تداخل متوالی بین جریان های سیگنال. روش پیشکدگذاری شامل: انجام پیشپردازش پیشکدینگ بر روی سیگنالی که قرار است ارسال شود، پیشپردازش باعث افزایش قدرت سیگنال ارسالی میشود. انتخاب یک الگوریتم محدود کننده توان با توجه به قانون انتخاب؛ انجام یک عملیات محدود کردن توان روی سیگنال از پیش پردازش شده طبق الگوریتم محدود کننده توان انتخابی. و یک سیگنال از پیش کدگذاری شده با توجه به سیگنال محدود قدرت تولید می کند. تجسمی از اختراع حاضر یک فرستنده، یک گیرنده، و یک سیستم پیش کدگذاری را نشان می دهد. در اختراع حاضر، اثر نامطلوب عمل محدود کردن توان بر انتقال سیگنالها را میتوان در زمانی که توان انتقال محدود میشود با استفاده از عملیات محدود کردن توان کاهش داد. 5 n. و 12 z.p. f-ly, 8 بیمار.

این اختراع مربوط به زمینه کدگذاری و رمزگشایی است و برای کمی سازی بردارهای پوشش فرکانس در نظر گرفته شده است. اثر: افزایش کارایی کوانتیزاسیون بردارهای پوشش فرکانس. این روش شامل: تقسیم N پاکت فرکانس در یک فریم به بردارهای N1، که در آن هر بردار در بردارهای N1 شامل پاکتهای فرکانس M است. کمی کردن اولین بردار به بردارهای N1 با استفاده از اولین کتاب کد برای به دست آوردن یک رمز متناظر با بردار اول کوانتیزه شده، جایی که اولین کتاب کد مذکور به بخش های 2B1 تقسیم می شود. با توجه به کلمه رمز مربوط به اولین بردار کوانتیزه شده، تعیین اینکه بردار اول کوانتیزه شده با بخش iام در بخشهای 2B1 کتاب کد اول مذکور مرتبط است. تعیین کتاب کد دوم با توجه به کتاب کد قسمت ith. و کمی کردن بردار دوم به بردارهای N1 بر اساس کتاب کد دوم گفته شده. در تجسمهای اختراع حاضر، پاکتهای فرکانس به تعدادی از بردارهای کوچکتر تقسیم میشوند تا با استفاده از یک کتاب کد با بیتهای کمتر، کمیسازی برداری را بر روی بردارهای پاکت فرکانس انجام دهیم. 2 n. و 6 z.p. f-ly, 3 بیمار.

گروه اختراعات مربوط به حوزه کدگذاری است. نتیجه فنی افزایش کارایی فشرده سازی داده ها است. روش رمزگذاری دادههای ورودی (D1) شامل تعیین اساساً تکرار بلوکهای داده و/یا بستههای داده در حداقل یکی از قطعات داده ورودی (D1) است، در حالی که بلوکهای داده و/یا بستههای داده شامل مجموعهای از عناصر مربوطه میشوند، جایی که عناصر شامل بیت های مجموعه ای هستند تعیین اینکه آیا عناصر در بلوکهای داده و/یا بستههای داده به طور قابل ملاحظهای تکرار شونده تغییر نمیکنند یا خیر، و/یا تعیین آن عناصر در بلوکهای داده و/یا بستههای داده که به طور قابلتوجهی تکرار میشوند. رمزگذاری عناصر بدون تغییر در داده های رمزگذاری شده (E2) با استفاده از حداقل یک نماد متناظر یا حداقل یک بیت متناظر که نشان دهنده عدم تغییر در عناصر بدون تغییر در مقایسه با عناصر متناظر آنها در بلوک داده مرجع و/یا بسته داده است. و رمزگذاری عناصر تغییر یافته در داده های رمزگذاری شده (E2). 6 n. و 28 z.p. f-ly, 8 بیمار.

این اختراع مربوط به رمزگشاها است. نتیجه فنی افزایش سرعت دستگاه های تبدیل اطلاعات با استفاده از رمزگشای اختراعی است. اولین ورودی منطقی دستگاه به ورودی آینه سوم جریان، ورودی منطقی دوم دستگاه به ورودی آینه جریان اول، خروجی جریان اول آینه جریان اول به ترکیبی متصل می شود. امیترهای ترانزیستورهای خروجی دوم و پنجم و از طریق منبع جریان مرجع کمکی به باس منبع تغذیه دوم متصل می شود، خروجی جریان دوم آینه جریان اول به امیترهای ترکیبی ترانزیستورهای خروجی اول و چهارم متصل می شود و به خروجی جریان اول آینه سوم جریان، کلکتور ترانزیستور خروجی دوم به ورودی آینه جریان دوم متصل می شود که جریان خروجی آن به امیترهای ترکیبی ترانزیستور خروجی سوم و ششم متصل می شود و به خروجی جریان دوم آینه سوم جریان و کلکتور ترانزیستور خروجی پنجم به باس منبع تغذیه دوم متصل می شود. 3 w.p. f-ly، 5 بیمار.

3. نمودار عملکردی، علامت گرافیکی شرطی و جدول صدق یک رسیور کامل برای 3 ورودی.

4. رمزگشاهای خطی: عملکرد سوئیچینگ، UGO و مدار.

5. رمزگشاهای هرمی: عملکرد سوئیچینگ، UGO و مدار.

6. رمزگشاهای مستطیلی چند مرحله ای: عملکرد سوئیچینگ، UGO و مدار.

7. رمزگشاهای کلاک و یکپارچه.

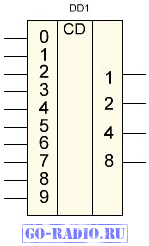

رمزگشا یک گره عملیاتی ترکیبی است که یک کلمه ورودی را در یکی از خروجی های خود به سیگنال تبدیل می کند.

بنابراین، رمزگشا گرهی است که در آن هر ترکیبی از سیگنال های ورودی مربوط به حضور یک سیگنال در یکی از خروجی ها است.

شکل 4 نمودار عملکردی رسیور را نشان می دهد که دارای n ورودی و 2 n-1 خروجی است.

روش سنتز رمزگشا

شرایط عملیاتی رمزگشا برای دو ورودی را می توان با جدول صدق نشان داد (جدول 3). تعداد خروجی های چنین رمزگشایی m = 2 2 = 4 است.

|

جدول 3 |

||||||||||||||||||||||||||||||||||||

|

جدول حقیقت رسیور 2x4

|

||||||||||||||||||||||||||||||||||||

توابع سوئیچینگ برای خروجی های رمزگشا مطابق این جدول صدق به صورت زیر نوشته می شود:

ما عبارات (4) را برای پیاده سازی بر اساس AND-NOT تبدیل می کنیم:

تصاویر مشروط از رسیور مورد استفاده در ساخت نمودارهای عملکردی، در شکل 7 نشان داده شده است، که در آن a نام عمومی رمزگشا است. ب - تعیین رمزگشای ماتریسی. ورودیهای رمزگشا با اعداد اعشاری نشاندهنده وزنهای باینری، خروجیها با تصاویر اعشاری از ترکیب کدهای مربوطه مشخص میشوند.

نام رسیور: 155 شناسه 1, 555شناسه 6 و غیره

3. تجزیه و تحلیل عملکرد رمزگذارها

هدف و اصل عملکرد انکودرها.

رسیدگی به موضوع با بازجویی از کارآموزان از روی صندلی و در تخته سیاه طبق طرح زیر انجام می شود:

وقت ملاقات

جدول درستی

روشهای سنتز مدارها

نمونه هایی از ساده ترین مدارها

موضوعات مورد بحث با کارآموزان

رمزگذارها:

1. هدف، منطق عملیات و طبقه بندی رمزگذارها.

2. نمودار عملکردی، تعیین گرافیک شرطی و جدول صدق رمزگذار برای n ورودی.

3. نمودار عملکردی، علامت گرافیکی شرطی و جدول حقیقت رمزگذار برای 4 ورودی.

4. سنتز انکودرها در پایه های مختلف.

5. اصول ساخت رمزگذارهای اولویت.

رمزگذار یک واحد عملکردی از یک کامپیوتر دیجیتال است و برای تبدیل یک کد واحد (کدی که در آن فقط یک متغیر یک مقدار واحد می گیرد) به کد موقعیتی (دودویی) طراحی شده است.

به عبارت دیگر، رمزگذار عملکردهایی را انجام می دهد که برعکس عملکرد رمزگشا هستند.

انکودر کامل دارای 2 متر ورودی و خروجی متر است. در این حالت، اگر یک سیگنال ورودی به یکی از مدارهای ورودی رمزگذار اعمال شود، در خروجی های آن کلمه ای مربوط به تعداد مدار برانگیخته تشکیل می شود.

سنتز یک رمزگذار معادل

اجازه دهید m=2، سپس تعداد ورودی های رمزگذار چهار می شود. جدول عملکرد چنین انکودری به شکل زیر خواهد بود (جدول 4).

|

جدول 4 |

||||||||||||||||||||||||||||||

|

جدول وضعیت رمزگذار 4x2

ترکیب رمزگذار اولویت اصل عملکرد رمزگذار را در نظر بگیرید "4 × 2" جدول حقیقت برای این رمزگذار در جدول ارائه شده است. 5. از جدول می توان دریافت که هنگام ساخت یک رمزگذار اولویت، از مجموعه های 1،2.4 و 8 استفاده می شود، برای مجموعه های باقی مانده، تابع یک مقدار بی تفاوت به دست می آورد - Ф. | ||||||||||||||||||||||||||||||

.

تراشه K176ID1، K561ID1

یک رسیور BCD ناقص دارای 4 ورودی برای دریافت کد باینری و 10 خروجی برای معادل اعشاری خود می باشد.

سطح فعال هر دو ورودی و خروجی بالا است. هنگامی که یک کد باینری در محدوده 8-15 به ریزمدار اعمال می شود، سطح منطقی پایینی روی همه خروجی ها تنظیم می شود (هیچ رمزگشایی انجام نمی شود). ریز مدار ورودی اضافی برای استروبینگ ندارد، با این حال، اگر دو رقم آخر اعشار را قربانی کنید، گسترش عمق بیت به راحتی قابل پیاده سازی است:

در نمودار بالا، معکوس ترین بیت کد ورودی به عنوان سیگنال بارق برای DD2 استفاده می شود. در عین حال، پایه های 4.5 (مهمترین رقم اعشار 8.9) ریز مدارها استفاده نمی شود و مدار یک رمزگشای کامل 4 بیتی BCD است.

در شکل زیر به دلیل استفاده از تراشه مجزا برای کنترل رسیورها، تعداد خروجی ها به 64 عدد (کد ورودی 6 بایت) افزایش یافته است.

——————————————-

تراشه K176ID2

رمزگشا - مبدل. طراحی شده برای تبدیل یک کد باینری به یک کد برای یک نشانگر هفت بخش. هیچ مداری برای کنترل اعشار در ریزمدار وجود ندارد. علاوه بر خود رمزگشا، ریز مدار دارای یک قفل است که به شما امکان می دهد داده های فعلی را ذخیره کنید.

دارای یک ورودی داده چهار رقمی و هفت خروجی برای اتصال نشانگر دیجیتال هفت بخش است. سطوح فعال ورودی و خروجی بالا هستند، اما در صورت لزوم، می توان آنها را با یک سیگنال در ورودی سرویس S معکوس کرد. هنگامی که سطح در این ورودی پایین است، سیگنال خروجی فعال بالا است، و هنگامی که "1" روشن است. S، کم است. این به شما امکان می دهد ماتریس های دیجیتال را هم با یک آند مشترک و هم با یک کاتد مشترک بدون اینورترهای اضافی متصل کنید. یکی دیگر از ورودی های سرویس K برای کنترل ماتریس خدمت می کند. "0" در ورودی K نمایش را فعال می کند، "1" ماتریس را خاموش می کند.

و سومین ورودی سرویس C برای بستن اطلاعاتی که به ورودی رمزگشا میآیند، عمل میکند. با سطح بالای C، سیگنال بلافاصله رمزگشایی شده و به نشانگر داده می شود. هنگامی که به "0" تغییر می کند، کد ورودی بسته می شود و بدون توجه به تغییرات ورودی نمایش داده می شود تا زمانی که سطح ورودی C دوباره بالا برود. حفظ کردن در سطح بالایی کاهش می یابد.

کلیدهای خروجی ریزمدار K176ID2 قادر به مقاومت در برابر جریان های اتصال کوتاه به صورت عددی برابر با سطح ولتاژ تغذیه (بر حسب میلی آمپر) هستند و بنابراین می توانند مستقیماً روی نشانگرهای LED (به عنوان مثال AL305، ALS324، ALS321) بدون جریان اضافی بارگذاری شوند. تقویت کننده ها

تراشه K176IDZ

آنالوگ کامل K176ID2 از نظر چیدمان پین و الگوریتم عملکرد. تفاوت در کلیدهای خروجی است که طبق طرح تخلیه باز ساخته شده اند. این به شما امکان می دهد آندهای نشانگرهای فلورسنت را که به ولتاژ نسبتاً بالا (تا 15 ولت) برای منبع تغذیه نیاز دارند، مستقیماً به خروجی رمزگشا متصل کنید. هنگام استفاده از یک ریزمدار در ارتباط با چنین نشانگرهایی، باید یک گزارش به ورودی سرویس S ارسال شود. "0".

——————————————-

تراشه 564ID4

رمزگشا - مبدل. طراحی شده برای تبدیل یک کد باینری به یک کد برای یک نشانگر هفت بخش (از جمله LCD). هیچ مداری برای کنترل نقطه اعشار وجود ندارد.

تفاوت اصلی با K176ID2 وجود خروجی سوم برای تغذیه سوئیچ های خروجی است که می تواند ولتاژهای تا 15 ولت را تحمل کند. تقویت کننده ویژه ای برای تغذیه ضد فاز LCD (ورودی S، خروجی P) وجود دارد. بیایید با استفاده از مثال اتصال نشانگر LCD IZHKTs1-1/18، کار آن را با جزئیات بیشتری در نظر بگیریم.

تفاوت اصلی با K176ID2 وجود خروجی سوم برای تغذیه سوئیچ های خروجی است که می تواند ولتاژهای تا 15 ولت را تحمل کند. تقویت کننده ویژه ای برای تغذیه ضد فاز LCD (ورودی S، خروجی P) وجود دارد. بیایید با استفاده از مثال اتصال نشانگر LCD IZHKTs1-1/18، کار آن را با جزئیات بیشتری در نظر بگیریم.

فرض کنید خود رمزگشا، مانند تمام اجزای قبلی دستگاه، با ولتاژ 5 ولت (پایین 16) تغذیه می شود و نشانگر LCD نیاز دارد. ولتاژ ACبا دامنه 15 ولت. برای تغذیه LCD به این صورت عمل می کنیم: 15 ولت را به پایه 7 (سومین پایه پاور) و به پایه 6 (ورودی S) سیگنال سطح TTL (5 ولت) و فرکانس می دهیم. از 100 هرتز این سیگنال بدون وارونگی به پین 1 (پایین P) می رسد، اما دامنه آن تا ولتاژ 15 ولت افزایش می یابد.

فرض کنید خود رمزگشا، مانند تمام اجزای قبلی دستگاه، با ولتاژ 5 ولت (پایین 16) تغذیه می شود و نشانگر LCD نیاز دارد. ولتاژ ACبا دامنه 15 ولت. برای تغذیه LCD به این صورت عمل می کنیم: 15 ولت را به پایه 7 (سومین پایه پاور) و به پایه 6 (ورودی S) سیگنال سطح TTL (5 ولت) و فرکانس می دهیم. از 100 هرتز این سیگنال بدون وارونگی به پین 1 (پایین P) می رسد، اما دامنه آن تا ولتاژ 15 ولت افزایش می یابد.

همان سیگنال در سطح فعال (log.1) سیگنال ها را از خروجی رمزگشا معکوس می کند (مشابه 176ID2,3). از آنجایی که کلیدهای خروجی ریز مدار توسط منبع 15 ولت تغذیه می شوند، سطح روی آنها از 0 به 15 ولت با فرکانس 100 هرتز و در پادفاز با سیگنال P تغییر می کند، بنابراین ولتاژ متناوب وجود خواهد داشت. در بخشهای فعال نشانگر، و 0 در بخشهای غیرفعال.

شایان ذکر است که رمزگشا کامل است - یعنی. قادر به نمایش نه تنها اعداد از 0 تا 9، بلکه کاراکترهای "L"، "H"، "P"، "A"، "-" به ترتیب کد باینری 10-14 است. کد 15 همه بخش ها را خاموش می کند.

اگرچه هدف اصلی ریز مدار کنترل نشانگر LCD است، قدرت خروجی آن برای احتراق ماتریس LED کافی است (با ولتاژ تغذیه تا 10 ولت - حتی بدون مقاومت های محدود کننده جریان). با تغییر سطح در ورودی S، می توان ماتریس ها را با آند مشترک و کاتد مشترک تغذیه کرد. خروجی R استفاده نمی شود.

——————————————-

تراشه 564ID5

رسیور به دلیل عدم وجود خروجی P با 564ID4 متفاوت است و دارای یک چفت چهار بیتی مشابه K176ID2 است.

رجیستر توسط ورودی C کنترل می شود: "1" - عبور مستقیم کد به رمزگشا و سپس به خروجی برای اتصال بخش های نشانگر، "0" - اطلاعات مربوط به نمایش. در این حالت، ریز مدار به تغییر کد باینری در ورودی پاسخ نمی دهد. هنگامی که سطح ورودی C کاهش می یابد، اطلاعات قفل می شود.

یکی از ویژگی های جالب رسیورهای K176ID2، K176ID3، 564ID4 و 564ID5 سیم کشی یکسان پایه های ورودی و خروجی به همین نام است.

——————————————-

تراشه KR1561ID6

یک بسته تراشه شامل دو رسیور BCD مستقل برای دو ورودی و چهار خروجی است. هر رمزگشا به یک ورودی بارق مجهز است.

سطوح ورودی و خروجی فعال زیاد است، ورودی دروازهای کم است. با "0" در ورودی S، رسیور کار می کند (معادل اعشاری کد ورودی در خروجی ظاهر می شود)، با "1" - همه خروجی ها روی "0" تنظیم می شوند.

سطوح ورودی و خروجی فعال زیاد است، ورودی دروازهای کم است. با "0" در ورودی S، رسیور کار می کند (معادل اعشاری کد ورودی در خروجی ظاهر می شود)، با "1" - همه خروجی ها روی "0" تنظیم می شوند.

تراشه KR1561ID7

آنالوگ کامل KR1561ID6 از نظر سیم کشی و الگوریتم عملکرد، اما هر دو رسیور دارای اینورتر در خروجی ها هستند (سطح خروجی فعال پایین است).

به دلیل وجود خروجیهای معکوس، این تراشه برای راهاندازی اکثر رمزگشاهای CMOS هنگامی که آبشاری هستند ایدهآل است. در شکل زیر در مدار کنترل گروه K561ID1 از یک رسیور ریز مدار KR1561ID7 استفاده شده است که تنها در پنج مورد امکان ساخت رسیور با 32 خروجی را فراهم کرده است.

به دلیل وجود خروجیهای معکوس، این تراشه برای راهاندازی اکثر رمزگشاهای CMOS هنگامی که آبشاری هستند ایدهآل است. در شکل زیر در مدار کنترل گروه K561ID1 از یک رسیور ریز مدار KR1561ID7 استفاده شده است که تنها در پنج مورد امکان ساخت رسیور با 32 خروجی را فراهم کرده است.

برای ساخت یک رسیور کامل برای 8 خروجی به تراشه KR1561ID6 (کد خروجی - مستقیم) یا KR1561ID7 (کد خروجی - معکوس)، فقط یک اینورتر اضافه کنید:

——————————————-

دستگاه های منطقی به دو دسته ترکیبی و ترتیبی تقسیم می شوند.

دستگاه نامیده می شود ترکیبی، اگر سیگنال های خروجی آن در نقطه ای از زمان به طور منحصر به فرد توسط سیگنال های ورودی که در آن نقطه از زمان رخ می دهند تعیین شوند.

در غیر این صورت، دستگاه را خودکار ترتیبی یا متناهی (اتومات دیجیتال، خودکار با حافظه) می نامند. دستگاه های متوالی لزوماً دارای عناصر حافظه هستند. وضعیت این عناصر به تاریخچه سیگنال های ورودی بستگی دارد. سیگنال های خروجی دستگاه های سریال نه تنها توسط سیگنال های موجود در ورودی ها تعیین می شود این لحظهزمان، بلکه وضعیت عناصر حافظه. بنابراین، پاسخ یک دستگاه سریال به سیگنال های ورودی خاص به تاریخچه عملکرد آن بستگی دارد.

در میان دستگاه های ترکیبی و ترتیبی، دستگاه های معمولی بیشترین استفاده را در عمل دارند.

رمزگذارها

رمزگذار یک دستگاه ترکیبی است که اعداد اعشاری را به یک سیستم اعداد باینری تبدیل میکند و به هر ورودی میتوان یک عدد اعشاری اختصاص داد و مجموعهای از سیگنالهای منطقی خروجی مربوط به یک کد باینری خاص است. رمزگذار گاهی اوقات "کدگذار" (از رمزگذار انگلیسی) نامیده می شود و برای مثال برای تبدیل اعداد اعشاری تایپ شده روی صفحه کلید یک کنترل پنل دکمه ای به اعداد باینری استفاده می شود.

اگر تعداد ورودیها آنقدر زیاد باشد که تمام ترکیبهای ممکن سیگنالهای خروجی در انکودر مورد استفاده قرار گیرد، آنگاه به چنین رمزگذار کامل، اگر نه همه، ناقص گفته میشود. تعداد ورودی ها و خروجی ها در یک رمزگذار کامل با رابطه n= 2 m مرتبط است که n تعداد ورودی ها و m تعداد خروجی ها است.

بنابراین، برای تبدیل کد صفحه کلید به یک عدد باینری چهار رقمی، کافی است فقط از 10 ورودی استفاده کنید، در حالی که تعداد کل ورودی های ممکن 16 خواهد بود (n = 2 4 = 16)، بنابراین رمزگذار 10 × 4 ( از 10 تا 4) ناقص خواهد بود.

نمونه ای از ساخت رمزگذار برای تبدیل کد واحد ده بیتی (اعداد اعشاری از 0 تا 9) به یک کد باینری را در نظر بگیرید. در این حالت، فرض می شود که سیگنال مربوط به یک واحد منطقی تنها به یک ورودی در یک زمان اعمال می شود. نمادچنین رمزگذار و جدول مطابقت کد در شکل نشان داده شده است. 3.35.

استفاده كردن این جدولمکاتبه، نوشتن عبارات بولی، از جمله در مجموع منطقی آن دسته از متغیرهای ورودی که با واحد برخی از متغیرهای خروجی مطابقت دارند. بنابراین، در خروجی، 1 یک "1" منطقی خواهد داشت، زمانی که "1" منطقی یا در ورودی X 1، یا X 3، یا X 5، یا X 7، یا X 9، یعنی y 1 \ باشد. u003d X 1 + X 3 + X 5 + X 7 + X 9

به طور مشابه، y 2 \u003d X 2 + X 3 + X 6 + X 7 y 3 \u003d X 4 + X 5 + X 6 + X 7 y 4 \u003d X 8 + X 9 به دست می آوریم

بیایید در شکل تصور کنیم. 3.36 طرح چنین رمزگذار با استفاده از عناصر OR.  در عمل اغلب از رمزگذار اولویت استفاده می شود. در این گونه انکودرها، کد عدد باینری مربوط به بالاترین عدد ورودی است که سیگنال "1" به آن اعمال می شود، یعنی اجازه ارسال سیگنال به چندین ورودی به انکودر اولویت دارد و کد عدد را تنظیم می کند. مربوط به بالاترین ورودی در خروجی است.

در عمل اغلب از رمزگذار اولویت استفاده می شود. در این گونه انکودرها، کد عدد باینری مربوط به بالاترین عدد ورودی است که سیگنال "1" به آن اعمال می شود، یعنی اجازه ارسال سیگنال به چندین ورودی به انکودر اولویت دارد و کد عدد را تنظیم می کند. مربوط به بالاترین ورودی در خروجی است.

اجازه دهید به عنوان مثال (شکل 3.37) یک رمزگذار با اولویت (انکودر اولویت) K555IVZ از سری ریزمدار K555 (TTLSh) را در نظر بگیریم.

رمزگذار دارای 9 ورودی معکوس است که با PR l , ... , PR 9 نشان داده می شود. مخفف PR مخفف "اولویت" است. انکودر دارای چهار خروجی معکوس B l , ... , B 8 . مخفف B به معنای "لاستیک" (از اتوبوس انگلیسی) است. اعداد مقدار سطح فعال (صفر) را در بیت مربوطه از عدد باینری تعریف می کنند. به عنوان مثال، B 8 به این معنی است که صفر در این خروجی با عدد 8 مطابقت دارد. بدیهی است که این یک رمزگذار ناقص است.

اگر همه ورودی ها یک منطقی داشته باشند، همه خروجی ها نیز یک منطقی دارند که با عدد 0 در کد معکوس (1111) مطابقت دارد. اگر حداقل یک ورودی صفر منطقی داشته باشد، وضعیت سیگنال های خروجی با بیشترین عدد ورودی که صفر منطقی دارد تعیین می شود و به سیگنال های ورودی با عدد کمتر بستگی ندارد.

به عنوان مثال، اگر ورودی PR 1 یک صفر منطقی باشد، و همه ورودی های دیگر یک واحد منطقی باشند، خروجی ها دارای سیگنال های زیر هستند: B 1 - 0، B 2 - 1، B 4 - 1، B 8 - 1، که با عدد 1 در کد معکوس (1110) مطابقت دارد.

اگر ورودی PR 9 یک صفر منطقی باشد، بدون در نظر گرفتن سایر سیگنال های ورودی، خروجی ها دارای سیگنال های زیر هستند: B 1 - 0، B 2 - 1، B 4 - 1، B 8 - 0 که مربوط به عدد است. 9 در کد معکوس (0110) .

هدف اصلی رمزگذار تبدیل شماره منبع سیگنال به یک کد است (به عنوان مثال، تعداد دکمه فشرده شده روی یک صفحه کلید خاص).

رمزگشاها

به آن دستگاه ترکیبی می گویند.که یک کد باینری n بیتی را به یک سیگنال منطقی تبدیل می کند که در خروجی ظاهر می شود که عدد اعشاری آن با کد باینری مطابقت دارد. تعداد ورودی ها و خروجی ها در رمزگشای به اصطلاح کامل با رابطه m= 2 n مرتبط است که n تعداد ورودی ها و m تعداد خروجی ها است. اگر رمزگشا از تعداد ناقص خروجی استفاده کند، چنین رمزگشایی ناقص نامیده می شود. بنابراین، برای مثال، یک رمزگشا با 4 ورودی و 16 خروجی کامل خواهد شد و اگر تنها 10 خروجی وجود داشته باشد، ناقص خواهد بود.

به عنوان مثال، اجازه دهید به رمزگشای K555ID6 از سری K555 بپردازیم (شکل 3.38).

رمزگشا دارای 4 ورودی مستقیم است که با A 1 , ... , A 8 نشان داده می شود. مخفف A مخفف "آدرس" (از آدرس انگلیسی) است. به این ورودی ها آدرس می گویند. اعداد مقادیر سطح فعال (یک) را در رقم مربوطه عدد باینری تعیین می کنند. رسیور دارای 10 خروجی معکوس Y 0 , ..., Y 9 . ارقام عدد اعشاری مربوط به عدد باینری داده شده را در ورودی ها تعریف می کنند. بدیهی است که این رمزگشا ناقص است.

مقدار سطح فعال (صفر) آن خروجی را دارد که تعداد آن برابر با عدد اعشاری است که توسط عدد باینری در ورودی تعیین می شود. به عنوان مثال، اگر همه ورودی ها صفرهای منطقی باشند، خروجی Y 0 یک صفر منطقی است و خروجی های باقی مانده یک منطقی است. اگر ورودی A 2 یک منطقی باشد، و ورودی های باقیمانده یک صفر منطقی باشد، خروجی Y 2 یک صفر منطقی است و خروجی های باقیمانده یک منطقی است. اگر ورودی یک عدد باینری بزرگتر از 9 باشد (به عنوان مثال، همه ورودی ها یک هستند که با عدد باینری 1111 و عدد اعشاری 15 مطابقت دارد)، پس همه خروجی ها یک عدد منطقی هستند.

رمزگشا یکی از ابزارهای منطقی پرکاربرد است. برای ساخت دستگاه های ترکیبی مختلف استفاده می شود.

رمزگذارها و رمزگشاهای در نظر گرفته شده نمونه هایی از ساده ترین مبدل های کد هستند.

مبدل کد

در حالت کلی به دستگاه هایی گفته می شود که برای تبدیل یک کد به کد دیگر طراحی شده اند و اغلب تبدیل کدهای غیر استاندارد را انجام می دهند. مبدل های کد با X/Y نشان داده می شوند.

ویژگی های اجرای مبدل را در مثال مبدل یک کد سه عنصری به یک کد پنج عنصری در نظر بگیرید. فرض کنید لازم است جدول مطابقت کد نشان داده شده در شکل را پیاده سازی کنید. 3.39.

در اینجا N عدد اعشاری مربوط به کد باینری ورودی را نشان می دهد. مبدل های کد اغلب یک طرح رمزگشا-رمزگذار ایجاد می کنند. رمزگشا کد ورودی را به مقداری اعشار تبدیل می کند و سپس رمزگذار کد خروجی را تولید می کند. نمودار مبدل ایجاد شده بر اساس این اصل در شکل نشان داده شده است. 3.40، که در آن از رمزگذار دیود ماتریسی استفاده می شود. اصل عملکرد چنین مبدل بسیار ساده است. به عنوان مثال، هنگامی که یک "O" منطقی در همه ورودی های رمزگشا وجود دارد، یک "1" منطقی در خروجی 0 ظاهر می شود که منجر به ظاهر شدن "1" در خروجی های 4 و 5 می شود، یعنی، خط اول جدول مطابقت کد پیاده سازی شده است.

انتشارات صنعت تعداد زیادی رمزگذار، رمزگشاو مبدل های کد مانند رمزگشای 4x16 با استروبینگ (K555IDZ)، مبدل کد برای کنترل ماتریس LED 7x5 (K155ID8)، مبدل کد برای کنترل نشانگر شماره گیری (K155ID15) و غیره.

یکی از عناصر بسیار مهم فناوری دیجیتال و به ویژه در رایانه ها و سیستم های کنترلی، رمزگذارها و رمزگشاها هستند.

وقتی کلمه رمزگذار یا رمزگشا را می شنویم، عباراتی از فیلم های جاسوسی به ذهنمان خطور می کند. چیزی مانند: رمزگشایی ارسال و رمزگذاری پاسخ.

هیچ اشکالی در این مورد وجود ندارد، زیرا ماشین های رمزگذاری ساکنان ما و کشورهای خارجی از رمزگذار و رمزگشا استفاده می کنند.

رمزگذارها

بنابراین، رمزگذار (رمزگذار) است دستگاه الکترونیکی، در این مورد، یک ریزمدار که کد یک سیستم عددی را به کد یک سیستم دیگر تبدیل می کند. بیشترین کاربرد در الکترونیک رمزگذارهایی هستند که یک کد اعشاری موقعیتی را به باینری موازی تبدیل می کنند. به این ترتیب می توان رمزگذار را در نمودار مدار نشان داد.

به عنوان مثال، تصور کنید که یک ماشین حساب معمولی را در دست گرفته ایم که اکنون هر دانش آموزی از آن استفاده می کند.

از آنجایی که تمام اقدامات در ماشین حساب با اعداد باینری انجام می شود (مبانی الکترونیک دیجیتال را به یاد بیاورید)، پس از صفحه کلید یک رمزگذار وجود دارد که اعداد وارد شده را به شکل باینری تبدیل می کند.

تمام دکمه های ماشین حساب به یک سیم مشترک متصل می شوند و با فشار دادن مثلاً دکمه 5 در ورودی انکودر، بلافاصله شکل باینری این عدد را در خروجی آن به دست می آوریم.

البته رمزگذار ماشین حساب تعداد ورودی بیشتری دارد، زیرا علاوه بر اعداد باید برخی از نمادهای دیگر عملیات حسابی نیز در آن وارد شود، بنابراین نه تنها اعداد به صورت باینری، بلکه دستورات نیز از خروجی ها حذف می شوند. از رمزگذار

اگر ساختار داخلی رمزگذار را در نظر بگیریم، به راحتی می توان مطمئن شد که بر روی ساده ترین عناصر منطقی پایه ساخته شده است.

در تمام دستگاه های کنترلی که بر اساس منطق باینری کار می کنند، اما برای راحتی اپراتور دارای صفحه کلید اعشاری هستند، از رمزگذارها استفاده می شود.

رمزگشاها

رسیورها متعلق به یک گروه هستند، فقط آنها دقیقا برعکس عمل می کنند. آنها باینری موازی را به اعشاری موقعیتی تبدیل می کنند. نام گرافیکی مشروط در نمودار ممکن است به شرح زیر باشد.

یا اینجوری

با صحبت کاملتر در مورد رمزگشاها، شایان ذکر است که آنها می توانند کد باینری را به سیستم های اعداد مختلف (اعشاری، هگزادسیمال و غیره) تبدیل کنند. همه اینها به هدف و هدف خاص ریز مدار بستگی دارد.

ساده ترین مثال. شما بیش از یک بار یک نشانگر دیجیتال هفت بخش دیده اید، به عنوان مثال یک LED. ارقام اعشاری و اعدادی را نشان می دهد که از دوران کودکی به آنها عادت کرده ایم (1، 2، 3، 4...). اما همانطور که می دانید الکترونیک دیجیتال با اعداد باینری کار می کند که ترکیبی از 0 و 1 هستند. احتمالاً قبلاً حدس زده اید که رمزگشا این کار را انجام داده است.

اگر مدار ساده ای را که از یک تراشه رمزگشا تشکیل شده است جمع آوری کنید، می توان کار رمزگشا را به صورت زنده ارزیابی کرد. K176ID2و یک نشانگر LED هفت بخش که به آن "هشت" نیز می گویند. به نمودار نگاهی بیندازید، درک نحوه عملکرد رمزگشا آسان تر است. برای مونتاژ سریع مدار می توان از تخته نان بدون لحیم استفاده کرد.

برای مرجع. ریزمدار K176ID2 برای کنترل یک نشانگر LED 7 قسمتی ساخته شده است. این تراشه قادر به تبدیل کد باینری از 0000 قبل از 1001 ، که مربوط به ارقام اعشاری از 0 تا 9 (یک دهه) است. بقیه، ترکیبات قدیمی تر به سادگی نمایش داده نمی شوند. نتیجه گیری C، S، K کمکی هستند.

تراشه K176ID2 دارای چهار ورودی (1، 2، 4، 8) است. گاهی اوقات به آنها نیز اشاره می شود D0-D3. به این ورودی ها یک کد باینری موازی داده می شود (مثلاً 0001). در این حالت کد باینری دارای 4 بیت است. ریز مدار کد را طوری تبدیل می کند که خروجی های ( a-g) سیگنال هایی ظاهر می شوند که ارقام اعشاری و اعدادی را تشکیل می دهند که در نشانگر هفت قسمتی به آنها عادت کرده ایم. از آنجایی که رسیور K176ID2 قادر به نمایش ارقام اعشاری در محدوده 0 تا 9 است، ما فقط آنها را روی نشانگر خواهیم دید.

4 سوئیچ ضامن (S1 - S4) به ورودی های رسیور K176ID2 متصل می شوند که با کمک آنها می توان یک کد باینری موازی را روی رسیور اعمال کرد. به عنوان مثال، هنگام بستن سوئیچ ضامن S1یک واحد منطقی به خروجی 5 میکرو مدار اعمال می شود. اگر مخاطبین سوئیچ ضامن را باز کنید S1- این با یک صفر منطقی مطابقت دارد. با کمک سوئیچ های ضامن می توانیم به صورت دستی منطق 1 یا 0 را در ورودی های ریزگرد قرار دهیم، فکر کنم با این همه چیز مشخص است.

نمودار نشان می دهد که چگونه کد 0101 به ورودی های رمزگشا DD1 اعمال می شود. نشانگر LEDعدد 5 نمایش داده می شود.اگر فقط کلید S4 بسته باشد، عدد 8 روی نشانگر نمایش داده می شود.برای نوشتن یک عدد از 0 تا 9 در اینچ کد باینریچهار رقم کافی است: a 3 * 8 + a 2 * 4 + a 1 * 2 + a 0 * 1، جایی که a 0 - a 3، اعدادی از سیستم اعداد (0 یا 1) هستند.

بیایید عدد 0101 را به صورت اعشاری نشان دهیم 0101 = 0*8 + 1*4 + 0*2 + 1*1 = 4 + 1 = 5 . حالا بیایید به نمودار نگاه کنیم و ببینیم که وزن رقم مطابق با عددی است که 0 یا 1 در فرمول ضرب شده است.

رمزگشا مبتنی بر فناوری TTL - K155ID1 در یک زمان برای کنترل یک نشانگر دیجیتال تخلیه گاز از نوع IN8، IN12 استفاده شد که در دهه 70 تقاضای زیادی داشت، زیرا نشانگرهای LED ولتاژ پایین هنوز بسیار نادر بودند.

همه چیز در دهه 80 تغییر کرد. خرید آزادانه ماتریس های LED هفت بخش (نشانگرها) و رونق در مونتاژ ساعت های الکترونیکی در بین آماتورهای رادیویی امکان پذیر بود. خانگی ساعت دیجیتالبرای خانه تنها تنبل جمع آوری نشده است.