20.04.2002 Михаил Кузьминский

В статье проанализирована предложенная компанией AMD архитектура x86-64 и рассмотрены некоторые ее достоинства и недостатки по сравнению с другими 64-разрядными архитектурами, в первую очередь Intel/HP IA-64. Дан краткий обзор микроархитектуры процессоров AMD Hammer, в которых впервые будет реализована архитектура x86-64. Характеристики Hammer сопоставлены с другими современными и перспективными высокопроизводительными процессорами.

Если все высокопроизводительные микропроцессоры RISC-архитектуры, выпускающиеся с конца 90-х годов, являются 64-разрядными (Сompaq/DEC Alpha, SGI/MIPS R1x000, IBM Power, HP PA-8x00, Sun UltraSPARC), то основные CISC-архитектуры (Intel x86, IBM S/390) переходят от 32 к 64 разрядам только сейчас (IA-64 , IBM z/Architecture ).

Переход от S/390 к z/Architecture выглядит достаточно естественным расширением, в то время как переход от x86 (ныне IA-32) к IA-64 означает, по сути, полную смену системы команд. Думаю, это обусловлено тем, что х86 начала свое историческое развитие с 8-ми, а затем 16-разрядных систем. Поэтому остававшаяся по соображениям совместимости относительно статичной в течение очень многих лет система команд со временем стала довольно «неестественной» с точки зрения других 32-разрядных процессоров.

Итак, если IBM перешла к 64-разрядной платформе эволюционным путем, переход от х86 к IA-64 - это революция; совместимость обеспечивается лишь путем аппаратной эмуляции. Пока непонятно, хочет ли Intel в будущем вообще отказаться от IA-32 в пользу IA-64, но то, что все программное обеспечение для IA-64 нужно как минимум перетранслировать - не говоря уже о дальнейшей оптимизации под IA-64 - это кажется ясным. Очевидно, переход на платформу IA-64 займет немало времени и будет стоить весьма дорого.

Совершенно другим путем пошла компания AMD. Она предложила собственную модернизацию архитектуры x86, которая (как и в случае с IBM) является естественным эволюционным развитием - подобно тому, как х86 в свое время была модернизирована с 16 до 32 разрядов.

Почему же 32-разрядные CISC-платформы становятся 64-разрядными только сейчас, хотя потребности в 64-разрядных приложениях стали достаточно большими уже несколько лет назад? Кроме уже отмеченной сложности перехода (очевидной в случае IA-64 и z/Architecture) следует указать и на резкое удешевление оперативной памяти при одновременном росте емкости модулей памяти. В результате 4-гигабайтный предел емкости для 32-разрядных систем оказывается вполне достижим уже в современных ПК. Так почему бы не поднять производительность ПК-сервера за счет установки дополнительной памяти, коль скоро это становится не так дорого?

Архитектура х86-64

Представляется, что отличия архитектуры х86-64 от IA-32 даже меньше, чем отличия IBM z/Architecture от S/390. В AMD всячески стараются подчеркнуть, что внесенные изменения минимальны , хотя анализ полного описания позволяет выявить достаточное количество мелких нюансов, касающихся, правда, в первую очередь разработчиков системного программного обеспечения, а не приложений.

Ключевых же изменений х86-64 по сравнению с сегодняшним состоянием IA-32 действительно не так много и они в определенном смысле аналогичны тем, которые были внесены при переходе от 16-ти к 32-разрядной архитектуре х86. Эти нововведения включают:

- 64-разрядные виртуальные адреса (в конкретной реализации возможна меньшая разрядность);

- "плоское" (flat) адресное пространство с единым пространством кодов, данных и стека;

- 64-разрядный счетчик команд (RIP);

- режим адресации относительно счетчика команд;

- расширение регистров общего назначения (целочисленных) до 64 разрядов;

- добавление 8 новых регистров общего назначения (R8-R15);

- добавление еще 8 SSE-регистров XMM8-XMM15 разрядностью 128 (соответствует предложенному Intel расширению SSE2).

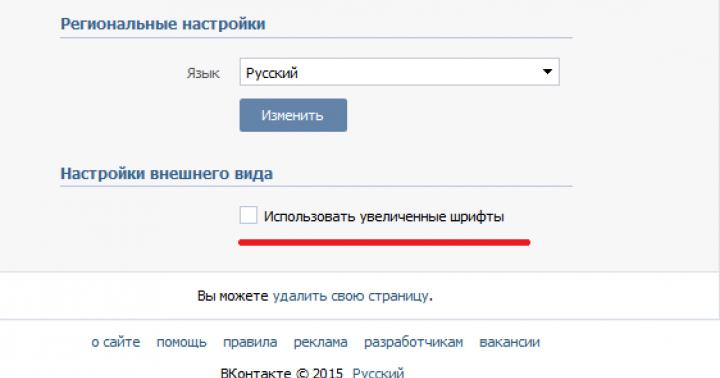

| Рис. 1. Пример расширения регистров общего назначения |

«Указания» на дополнительные регистры и размеры данных вводятся как префикс команд. Набор основных регистров x86-64 представлен на рис. 1. Регистры являются 64-разрядными, за исключением 32-разрядного регистра EFLAGS, 128-разрядных регистров ХММ и 80-разрядных регистров с плавающей запятой ST. Архитектура x86-64 включает, в частности, SSE2-расширения IA-32, представленные в Pentium 4.

На рис. 1 показано, каким образом расширены новые 64-разрядные регистры относительно 32-разрядных регистров в IA-32. Для выполнения 16-разрядных операций регистр А адресуется как АХ, для выполнения 32-разрядных операций - как EAX, а для выполнения 64-разрядных - как RAX. При выполнении 32-разрядных операций, в которых целочисленный регистр служит регистром результата, 32-разрядные значения дополняются нулями до 64-разрядных. 8-ми и 16-разрядные операции над целочисленными регистрами сохраняют старшие разряды неизменными .

Для работы с 64-разрядной адресацией в х86-64 введен режим Long Mode (назовем его «расширенным режимом»). Режим работы задается управляющим битом LMA (Long Mode Active), который взводится, если микропроцессор переходит в расширенный режим. В расширенном режиме регистры сегментов ES, DS, FS, GS, SS игнорируются. В регистре CS (дескриптор сегмента кода) находятся биты, уточняющие режимы работы микропроцессора.

В х86-64 расширенный режим имеет два «подрежима»: 64-разрядный режим и режим совместимости. В режиме совместимости обеспечивается двоичная совместимость с 16-ти и 32-разрядными режимами х86. Выбором подрежима управляет бит CS.L. Если он установлен в 0 (режим совместимости), 64-разрядная операционная система, работая в режиме LMA, может выполнять старые 16-ти и 32-разрядные х86-приложения. За выбор размера операнда отвечает бит CS.D.

По умолчанию, в 64-разрядном режиме (взведен бит LMA, CS.L = 1, CS.D = 0) применяются 64-разрядные адреса и 32-разрядные операнды. Используя префиксы команд, можно изменить размер операнда (установить его равным 64 или 16 разрядам), а также изменить размер адреса (установить равным 32 разрядам). В таблицах 1 и указаны основные допустимые типы режимов процессора и режимов работы операционной системы и приложений.

Приведенные данные показывают, что процессоры с архитектурой х86-64 могут работать как с уже существующими 16-ти и 32-разрядными, так и с новыми 64-разрядными операционными системами. В последнем случае в режиме совместимости возможно одновременное выполнение 16-ти и 32-разрядных приложений благодаря установке соответствующих бит в индивидуальных сегментах кодов. При этом 32-разрядные приложения могут использовать первые 4 Гбайт виртуальной памяти.

Для выяснения особенностей микропроцессоров с архитектурой х86-64 необходимо анализировать регистры EAX/EBX/ECX/EDX, в которые помещаются результаты выполнения команды CPUID (при ее вызове, как и ранее, в EAX нужно положить 8000_0000h). Если 29-й бит в EAX равен 1, микропроцессор работает в расширенном режиме.

В х86-64 имеется еще ряд интересных усовершенствований, особенно для задач системного программирования. В качестве примера отметим введение нового регистра приоритета задач TPR, который используется для ускорения обработки прерываний. За подробностями отсылаем читателей к описанию x86-64 .

Микроархитектура Hammer

Процессор Athlon относится к седьмому поколению архитектуры x86, реализованному компанией AMD. Первые процессоры, в которых будет реализована архитектура х86-64, получили кодовое название Hammer и представляют собой восьмое поколение х86-процессоров от AMD. В них продолжилась тенденция определенного отхода системы команд процессоров AMD от полной тождественности с Intel x86. Однако если прежде отличия были связаны с введением AMD новых команд 3DNow!, то теперь Hammer, в отличие от х86, становится 64-разрядным. В Hammer применяются 64-разрядные внутренние «шины», используемые для обмена данными. Виртуальное адресное пространство является 48-разрядным, а пространство физических адресов - 40-разрядным.

Целями AMD при создании данного семейства микропроцессоров, помимо очевидной цели поддержи х86-64, были :

- по возможности минимальное увеличение площади микросхемы;

- обеспечение возможностей дальнейшего беспрепятственного роста тактовой частоты процессора на современном уровне развития технологий;

- обеспечение при этом ускорения как 64-разрядных, так и 32-разрядных приложений. Общее представление о микроархитектуре Hammer дает рис. 2 .

В современных наиболее мощных RISC-процессорах имеется тенденция интеграции в микропроцессор кэш-памяти второго уровня большой емкости. Как Intel, так и AMD в своих высокопроизводительных процессорах не так давно уменьшили емкость кэша второго уровня с 512 Кбайт до 256 Кбайт, одновременно интегрировав его в процессор. Но в Pentium 4 Northwood разработчики Intel вновь расширили кэш второго уровня до 512 Кбайт. Соответствующие официальные данные по Hammer отсутствуют; между тем емкость кэша второго уровня может сильно повлиять на его производительность. По мнению некоторых аналитиков, емкость кэша второго уровня в старших моделях Hammer будет вчетверо выше, чем у современных моделей Athlon.

Буферы быстрой переадресации в данном процессоре по сравнению с Athlon модернизированы. I-TLB первого уровня в Hammer имеет емкость 40 строк (на 16 строк больше, чем раньше) и является полностью ассоциативным. У D-TLB первого уровня те же характеристики. Оба буфера TLB обеспечивают работу со страницами памяти емкостью 4 Кбайт, 2 Мбайт и 4 Мбайт.

I-TLB второго уровня, как и D-TLB второго уровня, содержат по 512 строк (вдвое больше, чем в Athlon) и являются 4-канальными частично-ассоциативными. Как указано в , TLB обладают уменьшенными по сравнению с Athlon задержками. Кроме того, аппаратно реализована возможность разделения TLB между несколькими процессами (для этого предусмотрен специальный «фильтр поджога»).

Очевидно, что увеличение емкости TLB и поддержка страниц памяти больших размеров ориентированы на использование в системах с большой емкостью памяти; это естественно для 64-разрядных приложений. Возможность разделения TLB, в свою очередь, может повышать производительность многозадачных операционных систем на серверных приложениях.

Традиционным направлением совершенствования современных микропроцессоров является улучшение точности предсказания переходов. В Hammer имеется массив адресов переходов емкостью 2К строк, а также таблица глобальной истории переходов, содержащая 16К 2-разрядных счетчиков (в 4 раза больше, чем у Athlon). Наконец, емкость стека адресов возврата - 12 строк.

Важной особенностью, способствующей повышению производительности, является интеграция в Hammer контроллера оперативной памяти. Это позволяет и пропускную способность увеличить, и уменьшить задержки. Данные характеристики будут автоматически улучшаться с ростом частоты процессора. Для архитектуры х86 эта особенность уникальна; Compaq же в своих новейших процессорах Alpha EV7 идет по такому же пути.

Контроллер памяти будет иметь интерфейс шириной 8 или 16 байт к оперативной памяти типа DDR. В последнем случае речь идет о двухканальной DDR-памяти, по 4 регистровых DIMM-модулей на канал. AMD обещает поддержку как регистровых, так и небуферизованных DIMM-модулей для памяти типа DDR PC1600/PC2100/PC2700. При использовании PC2700 в двухканальном варианте пропускная способность оперативной памяти достигнет значения 5,3 Гбайт/с. Для сравнения, процессор Intel McKinley, который вследствие особенностей архитектуры IA-64 нуждается в повышенной пропускной способности оперативной памяти, будет снабжен системной шиной лишь немного быстрее - 6,4 Гбайт/с.

Применение при построении систем на базе Hammer технологии HyperTransport позволит уменьшить задержки оперативной памяти с ростом тактовой частоты микропроцессора, автоматически повышать пропускную способность так называемых snoop-проб при поддержании когерентности кэша в многопроцессорных системах с ростом частоты и, наконец, масштабировать пропускную способность и емкость оперативной памяти с ростом числа процессоров в системе.

Фронтальная часть конвейера включает выборку и декодирование команд (рис. 2). Логика работы этих стадий в Hammer усложнилась, возросла степень упаковки команд, направляемых декодерами к планировщикам. По сравнению с Athlon длина этой части конвейера возросла на 2 стадии, так что общая длина целочисленного конвейера Hammer равна 12, а конвейера с плавающей запятой - 17 стадий . По мнению разработчиков, это должно способствовать беспроблемному росту тактовой частоты процессора по мере совершенствования технологии изготовления. Первоначально планируется использовать 0,13-микронную технологию «кремний-на-изоляторе»; во второй половине 2003 года планируется переход к 0,09 мкм.

Надо отметить, официальные данные о площади, занимаемой Hammer, отсутствуют. Между тем, появились сообщения о том, что процессор ClawHammer будет обладать площадью всего 105 мм 2 , в то время как Athlon/Palomino, выполненный по той же технологии на 0,13 мкм - 80 мм 2 . Для сравнения, площадь McKinley, судя по представленным Intel на международной конференции ISSCC ?2002 данным, - 464 мм 2 .

Недостатки и достоинства длинных конвейеров хорошо известны: легче увеличивать тактовую частоту, но больше потери на перезаполнения конвейера, в частности, при неправильном предсказании перехода. Интересно сопоставить длину конвейера Hammer с другими современными микропроцессорами Intel. В Pentium 4, добившемся рекордных частот в 2,2 ГГц, по сравнению с Pentium III длина конвейера благодаря использованию технологии HyperPipeline возросла вдвое - до 20 стадий. Это имело ту же цель - обеспечение беспрепятственного роста тактовой частоты; в Intel говорят о 10 ГГц к 2005-2006 годам. В McKinley длину конвейера, наоборот, сократили - до 8 стадий против 10 в Itanium, но его ожидаемая частота - 1 ГГц.

Производительность, как известно, зависит не только от тактовой частоты, но и от числа реально выполняемых за такт команд. По утверждению AMD , в Hammer число это повысится. А вот на какой частоте будет работать Hammer, не сообщается; можно предположить, что этот показатель окажется около 2 ГГц.

Построение систем на базе Hammer

Мы рассмотрели основные особенности микроархитектуры Hammer, за исключением применения технологии HyperTransport. Она используется в Hammer как для подсоединения системы ввода-вывода, так и для организации межпроцессорных связей. Фактически благодаря встроенному в Hammer контроллеру оперативной памяти и применению технологии HyperTransport в Hammer интегрированы основные функции набора микросхем (точнее говоря, северного моста).

Собственно технология HyperTransport развивается одноименным консорциумом, основанном компаниями AMD, Sun Microsystems, Cisco Systems, Nvidia, Transmeta и Apple Computer. Думаю, потребности в разработке такой технологии диктовались в первую очередь возникновением узких мест в системах ввода/вывода в ПК и вообще использованием шин PCI, характеристики производительности которых не удовлетворяют требованиям современных высокопроизводительных сетевых плат и каналов ввода/вывода для жестких дисков.

Каналы HyperTransport при том же числе контактов, что и PCI, обеспечивают гораздо более высокую пропускную способность: пиковая величина ее составляет 3,2 Гбайт/с. Каналы HyperTransport имеют ширину 16 разрядов, обеспечивая 1,6 миллиардов передач в секунду в каждом направлении. HyperTransport позволяет осуществить соединения типа «точка-точка» с полнодуплексным режимом и расщепленной обработкой транзакций. Такие характеристики данной технологии позволяют использовать ее и для организации межпроцессорных связей; в последнем случае, в отличие от ввода/вывода, применяется вариант HyperTransport с поддержанием когерентности кэша.

|

| Рис. 3. Схема построения 4-процессорных систем на базе Hammer |

Процессоры Hammer имеют по три порта для каналов HyperTransport (рис. 3), плюс порт к контроллеру оперативной памяти. Поэтому в состав процессора введен коммутатор ХВОХ , который маршрутизирует команды и данные между этими портами и интерфейсом системных запросов (очередь SRQ). Эта очередь имеет длину 24 строки, а очередь к DRAM-контроллеру (Memory Command Queue) - 20 строк . Для связи с подсистемой ввода/вывода в Hammer используется мост Host Bridge, тогда два других канала HyperTransport задействуются в межпроцессорных обменах.

Единственное, что не встроено в Hammer - это интерфейс с AGP; поэтому микросхеме, занимающей место северного моста (рис. 4), необходимо поддерживать этот интерфейс. Предполагается, что это будет AGP 8X.

С этой микросхемой соединен южный мост. Хотя AMD традиционно предлагает набор микросхем для своих новых процессоров и сделает это, очевидно, и для Hammer, уже известно о разработках южного моста для этого процессора компаниями Nvidia и VIA Technologies. Кроме того, в многопроцессорных системах ожидается применение «шлюза» между HyperTransport и PCI-X ; возможно применение аналогичных средств для других стандартов ввода/вывода.

|

|

Рис. 4. Архитектура многопроцессорных систем на базе Hammer А) однопроцессорная система Б) двухпроцессорная система В) четырехпроцессорная система |

Схемы, представленные на рис. 4, демонстрируют эффективность построения многопроцессорных систем на базе Hammer. В таких компьютерах с ростом числа процессоров масштабируются не только вычислительная мощность, емкость и пропускная способность оперативной памяти, но и ресурсы подсистемы ввода/вывода. Так, в 8-процессорной системе доступными будут 64 (8х8) DIMM-модуля (до 128 Гбайт) и 4 канала HyperTransport с суммарной пропускной способностью 25 Гбайт/с для дуплексной передачи.

AMD анонсировала набор микросхем серии 8000, который будет доступен в четвертом квартале 2002 года. Он включает микросхемы AMD-8151 (организует интерфейс с AGP 3.0), AMD-8131 (мост от HyperTransport к PCI-X) и AMD-8111 (концентратор ввода/вывода, обеспечивает поддержку PCI-32/33 МГц, USB, IDE и т.п.).

Интересно организовано обеспечение когерентности кэша с использованием каналов HyperTransport при числе процессоров от 4 и выше: в обработке соответствующих запросов участвуют несколько образуемых каналами HyperTransport путей между процессорами , что способствует ускорению работы. В принципе возможно построение систем с числом процессоров Hammer, большем 8, но для этого понадобится коммутатор HyperTransport.

Задержки при работе с локальной (ближней к микропроцессору) оперативной памятью незначительно возрастают при обращении к «удаленной» памяти. На ненагруженной 4-процессорной системе задержка равна 140 нс, на аналогичной 8-процессорной системе - 160 нс. Это позволяет говорить об архитектуре SMP, а не ссNUMA. Вместе с тем применение технологии коммутации вместо системных шин позволяет достигнуть высоких показателей и по пропускной способности оперативной памяти. Для операций типа копирования она составляет 8 Гбайт/с для 4-процессорной системы, что, по утверждению AMD, существенно выше, чем в шинных архитектурах .

В ожидании Hammer

Начало продаж Hammer начнется ориентировочно в третьем квартале 2002 года. Первым микропроцессором данного семейства станет ClawHammer, ориентированный на одно- и двухпроцессорные системы; затем появится SledgeHammer. Хотя по сути Hammer должен вступить в конкуренцию с микропроцессорами архитектуры IA-64 (к тому времени должен появиться и McKinley), можно предположить, что в будущем Hammer окажется в состоянии вытеснить Athlon на всем спектре применений (но на это может уйти не один год). Это означает также, что Hammer может стать конкурентом Pentium 4.

Кроме существующих 32-разрядных операционных систем, на 64-разрядную архитектуру Hammer переносятся NetBSD, FreeBSD и Linux, а также современные разновидности Windows.

Преимуществами х86-64 и Hammer являются:

- совместимость с 16-ти и 32-разрядными приложениями при высоком уровне производительности выполнения;

- относительная (по сравнению с IA-64) простота перехода от х86 и соответственно отсутствие необходимости чрезмерных финансовых затрат на этот переход;

- меньший риск неудачи новой архитектуры;

- простота разработки и реализации;

- небольшая площадь, что повышает выход годных и облегчает масштабирование по тактовой частоте.

Можно сказать, что благодаря выбранному «эволюционному» подходу можно более надежно предсказать успехи в росте производительности.

Перечисленные преимущества сопровождаются и некоторыми потенциально «опасными» для AMD моментами. Архитектура х86-64 не столь «революционна», как IA-64; более того, число регистров по сравнению с современными RISC-процессорами не выглядит достаточно большим, что, как известно, усложняет оптимизацию программ.

AMD придется продемонстрировать, что высоты производительности достижимы главным образом за счет технологии (и соответствующего роста тактовой частоты), но не за счет архитектуры. Пока это успешно доказывает, в частности, Pentium 4, а вот обратных доказательств со стороны IA-64 пока не получено.

Для создания 64-разрядных приложений понадобится разработать оптимизирующие компиляторы, информация о которых пока отсутствует. Наконец, современная компьютерная индустрия стоит на пороге выбора новых стандартов ввода/вывода - Infiniband, PCI-X, 3GIO, HyperTransport. Жесткая привязка к технологии HyperTransport способна вывести AMD в лидеры, но и несет в себе определенный риск.

Что касается областей применения, где нужна 64-разрядная архитектура, то AMD указывает в первую очередь на СУБД, САПР, средства создания цифрового «содержания». По мнению автора, процессоры Hammer могут оказаться активно востребованы на быстро растущем сегменте рынка - кластерах (в первую очередь, Linux-кластерах) с двухпроцессорными узлами.

В настоящее время очень популярной является такая платформа на базе Athlon MP; аналогичные системы на базе Pentium 4/Xeon стоят заметно дороже. При сохранении такого соотношения AMD сможет рассчитывать на успех и в этой части рынка.

Работа поддержана РФФИ, проект 01-07-90072.

Литература

- Михаил Кузьминский, "Краткий обзор IA-64" . "Открытые системы", 1999, № 9-10

- Михаил Кузьминский, "Микроархитектура Itanium" . Открытые системы, № 9, 2001

- Михаил Кузьминский, "Z-архитектура. Современные 64-разрядные мэйнфреймы IBM" . "Открытые системы", 2001, № 10

- "x86-64 Technology White Paper", 2001, AMD

- "AMD 64-Bit Technology. The AMD x86-64 Architecture Programmers Overview", AMD, 2001, Jan.

- "AMD Eight-Generation Processor Architecture. White Paper", AMD, 2001, Oct.

- F. Weber, "AMD Next Generation Microprocessor Architecture", Microprocessor Forum, 2001

Михаил Кузьминский ([email protected]) - старший научный сотрудник Центра компьютерного обеспечения ИОХ РАН (Москва).

Автор достаточно рисковал, включая этот материал в учебное пособие, так как публикуемые в наше время сведения о конкретных моделях микропроцессоров устаревают, находясь ещё под печатным станком. Однако ради полноты картины о современных 64-разрядных архитектурах эта глава оправдывает своё присутствие в настоящем пособии.

10.1 Архитектура Intel Core 2

Восьмое поколение процессоров Intel, получившее название Core 2, без доли сомнения можно назвать революционным.

Инженеры Intel после довольно продолжительного отставания от AMD не придумали кардинально новую архитектуру. Как водится, все новое – это хорошо забытое старое. В основу Conroe легли наработки мобильного Pentium M – процессора настолько успешного, что некоторые производители стали применять его не только для переносных компьютеров, но и для настольных рабочих станций. В свою очередь, Pentium M тоже появился не на пустом месте. Его прародителем является Pentium III, который, как известно, был эволюционным продолжением Pentium Pro.

Соответствующая эволюционная цепочка выглядит следующим образом: Pentium Pro Pentium II Pentium III Pentium M Core 2.

Данный случай является примером, когда шаг назад стал значительным шагом вперед. Если очень сильно абстрагироваться от деталей, то разработчики из Intel сделали следующее. Создали к 1995 году довольно успешный процессор Pentium Pro, нарастили его мощность (Pentium II, Pentium III), разработали механизм снижения энергопотребления (Pentium M), создали эффективную систему взаимодействия нескольких процессорных ядер (Core 2). Эта схема весьма условна, так как на каждом из этапов были и другие существенные доработки (такие как переход к 64-разрядной архитектуре), но некоторые наследственные черты все же сохранились.

В зависимости от целевого сегмента процессоры имеют свои технологические особенности. Для настольных систем предназначены Conroe-L (одно ядро), Allendale (два ядра), Conroe и Wolfdale (два ядра), Kentsfield и Yorkfield (четыре ядра). Кодовые имена Merom и Penryn носят продукты, ориентированные на мобильный сегмент рынка. Последней реинкарнацией архитектуры Core 2 станут шестиядерные процессоры Dunnington.

Следующее за Core 2 поколение процессоров продаётся под брендом Core i7 (архитектура Nehalem).

Следует отметить, что шестиядерные конфигурации не дают шестикратный прирост производительности по сравнению с одноядерными. Причины кроются в особенностях работы с памятью. В отдельных задачах вместо улучшения быстродействия возможно даже снижение скорости работы. Это объясняется тем, что большинство программных продуктов еще на адаптировано для работы на многопроцессорных (многоядерных) платформах.

Что же изменилось в Intel Core 2 по сравнению с Pentium 4? Одно из важных отличий – уход от длинноконвейерной архитектуры NetBrust, главной задачей которой было обеспечить определенное преимущество в условиях «гонки гигагерц». Кроме того, произошло существенное сокращение длины конвейера. В архитектуре Core его длина составляет 14 ступеней, в то время как в предыдущем поколении процессоров она была равна 31 ступени (ядро Prescott), а это более чем двукратное сокращение. Зато первые NetBrust-процессоры на ядре Northwood разгонялись с 1,6 до 3,4 ГГц. Не лишним будет напомнить, что такое повышение тактовой частоты было чревато чрезмерным энергопотреблением (для топовых процессоров TDP оно доходило до 160-170 Вт). Однако, как показывала практика, все эти гигагерцы очень слабо трансформировались в рост производительности.

Объем L2-кэша у новых моделей варьируется от 3 Мбайт у Wolfdale‑3М до 12 Мбайт у Yorkfield.

Прежде чем переходить к изучению структурной схемы, отметим ключевые технологические моменты, которые лежат в основе архитектуры Core:

Intel Wide Dynamic Execution – обеспечивает выполнение до пяти микроопераций за один такт.

Intel Intelligent Power Capability – представляет собой целый набор технологий, призванных существенно снизить энергопотребление.

Intel Advanced Smart Cache – подразумевает наличие общей для всех ядер кэш-памяти L2, которая динамически распределяется между ними в зависимости от выполняемых задач.

Intel Smart Memory Access – комплекс технологий по оптимизации алгоритмов доступа к памяти и предварительной загрузки данных.

Intel Advanced Digital Media Boost – технология, направленная на оптимизацию декодирования мультимедийного контента. Позволяет обрабатывать все 128-разрядные команды SSE, SSE2 и SSE3, широко используемые в мультимедийных и графических приложениях, за один такт.

Intel 64 Technology – 64-битный (ЕМ64Т) режим целочисленной и адресной арифметики. Он позволяет работать с числами большой разрядности, а также адресовать свыше 1 Тбайт памяти. 32-битная архитектура позволяла адресовать не более 4 Гбайт оперативной памяти. Это накладывает определенные ограничения при работе с большими объемами данных.

Статья раскрывает смысл термина «64 бита». В статье кратко рассмотрена история развития 64-битных систем, описаны наиболее распространенные на данный момент 64-битные процессоры архитектуры Intel 64 и 64-битная операционная система Windows.

Введение

В рамках архитектуры вычислительной техники под термином «64-битный» понимают 64-битные целые и другие типы данных, имеющих размер 64 бита. Под «64-битными» системами могут пониматься 64-битные архитектуры микропроцессоров (например, EM64T, IA-64) или 64-битные операционные системы (например, Windows XP Professional x64 Edition). Можно говорить о компиляторах, генерирующих 64-битный программный код.В данной статье будут рассмотрены различные моменты, связанные с 64-битными технологиями. Статья предназначена для программистов, желающих начать разрабатывать 64-битные программы , и ориентирована на Windows-разработчиков, поскольку для них вопрос знакомства с 64-битными системами наиболее актуален.

История 64-битных систем

64-битность только недавно вошла в жизнь большинства пользователей и прикладных программистов. Однако работа с 64-битными данными имеет уже длинную историю.1961: IBM выпускает суперкомпьютер IBM 7030 Stretch, в котором используются 64-битные слова данных, 32-битные или 64-битные машинные инструкции.

1974: Control Data Corporation запускает векторный суперкомпьютер CDC Star-100, в котором используется архитектура 64-битных слов (предыдущие системы CDC имели 60-битную архитектуру).

1976: Cray Research выпускает первый суперкомпьютер Cray-1, в котором реализована архитектура 64-битных слов и который послужит основой для всех последующих векторных суперкомпьютеров Cray.

1985: Cray выпускает UNICOS - первую 64-битную реализацию операционной системы Unix.

1991: MIPS Technologies производит первый 64-битный процессор, R4000, в котором реализована третья модификация разработанной в их компании архитектуры MIPS. Этот процессор используется в графических рабочих станциях SGI начиная с модели IRIS Crimson. Kendall Square Research выпускает свой первый суперкомпьютер KSR1, построенный на основе их собственной запатентованной 64-битной архитектуры RISC под операционной системой OSF/1.

1992: Digital Equipment Corporation (DEC) представляет полностью 64-битную архитектуру Alpha - детище проекта PRISM.

1993: DEC выпускает 64-битную Unix-подобную операционную систему DEC OSF/1 AXP (позже переименованную в Tru64 UNIX) для своих систем, построенных на архитектуре Alpha.

1994: Intel объявляет о своих планах по разработке 64-битной архитектуры IA-64 (совместно с компанией Hewlett-Packard) - преемника их 32-битных процессоров IA-32. Дата выпуска назначена на 1998-1999 годы. SGI выпускает IRIX 6.0 с 64-битной поддержкой чипсета R8000.

1995: Sun запускает 64-битный процессор семейства SPARC UltraSPARC. HAL Computer Systems, подчиненная Fujitsu, запускает рабочие станции, созданные на основе 64-битного процессора SPARC64 первого поколения, независимо разработанного компанией HAL. IBM выпускает микропроцессоры A10 и A30, а также 64-битные процессоры PowerPC AS. IBM также выпускает 64-битное обновление для системы AS/400, способное преобразовывать операционную систему, базы данных и приложения.

1996: Nintendo представляет игровую консоль Nintendo 64, созданную на основе более дешевого варианта MIPS R4000. HP выпускает реализацию 64-битной 2.0 версии собственной архитектуры PA-RISC PA-8000.

1997: IBM запускает линейку RS64 64-битных процессоров PowerPC/PowerPC AS.

1998: Sun выпускает Solaris 7 с полной 64-битной поддержкой UltraSPARC.

1999: Intel выпускает набор команд для архитектуры IA-64. AMD публично объявляет о своем наборе 64-битных расширений для IA-32, который был назван x86-64 (позже переименован в AMD64).

2000: IBM выпускает свой первый 64-битный мэйнфрейм zSeries z900, совместимый с ESA/390, а также новую операционную систему z/OS.

2001: Intel наконец запускает линейку 64-битных процессоров, которые теперь получают название Itanium и рассчитаны на высокопроизводительные серверы. Проект не соответствует ожиданиям из-за многочисленных задержек при выпуске IA-64 на рынок. NetBSD становится первой операционной системой, которая запускается на процессоре Intel Itanium после его выхода. Кроме того, Microsoft также выпускает Windows XP 64-Bit Edition для архитектуры IA-64 семейства Itanium, хотя в ней сохраняется возможность запускать 32-битные приложения при помощи прослойки WoW64.

2003: AMD представляет линейки процессоров Opteron и Athlon 64, созданные на основе архитектуры AMD64, которая является первой 64-битной процессорной архитектурой, основанной на архитектуре x86. Apple начинает использовать 64-битный процессор «G5» PowerPC 970 производства IBM. Intel утверждает, что процессорные чипы семейства Itanium останутся единственными 64-битными процессорами, разработанными в их компании.

2004: В ответ на коммерческий успех AMD, Intel признается, что они разрабатывали клон расширений AMD64, которому дали название IA-32e (позже переименован в EM64T, и затем еще раз в Intel 64). Intel также выпускает обновленные версии семейств процессоров Xeon и Pentium 4 с поддержкой новых команд.

2004: VIA Technologies представляет свой 64-битный процессор Isaiah.

2005: 31 января Sun выпускает Solaris 10 с поддержкой процессоров AMD64 / Intel 64. 30 апреля Microsoft выпускает Windows XP Professional x64 Edition для процессоров AMD64 / Intel 64.

2006: Sony, IBM и Toshiba начинают выпуск 64-битного процессора Cell для PlayStation 3, серверов, рабочих станций и других устройств. Microsoft выпускает Windows Vista с включенной 64-битной версией для процессоров AMD64 / Intel 64, которая поддерживает 32-битную совместимость. Все Windows-приложения и компоненты являются 64-битными, однако многие из них имеют 32-битные версии, включенные в систему в виде плагинов в целях совместимости.

2009: Как и Windows Vista, Windows 7 компании Microsoft включает полную 64-битную версию для процессоров AMD64 / Intel 64, и на большинство новых компьютеров по умолчанию устанавливается 64-битная версия. Выходит операционная система компании Apple Mac OS X 10.6, «Snow Leopard» которая имеет 64-битное ядро и предназначена для процессоров AMD64 / Intel 64, однако по умолчанию эта система устанавливается только на некоторые из последних моделей компьютеров компании Apple. Большинство приложений, поставляемых с Mac OS X 10.6, теперь также являются 64-битными.

Более подробно с историей развития 64-битных систем можно познакомиться в статье Джона Машей "Долгая дорога к 64 битам " и в энциклопедической статье в Wikipedia "64-bit " .

Прикладное программирование и 64-битные системы

На момент написания статьи в 2010 году, наиболее известными и распространенными являются две 64-битные архитектуры микропроцессоров: IA64 и Intel 64.- IA-64 64-битная микропроцессорная архитектура, разработанная совместно компаниями Intel и Hewlett Packard. Реализована в микропроцессорах Itanium и Itanium 2. Для более подробного знакомства с архитектурой IA-64 можно обратиться к следующим статьям в Wikipedia: "IA-64 ", "Itanium ", "Itanium 2 ". Архитектуру Itanium поддерживает большое количество производителей серверов: Bull, Fujitsu, Fujitsu Siemens Computers, Hitachi, HP, NEC, SGI и Unisys. Эти производители присоединились к Intel и множеству разработчиков ПО для создания Itanium Solutions Alliance , с целью продвижения архитектуры и ускорения темпов портирования ПО.

- Intel 64 (AMD64 / x86-64 / x64 / EM64T) - данная архитектура представляет собой расширение архитектуры x86 с полной обратной совместимостью. Существует множество вариантов названия данной архитектуры, что приводит к путанице, хотя, по сути, все эти названия обозначают одно и тоже: x86-64, AA-64, Hammer Architecture, AMD64, Yamhill Technology, EM64T, IA-32e, Intel 64, x64. Более подробно узнать о том, как появилось так много названий, можно в статье из Wikipedia: "X86-64 ". Процессоры с архитектурой Intel 64 нашли широкое распространение персональных компьютерах. И скорее всего ваш компьютер оснащен именно процессором с данной архитектурой.

Архитектура Intel 64 (AMD64)

Рассматриваемая архитектура Intel 64 простое, но в то же время мощное обратно совместимое расширение устаревшей промышленной архитектуры x86. Она добавляет 64-битное адресное пространство и расширяет регистровые ресурсы для поддержки большей производительности перекомпилированных 64-битных программ. Архитектура обеспечивает поддержку устаревшего 16-битного и 32-битного кода приложений и операционных систем без их модификации или перекомпиляции.Отличительной особенностью Intel 64 является поддержка шестнадцати 64-битных регистров общего назначения (в x86-32 имелось восемь 32-битных регистров). Поддерживаются 64-битные арифметические и логические операции над целыми числами. Поддерживаются 64-битные виртуальные адреса. Для адресации новых регистров для команд введены «префиксы расширения регистра», для которых был выбран диапазон кодов 40h-4Fh, использующихся для команд INC <регистр> и DEC <регистр> в 32- и 16-битных режимах. Команды INC и DEC в 64-битном режиме должны кодироваться в более общей, двухбайтовой форме.

Регистры:

16 целочисленных 64-битных регистра общего назначения (RAX, RBX, RCX, RDX, RBP, RSI, RDI, RSP, R8 - R15),

8 80-битных регистров с плавающей точкой (ST0 - ST7),

8 64-битных регистров Multimedia Extensions (MM0 - MM7, имеют общее пространство с регистрами ST0 - ST7),

16 128-битных регистров SSE (XMM0 - XMM15),

64-битный указатель RIP и 64-битный регистр флагов RFLAGS.

Необходимость 64-битной архитектуры определяется приложениями, которым необходимо большое адресное пространство. В первую очередь это высокопроизводительные серверы, системы управления базами данных, САПР и, конечно, игры. Такие приложения получат существенные преимущества от 64-битного адресного пространства и увеличения количества регистров. Малое количество регистров, доступное в устаревшей x86 архитектуре, ограничивает производительность в вычислительных задачах. Увеличенное количество регистров обеспечивает достаточную производительность для многих приложений.

Подчеркнем основные достоинства архитектуры x86-64:

- 64-битное адресное пространство;

- расширенный набор регистров;

- привычный для разработчиков набор команд;

- возможность запуска старых 32-битных приложений в 64-битной операционной системе;

- возможность использования 32-битных операционных систем.

64-битные операционные системы

Практически все современные операционные системы сейчас имеют версии для архитектуры Intel 64. Например, Microsoft предоставляет Windows XP x64. Крупнейшие разработчики UNIX систем также поставляют 64-битные версии, как например Linux Debian 3.5 x86-64. Однако это не означает, что весь код такой системы является полностью 64-битным. Часть кода ОС и многие приложения вполне могут оставаться 32-битными, так как Intel 64 обеспечивает обратную совместимость с 32-битными приложениями. Например, 64-битная версия Windows использует специальный режим WoW64 (Windows-on-Windows 64), который транслирует вызовы 32-битных приложений к ресурсам 64-битной операционной системы.WoW64

Windows-on-Windows 64-bit (WoW64) - подсистема операционной системы Windows, позволяющая запускать 32-битные приложения на всех 64-битных версиях Windows.Подсистема WoW64 не поддерживает следующие программы:

- программы, скомпилированные для 16-разрядных операционных систем;

- программы режима ядра, скомпилированные для 32-разрядных операционных систем.

WoW64 на архитектуре Intel 64 (AMD64 / x64) не требует эмуляции инструкций. Здесь подсистема WoW64 эмулирует только 32-битное окружение, за счет дополнительной прослойки между 32-битным приложением и 64-битным Windows API. Где-то эта прослойка тонкая, где-то не очень. Для средней программы потери в производительности из-за наличия такой прослойки составят около 2%. Для некоторых программ это значение может быть больше. Два процента это немного, но следует учитывать, что 32-битные приложения работают немного медленнее под управлением 64-битной операционной системы Windows, чем в 32-битной среде.

Компиляция 64-битного кода не только исключает необходимость в WoW64, но и дает дополнительный прирост производительности. Это связано с архитектурными изменениями в микропроцессоре, такими как увеличение количества регистров общего назначения. Для средней программы можно ожидать в пределах 5-15% прироста производительности от простой перекомпиляции.

Из-за наличия прослойки WoW64 32-битные программы работают менее эффективно в 64-битной среде, чем в 32-битной. Но все-таки, простые 32-битные приложения могут получить одно преимущество от их запуска в 64-битной среде. Вы, наверное, знаете, что программа, собранная с ключом /LARGEADDRESSAWARE:YES может выделять до 3-х гигабайт памяти, если 32-битная операционная система Windows запущена с ключом /3gb. Так вот, эта же 32-битная программа, запущенная на 64-битной системе, может выделить почти 4 GB памяти (на практике около 3.5 GB).

Подсистема WoW64 изолирует 32-разрядные программы от 64-разрядных путем перенаправления обращений к файлам и реестру. Это предотвращает случайный доступ 32-битных программ к данным 64-битных приложений. Например, 32-битное приложение, которое запускает файл DLL из каталога %systemroot%\System32, может случайно обратиться к 64-разрядному файлу DLL, который несовместим с 32-битной программой. Во избежание этого подсистема WoW64 перенаправляет доступ из папки %systemroot%\System32 в папку %systemroot%\SysWOW64. Это перенаправление позволяет предотвратить ошибки совместимости, поскольку при этом требуется файл DLL, созданный специально для работы с 32-разрядными приложениями.

Подробнее с механизмами перенаправления файловой системы и реестра можно познакомиться в разделе MSDN "Running 32-bit Applications ".

Программная модель Win64

Также как и в Win32 размер страниц в Win64 составляет 4Кб. Первые 64Кб адресного пространства никогда не отображаются, то есть наименьший правильный адрес это 0x10000. В отличие от Win32, системные DLL загружаются выше 4Гб.Особенность компиляторов для Intel 64 в том, что они могут наиболее эффективно использовать регистры для передачи параметров в функции, вместо использования стека. Это позволило разработчикам Win64 архитектуры избавиться от такого понятия как соглашение о вызовах (calling convention). В Win32 можно использовать разные соглашения: __stdcall, __cdecl, __fastcall и так далее. В Win64 есть только одно соглашение о вызовах. Рассмотрим пример, как передаются в регистрах четыре аргумента типа integer:

- RCX: первый аргумент

- RDX: второй аргумент

- R8: третий аргумент

- R9: четвертый аргумент

Разница в соглашениях о вызове приводит к тому, что в одной программе нельзя использовать и 64-битный, и 32-битный код. Другими словами, если приложение скомпилировано для 64-битного режима, то все используемые библиотеки (DLL) также должны быть 64-битными.

Передача параметров через регистры является одним из новшеств, делающих 64-битные программы более производительными, чем 32-битные. Дополнительный выигрыш в производительности можно получить, используя 64-битные типы данных.

Адресное пространство

Хотя 64-битный процессор теоретически может адресовать 16 экзабайт памяти (2^64), Win64 в настоящий момент поддерживает 16 терабайт (2^44). Этому есть несколько причин. Текущие процессоры могут обеспечивать доступ лишь к 1 терабайту (2^40) физической памяти. Архитектура (но не аппаратная часть) может расширить это пространство до 4 петабайт (2^52). Однако в этом случае необходимо огромное количество памяти для страничных таблиц, отображающих память.Помимо перечисленных ограничений, объем памяти, который доступен в той или иной версии 64-битной операционной системе Windows зависит также от коммерческих соображений компании Microsoft. Ниже приведена информация по объему памяти, поддерживаемой различными версиями 64-биными версиями Windows:

Windows XP Professional - 128 Gbyte;

Windows Server 2003, Standard - 32 Gbyte;

Windows Server 2003, Enterprise - 1 Tbyte;

Windows Server 2003, Datacenter - 1 Tbyte;

Windows Server 2008, Datacenter - 2 Tbyte;

Windows Server 2008, Enterprise - 2 Tbyte;

Windows Server 2008, Standard - 32 Gbyte;

Windows Server 2008, Web Server - 32 Gbyte;

Vista Home Basic - 8 Gbyte;

Vista Home Premium - 16 Gbyte;

Vista Business - 128 Gbyte;

Vista Enterprise - 128 Gbyte;

Vista Ultimate - 128 Gbyte;

Windows 7 Home Basic - 8 Gbyte;

Windows 7 Home Premium - 16 Gbyte;

Windows 7 Professional - 192 Gbyte;

Windows 7 Enterprise - 192 Gbyte;

Windows 7 Ultimate - 192 Gbyte;

Разработка 64-битных приложений

Наиболее полно вопросы разработки 64-битных приложений рассмотрены в курсе "Вопрос: Архитектура процессора - что это?

Ответ

: Термин "архитектура процессора" в настоящее время не имеет однозначного толкования. С точки зрения программистов, под архитектурой процессора подразумевается его способность исполнять определенный набор машинных кодов. Большинство современных десктопных CPU относятся к семейству x86, или Intel-совместимых процессоров архитектуры IA32 (архитектура 32-битных процессоров Intel). Ее основа была заложена компанией Intel в процессоре i80386, однако в последующих поколениях процессоров она была дополнена и расширена как самой Intel (введены новые наборы команд MMX, SSE, SSE2 и SSE3), так и сторонними производителями (наборы команд EMMX, 3DNow! и Extended 3DNow!, разработанные компанией AMD). Однако разработчики компьютерного железа вкладывают в понятие "архитектура процессора" (иногда, чтобы окончательно не запутаться, используется термин "микроархитектура") несколько иной смысл. С их точки зрения, архитектура процессора отражает основные принципы внутренней организации конкретных семейств процессоров. Например, архитектура процессоров Intel Pentium обозначалась как Р5, процессоров Pentium II и Pentium III - Р6, а популярные в недавнем прошлом Pentium 4 относились к архитектуре NetBurst. После того, как компания Intel закрыла архитектуру Р5 для сторонних производителей, ее основной конкурент - компания AMD была вынуждена разработать собственную архитектуру - К7 для процессоров Athlon и Athlon XP, и К8 для Athlon 64.

Вопрос: Какие процессоры лучше, 64-битные или 32-битные? И почему?

Ответ

: Достаточно удачное 64-битное расширение классической 32-битной архитектуры IA32 было предложено в 2002 году компанией AMD (первоначально называлось x86-64, сейчас - AMD64) в процессорах семейства К8. Спустя некоторое время компанией Intel было предложено собственное обозначение - EM64T (Extended Memory 64-bit Technology). Но, независимо от названия, суть новой архитектуры одна и та же: разрядность основных внутренних регистров 64-битных процессоров удвоилась (с 32 до 64 бит), а 32-битные команды x86-кода получили 64-битные аналоги. Кроме того, за счет расширения разрядности шины адресов объем адресуемой процессором памяти существенно увеличился.

И... все. Так что те, кто ожидает от 64-битных CPU сколь-нибудь существенного прироста производительности, будут разочарованы - их производительность в подавляющем большинстве современных приложений (которые в массе своей заточены под IA32 и вряд ли в обозримом будущем будут перекомпилированы под AMD64/EM64T) практически та же, что и у старых добрых 32-битных процессоров. Весь потенциал 64-битной архитектуры может раскрыться лишь в отдаленном будущем, когда в массовых количествах появятся (а может, и не появятся) приложения, оптимизированные под новую архитектуру. В любом случае, наиболее эффективен переход на 64-бита будет для программ, работающих с базами данных, программ класса CAD/CAE, а также программ для работы с цифровым контентом.

Вопрос: Что такое процессорное ядро?

Ответ

: В рамках одной и той же архитектуры различные процессоры могут достаточно сильно отличаться друг от друга. И различия эти воплощаются в разнообразных процессорных ядрах, обладающих определенным набором строго обусловленных характеристик. Чаще всего эти отличия воплощаются в различных частотах системной шины (FSB), размерах кэша второго уровня, поддержке тех или иных новых систем команд или технологических процессах, по которым изготавливаются процессоры. Нередко смена ядра в одном и том же семействе процессоров влечет за собой замену процессорного разъема, из чего вытекают вопросы дальнейшей совместимости материнских плат. Однако в процессе совершенствования ядра, производителям приходится вносить в него незначительные изменения, которые не могут претендовать на "имя собственное". Такие изменения называются ревизиями ядра и, чаще всего, обозначаются цифробуквенными комбинациями. Однако в новых ревизиях одного и того же ядра могут встречаться достаточно заметные нововведения. Так, компания Intel ввела поддержку 64-битной архитектуры EM64T в отдельные процессоры семейства Pentium 4 именно в процессе изменения ревизии.

Вопрос: В чем заключается преимущество двухъядерных процессоров перед одноядерными?

Ответ

: Самым значимым событием 2005 года стало появление двухъядерных процессоров. К этому времени классические одноядерные CPU практически полностью исчерпали резервы роста производительности за счет повышения рабочей частоты. Камнем преткновения стало не только слишком высокое тепловыделение процессоров, работающих на высоких частотах, но и проблемы с их стабильностью. Так что экстенсивный путь развития процессоров на ближайшие годы был заказан, и их производителям волей-неволей пришлось осваивать новый, интенсивный путь повышения производительности продукции. Самой расторопной на рынке десктопных CPU, как всегда, оказалась Intel, первой анонсировавшая двухъядерные процессоры Intel Pentium D и Intel Extreme Edition. Впрочем, AMD с Athlon64 X2 отстала от конкурента буквально на считанные дни. Несомненным достоинством двухъядерников первого поколения, к которым относятся вышеназванные процессоры, является их полная совместимость с существующими системными платами (естественно, достаточно современными, на которых придется только обновить BIOS). Второе поколение двухъядерных процессоров, в частности, Intel Core 2 Duo, "требует" специально разработанных для них чипсетов и со старыми материнскими платами не работает.

Не следует забывать, что, на сегодняшний день для работы с двухъядерными процессорами более или менее оптимизировано в основном только профессиональное ПО (включая работу c графикой, аудио- и видео данными), тогда как для офисного или домашнего пользователя второе процессорное ядро иногда приносит пользу, но гораздо чаще является мертвым грузом. Польза от двухъядерных процессоров в этом случае видна невооруженным взглядом только тогда, когда на компьютере запущены какие-либо фоновые задачи (проверка на вирусы, программный файервол и т.п.). Что касается прироста производительности в существующих играх, то он минимальный, хотя уже появились первые игры популярных жанров, полноценно использующие преимущества от использования второго ядра.

Впрочем, если сегодня стоит вопрос выбора процессора для игрового ПК среднего или верхнего ценового диапазона, то, в любом случае, лучше предпочесть двухъядерный, а то и 4-ядерный процессор чуть более высокочастотному одноядерному аналогу, так как рынок неуклонно движется в сторону мультиядерных систем и оптимизированных параллельных вычислений. Такая тенденция будет господствующей в ближайшие годы, так что доля ПО, оптимизированного под несколько ядер, будет неуклонно возрастать, и очень скоро может наступить момент, когда мультиядерность станет насущной необходимостью.

Вопрос: Что такое кэш?

Ответ

: Во всех современных процессорах имеется кэш (по-английски - cache) - массив сверхскоростной оперативной памяти, являющейся буфером между контроллером сравнительно медленной системной памяти и процессором. В этом буфере хранятся блоки данных, с которыми CPU работает в текущий момент, благодаря чему существенно уменьшается количество обращений процессора к чрезвычайно медленной (по сравнению со скоростью работы процессора) системной памяти. Тем самым заметно увеличивается общая производительность процессора.

При этом в современных процессорах кэш давно не является единым массивом памяти, как раньше, а разделен на несколько уровней. Наиболее быстрый, но относительно небольшой по объему кэш первого уровня (обозначаемый как L1), с которым работает ядро процессора, чаще всего делится на две половины - кэш инструкций и кэш данных. С кэшем L1 взаимодействует кэш второго уровня - L2, который, как правило, гораздо больше по объему и является смешанным, без разделения на кэш команд и кэш данных. Некоторые десктопные процессоры, по примеру серверных процессоров, также порой обзаводятся кэшем третьего уровня L3. Кэш L3 обычно еще больше по размеру, хотя и несколько медленнее, чем L2 (за счет того, что шина между L2 и L3 более узкая, чем шина между L1 и L2), однако его скорость, в любом случае, несоизмеримо выше, чем скорость системной памяти.

Кэш бывает двух типов: эксклюзивный и не эксклюзивный кэш. В первом случае информация в кэшах всех уровней четко разграничена - в каждом из них содержится исключительно оригинальная, тогда как в случае не эксклюзивного кэша информация может дублироваться на всех уровнях кэширования. Сегодня трудно сказать, какая из этих двух схем более правильная - и в той, и в другой имеются как минусы, так и плюсы. Эксклюзивная схема кэширования используется в процессорах AMD, тогда как не эксклюзивная - в процессорах Intel.

Вопрос: Что такое процессорная шина?

Ответ

: Процессорная (иначе - системная) шина, которую чаще всего называют FSB (Front Side Bus), представляет собой совокупность сигнальных линий, объединенных по своему назначению (данные, адреса, управление), которые имеют определенные электрические характеристики и протоколы передачи информации. Таким образом, FSB выступает в качестве магистрального канала между процессором (или процессорами) и всеми остальными устройствами в компьютере: памятью, видеокартой, жестким диском и так далее. Непосредственно к системной шине подключен только CPU, остальные устройства подсоединяются к ней через специальные контроллеры, сосредоточенные в основном в северном мосте набора системной логики (чипсета) материнской платы. Хотя могут быть и исключения - так, в процессорах AMD семейства К8 контроллер памяти интегрирован непосредственно в процессор, обеспечивая, тем самым, гораздо более эффективный интерфейс память-CPU, чем решения от Intel, сохраняющие верность классическим канонам организации внешнего интерфейса процессора. Основные параметры FSB некоторых процессоров приведены в табл

| Процессор | частота FSB, МГц | Тип FSB | Теоретическая пропускная способность FSB, Мб/с |

| Intel Pentium III | 100/133 | AGTL+ | 800/1066 |

| Intel Pentium 4 | 100/133/200 | QPB | 3200/4266/6400 |

| Intel Pentium D | 133/200 | QPB | 4266/6400 |

| Intel Pentium 4 EE | 200/266 | QPB | 6400/8533 |

| Intel Core | 133/166 | QPB | 4266/5333 |

| Intel Core 2 | 200/266 | QPB | 6400/8533 |

| AMD Athlon | 100/133 | EV6 | 1600/2133 |

| AMD Athlon XP | 133/166/200 | EV6 | 2133/2666/3200 |

| AMD Sempron | 800 | HyperTransport | <6400 |

| AMD Athlon 64 | 800/1000 | HyperTransport | 6400/8000 |

Процессоры компании Intel используют системную шину QPB (Quad Pumped Bus), передающую данные четыре раза за такт, тогда как системная шина EV6 процессоров AMD Athlon и Athlon XP передает данные два раза за такт (Double Data Rate). В архитектуре AMD64, используемой компанией AMD в процессорах линеек Athlon 64/FX/Opteron, применен новый подход к организации интерфейса CPU - здесь вместо процессорной шины FSB и для сообщения с другими процессорами используются: высокоскоростная последовательная (пакетная) шина HyperTransport, построенная по схеме Peer-to-Peer (точка-точка), обеспечивающая высокую скорость обмена данными при сравнительно низкой латентности.

Переход к 16-разрядным микропроцессорам - i8086 и другие аналогичной вычислительной мощности - ознаменовался качественным скачком всех основных характеристик МП: не просто увеличение разрядности, но значительное изменение архитектуры, системы команд, принципов организации структуры. Кроме показанного на Рис. 2.4, в машину пользователя i8086 включатся память объемом 1М байт и две области портов ввода и вывода по 64К каждая.

Рассмотрим "машину пользователя" на базе i8086 (К1810ВМ86):

| 7 0 | 7 0 | |||

| AX | AH | AL | Аккумулятор | |

| РОН | BX | BH | BL | База |

| CX | CH | CL | Счетчик | |

| DX | DH | DL | Данные | |

| 15 0 | ||||

| Регистры- | SP | Указатель стека | ||

| указатели | BP | Указатель базы | ||

| Индексные | SI | Индекс операнда | ||

| регистры | DI | Индекс результата | ||

| 15 0 | ||||

| CS | Сегмент кода | |||

| Сегментные | DS | Сегмент данных | ||

| регистры | SS | Сегмент стека | ||

| ES | Сегмент доп. данных | |||

| 15 0 | ||||

| IP | Счетчик команд | |||

| FLAGS | Регистр признаков |

Рис. 2.4. МП i8086 - машина пользователя

Разработчики i8086 старались сохранить возможность преемственности программного обеспечения i8080, поэтому в составе i8086 можно выделить подмножество регистров i8080 (соответствующие подмножество сохранено и в системе команд). Помимо операций с 16-разрядными регистрами общего назначения (РОН) AX..DX, допускается обращение к каждому байту этих регистров - AL..DL, AH..DH. В некоторых командах РОНы выполняют определенные по умолчанию функции счетчиков, индексных регистров и т.п. (см. Рис. 2.4).

16-разрядные регистры BP, SI, DI используются для образования исполнительных адресов памяти (см. ниже), SP - указатель стека, IP - программный счетчик (СчК), F - регистр флагов. Младший байт F полностью повторяет формат регистра признаков i8080, а старший имеет след. формат:

DF определяет направление модификации адресов массивов в командах цепочек (увеличение или уменьшение адреса);

IF маскирует внешнее прерывание по входу INT (при IF = 1 прерывание разрешено);

TF управляет пошаговым режимом работы микропроцессора. При TF = 1 после выполнения каждой команды автоматически формируется прерывание с вектором 4 (см. раздел 7).

Распределение адресного пространства .

Адресное пространство МП определяется в i8086 разрядностью шины адреса/данных + адреса и составляет 2 20 = 1М байт. В этом адресном пространстве МП одновременно доступны четыре сегмента, два из которых (DS и ES) предназначены для размещения данных, CS - сегмент кода (для размещения программы) и SS - сегмент стека.

Размеры сегментов определяются разрядностью логических адресов команд, данных и стека. Логические адреса команд и стека (верхушки) хранятся в 16-разрядных регистрах IP и SS соответственно, а логический адрес данных вычисляется в команде (см. ниже) и так же составляет 16 бит. Таким образом, размер каждого сегмента в i8086 составляет 64К байт. Положение сегмента в адресном пространстве (его начальный адрес) определяется содержимым одноименного сегментного регистра. Формирование физического адреса иллюстрируется схемой Рис. 2.5 .

Из Рис. 2.5 видно, что граница сегмента в адресном пространстве может быть установлена не произвольно, а таким образом, чтобы начальный адрес сегмента был кратен 16.

| 15 0 | ||

| Сегментный регистр | .0 0 0 0 | |

| 15 0 | ||

| Логический адрес | ||

| 19 0 | ||

| Физический адрес | ||

Рис. 2.5. Формирование физического адреса

По умолчанию сегментные регистры выбираются для образования физического адреса след. образом: при считывании команды по адресу IP используется CS, при обращении к данным - DS или ES, при обращению к стеку - SS. С помощью специальных приставок к команде (префикса) можно назначить для использования произвольный сегментный регистр (кроме пары CS:IP, которая не подлежит модификации). Границы сегментов могут быть выбраны т.о., что сегменты будут изолированы друг от друга, пересекаться или даже полностью совпадать. Например, если загрузить CS=SS=DS=ES=0, то все сегменты будут совпадать друг с другом и начинаться с нулевого адреса - вариант организации адресного пространства i8080.

Способы адресации

и методы формирования исполнительного адреса

Длина команды i8086 может составлять от 1 до 6 байт. Формат команды представлен на Рис. 2.6.

| 1 байт | 2 байт | 3..6 байты | ||||||||

| КОП | D | W | MOD | REG | R/M | [Смещение. данные] | ||||

| 7 2 1 0 | 7 6 5 3 2 0 | |||||||||

Рис. 2.6. Формат команды МП i8086

Большинство команд i8086 являются двухадресными, причем один адрес определяет регистр процессора, а другой - память или регистр. Поля команды имеют следующие назначения:

D - определяет направление передачи информации: при D = 1 REG является приемником, иначе - источником;

W - определяет длину операндов в команде: при W = 1 длина операндов составляет 16 бит (слово - word), иначе - 8 бит(байт);

REG - определяет регистр для первого операнда согласно Табл. 2.3:

| REG (R/M) | Регистр | |

| W = 0 | W = 1 | |

| AL | AX | |

| CL | CX | |

| DL | DX | |

| BL | BX | |

| AH | SP | |

| CH | BP | |

| DH | SI | |

| BH | DI |

Поля R/M и MOD определяют способ формирования адреса второго операнда, который располагается чаще всего в памяти. В Табл. 2.4 приведены способы формирования адресов памяти для двух значений поля MOD.

| R/M | MOD = 00 | MOD = 01 | ||

| Логич.адрес | Сегмент | Логич.адрес | Сегмент | |

| BX+SI | DS | BX+SI+d8 | DS | |

| BX+DI | DS | BX+DI+d8 | DS | |

| BP+SI | SS | BP+SI+d8 | SS | |

| BP+DI | SS | BP+DI+d8 | SS | |

| SI | DS | SI+d8 | DS | |

| DI | DS | DI+d8 | DS | |

| d16 | DS | BP+d8 | DS | |

| BX | DS | BX+d8 | DS |

В Табл. 2.4 d8 и d16 означают соответственно 8- и 16-разрядное смещение (3 и 3+4 байты команды). При операциях с d8 осуществляется его "знаковое расширение" до 16 бит - биты 15..8 принимают значение бита 7 (знака).

При значении MOD = 10 используются те же регистры, что при MOD = 01 (см. Табл. 2.4), но вместо d8 используется d16.

При MOD = 11 вторым операндом команды является регистр, определяемый полем R/M согласно Табл. 2.3.

Таким образом, операнд в памяти может адресоваться прямо (MOD = 00, R/M = 110) или косвенно посредством содержимого базовых (BP, BX) или индексных (SI, DI) регистров, а так же их суммы. Режимы адресации спроектированы с учетом эффективной реализации языков высокого уровня. Например, к простой переменной можно обратиться в режиме прямой адресации, а к элементу массива - в режиме косвенной адресации посредством BX, SI. Режим адресации через BP предназначен для доступа к данным из сегмента стека, что удобно при реализации рекурсивных процедур и компиляторов языков высокого уровня.