Современные вычислительные системы характеризуются:

□ стремительным ростом быстродействия микропроцессоров и некоторых внешних устройств (так, для отображения цифрового полноэкранного видео с высоким качеством необходима пропускная способность 22 Мбайт/с);

□ появлением программ, требующих выполнения большого количества интерфейсных операций (например программы обработки графики в Windows, мультимедиа).

В этих условиях пропускной способности шин расширения, обслуживающих одновременно несколько устройств, оказалось недостаточно для комфортной работы пользователей, поскольку компьютеры стали подолгу «задумываться». Разработчики интерфейсов пошли по пути создания локальных шин, подключаемых непосредственно к шине МП, работающих на тактовой частоте МП (но не на внутренней рабочей его частоте) и обеспечивающих связь с некоторыми скоростными внешними по отношению к МП устройствами: основной и внешней памятью, видеосистемами и т. д.

Сейчас существуют три основных стандарта универсальных локальных шин: VLB, PCI и AGP.

Шина VLB (VL-bus, VESA Local Bus) представлена в 1992 году ассоциацией стандартов видеоэлектроники (VESA - торговая марка Video Electronics Standards Association) и поэтому часто ее называют шиной VESA. Шина VLB, по существу, является расширением внутренней шины МП для связи с видеоадаптером и реже - с жестким диском, платами мультимедиа, сетевым адаптером. Разрядность шины для данных - 32 бита, для адреса - 30, реальная скорость передачи данных по VLB - 80 Мбайт/с, теоретически достижимая - 132 Мбайт/с (в версии 2 - 400 Мбайт/с).

Недостатки шины VLB:

□ ориентация только на МП 80386, 80486 (не адаптирована для процессоров класса Pentium);

□ жесткая зависимость от тактовой частоты МП (каждая шина VLB рассчитана только на конкретную частоту до 33 МГц);

□ малое количество подключаемых устройств - к шине VLB может подключаться только 4 устройства;

□ отсутствует арбитраж шины - могут быть конфликты между подключаемыми устройствами.

Шина PCI (Peripheral Component Interconnect, соединение внешних компонентов) - самый распространенный и универсальный интерфейс для подключения различных устройств. Разработана в 1993 году фирмой Intel. Шина PCI является намного более универсальной, чем VLB; допускает подключение до 10 устройств; имеет свой адаптер, позволяющий ей настраиваться на работу с любым МП от 80486 до современных Pentium. Тактовая частота PCI - 33 МГц, разрядность - 32 разряда для данных и 32 разряда для адреса с возможностью расширения до 64 бит, теоретическая пропускная способность 132 Мбайт/с, а в 64-битовом варианте - 264 Мбайт/с. Модификация 2.1 локальной шины PCI работает на тактовой частоте до 66 МГц и при разрядности 64 имеет пропускную способность до 528 Мбайт/с. Осуществлена поддержка режимов Plug and Play, Bus Mastering и автоконфигурирования адаптеров.

Конструктивно разъем шины на системной плате состоит из двух следующих подряд секции по 64 контакта (каждая со своим ключом). С помощью этого интерфейса к материнской плате подключаются видеокарты, звуковые карты, модемы, контроллеры SCSI и другие устройства. Как правило, на материнской плате имеется несколько разъемов PCI. Шина PCI, хотя и является локальной, выполняет и многие функции шины расширения. Шины расширения ISA, EISA, MCA (а она совместима с ними) при наличии шины PCI подключаются не непосредственно к МП (как это имеет место при использовании шины VLB), а к самой шине PCI (через интерфейс расширения). Благодаря такому решению шина является независимой от процессора (в отличие от VLB) и может работать параллельно с шиной процессора, не обращаясь к ней за запросами. Таким образом, загрузка шины процессора существенно снижается. Например, процессор работает с системной памятью или с кэш-памятью, а в это время по сети на жесткий диск пишется информация. Конфигурация системы с шиной PCI показана на рис. 5.8.

Шина AGP (Accelerated Graphics Port - ускоренный графический порт) - интерфейс для подключения видеоадаптера к отдельной магистрали AGP, имеющей

Глава 5. Микропроцессоры и системные платы

выход непосредственно на системную память. Разработана шина на основе стандарта PCI v2.1. Шина AGP может работать с частотой системной шины до 133 МГц и обеспечивает высочайшую скорость передачи графических данных. Ее пиковая пропускная способность в режиме четырехкратного умножения AGP4x (передаются 4 блока данных за один такт) имеет величину 1066 Мбайт/с, а в режиме восьмикратного умножения AGP8x - 2112 Мбайт/с. По сравнению с шиной PCI, в шине AGP устранена мультиплексированность линий адреса и данных (в PCI для удешевления конструкции адрес и данные передаются по одним и тем же линиям) и усилена конвейеризация операций чтения-записи, что позволяет устранить влияние задержек в модулях памяти на скорость выполнения этих операций.

Рис. 5.8. Конфигурация системы с шиной PCI

Шина AGP имеет два режима работы: DMA и Execute. В режиме DMA основной памятью является память видеокарты. Графические объекты хранятся в системной памяти, но перед использованием копируются в локальную память карты. Обмен ведется большими последовательными пакетами. В режиме Execute системная память и локальная память видеокарты логически равноправны. Графические объекты не копируются в локальную память, а выбираются непосредственно из системной. При этом приходится выбирать из памяти относительно малые случайно расположенные куски. Поскольку системная память выделяется динамически, блоками по 4 Кбайт, в этом режиме для обеспечения приемлемого быстродействия предусмотрен механизм, отображающий последовательные адреса фрагментов на реальные адреса 4-килобайтовых блоков в системной памяти. Эта процедура выполняется с использованием специальной таблицы (Graphic Address Re-mapping Table или GART), расположенной в памяти. Интерфейс выполнен в виде отдельного разъема, в который устанавливается AGP-видео-адаптер. Конфигурация системы с шиной AGP показана на рис. 5.9.

Внутримашинные системный и периферийный интерфейсы

Рис. 5.9. Конфигурация системы с шиной AGP

Все сказанное выше в отношении шин обобщается в табл. 5.4. Таблица 5.4. Основные характеристики шин

С повышением тактовых частот и разрядности процессоров настала насущная проблема в повышении скорости передачи данных в шинах (какой смысл использовать камень с тактовой частотой, скажем, 66 МГц, если шина работает на частоте лишь 8,33 МГц). В одних случаях, например клавиатуре или мышке, высокая скорость ни к чему. Но инженеры фирм производителей плат расширения готовы были изготовлять устройства со скоростью, которую шины не могли предоставить.

В

ыход из создавшегося положения был найден следующий: часть операций обмена данными, требующих высоких скоростей, должна осуществляться не через стандартные разъемы шины ввода/вывода, а через дополнительные высокоскоростные интерфейсы - шину процессора, примерно так же, как подключается внешний кэш.

Дело в том, что эти самые высокоскоростные интерфейсы подключаются к шине процессора. Из этого следует, что подключаемые платы будут иметь доступ непосредственно к процессору через его шину. Такая конструкция получила название локальной шины (LB, Local Bus). Локальная шина не заменяла собой прежние стандарты, а дополняла их. Рисунок демонстрирует различие между обычной архитектурой и архитектурой с локальной шиной. Между прочим, первые шины ISA как раз и были локальными, но когда их тактовая частота превысила 8 МГц, произошло разделение.

Основными шинами в компьютере по-прежнему оставались ISA или EISA, но к ним добавлялись один или несколько слотов локальной шины. Первоначально эти слоты использовались почти исключительно для установки видеоадаптеров, при этом к 1992 году было разработано несколько несовместимых между собой вариантов локальных шин, исключительные права на которые принадлежали фирмам-изготовителям.

Такое разнообразие сдерживала распространение локальных шин, поэтому Ассоциация по стандартам в области видеоэлектроники VESA (Video Electronic Standard Association), представляющая более 100 компаний, предложила в августе 1992 года свою спецификацию локальной шины VESA Local Bus (VL-bus или VLB) , которая не изменяла, а дополняла существующие стандарты. Шина VLB разработана с целью увеличить пропускную способность между основным процессором и видеокартой, для этого просто к основным шинам добавлялось несколько новых быстродействующих локальных слотов. Основная функция, для которой была предназначена новая шина, – обмен данными с видеоадаптером.

Представляла собой 32-битную шину, которая использовала третий и четвёртый разъём в виде продолжения обычного слота ISA. Шина работала на номинальной частоте 33 МГц и обеспечивала существенный прирост производительности по сравнению с ISA. В дальнейшем шину VLB стали использовать производители контроллеров жестких дисков и других устройств, требующих высокоскоростной передачи данных. Выпускались даже 100-мегабитные Ethernet контроллеры с шиной VLB. Широкое распространение шины VESA обусловила ее относительная дешевизна и совместимость “сверху вниз” со своей предшественницей – шиной ISA. Разъем VLB есть разъем ISA с “продолжением”.

Основные характеристики VL-bus таковы:

поддержка процессоров серий 80386 и 80486. Шина разработана для использования в однопроцессорных системах, при этом в спецификации предусмотрена возможность поддержки х86-несовместимых процессоров с помощью моста (bridge chip);

максимальное число bus master - 3 (не включая контроллер шины). При необходимости возможна установка нескольких подсистем для поддержки большего числа master. Несмотря на то что изначально шина была разработана для поддержки видеоконтроллеров, возможна поддержка и других устройств (например, контроллеров жесткого диска);

допускается работа шины на частоте до 66 МГц, однако электрические характеристики разъема VL-bus ограничивают ее до 50 МГц (это ограничение, естественно, не относится к интегрированным в материнскую плату устройствам);

двунаправленная (bi-directional) 32-разрядная шина данных поддерживает и 16-разрядный обмен. В спецификацию заложена возможность 64-разрядного обмена;

поддержка DMA обеспечивается только для bus masters. Шина не поддерживает специальных "инициаторов" DMA;

максимальная теоретическая пропускная способность шины 160 Мб/с (при частоте шины 50 МГц), стандартная - 107 Мб/с при частоте 33 МГц;

поддержка пакетного режима обмена (для материнских плат 80486, поддерживающих этот режим). Пять линий используется для идентификации типа и скорости процессора, сигнал Burst Last (BLAST#) используется для активизации этого режима. Для систем, не поддерживающих этот режим, линия устанавливается в 0;

использование 58-контактного разъема МСА. Максимально поддерживается 3 слота (на некоторых 50-мегагерцовых шинах возможна установка только 1 слота). Слот VL-bus устанавливается в линию за слотами ISA/EISA/MCA, поэтому VL-платам доступны все линии этих шин;

поддержка, как интегрированного кэш- процессора, так и кэша на материнской плате. Напряжение питания - 5 В. Устройства с уровнем выходного сигнала 3,3 В поддерживаются при условии, что они могут работать с уровнем входного сигнала 5 В.

Эта 32/32-разрядная шина разрабатывалась для машин с 386, 486 и Pentium процессорами. Наиболее широкое распространение шина VLB получила на материнских платах 486. На них VESA – это линии адреса, данных и управления процессора, выведенные на разъем. Это обстоятельство накладывает значительные ограничения на VLB- карты расширения – временные и нагрузочные параметры должны быть четко выдержаны. Как указано в инструкциях на многие материнские платы, число VLB- карт при тактовой частоте 25 МГц не должно превышать трех, при 33 МГц – двух, при 40 и 50 МГц – одной. В случае нарушения этих требований система будет работать нестабильно, поскольку превышена нагрузочная способность процессора.

Для оценки скорости шины можно привести следующий расчет: если карта расширения работает на частоте 50 МГц, тогда пропускная способность шины будет равна 32*50*10 6 = 1,6*10 9 Мбит/с = 200 Мбайт/с, что довольно много. Однако не следует забывать, что такая скорость почти никогда не может быть востребована, поскольку данные из видеопамяти не могут читаться с такой скоростью. Кроме того, во время обращения к VLB- карте процессор не может больше заниматься ничем, сколько бы медленным не было устройство на этой карте (например, последовательный порт).

Шина VL-bus явилась огромным шагом вперед по сравнению с ISA как по производительности, так и по дизайну. Одним из преимуществ шины являлось то, что она позволяла создавать карты, работающие с существующими чипсетами и не содержащие большого количества схем дорогостоящей управляющей логики. В результате VL-карты получались дешевле аналогичных EISA-карт. Однако и эта шина не была лишена недостатков, главными из которых являлись следующие:

ориентация на 486-й процессор. VL-bus жестко привязана к шине процессора 80486, которая отличается от шин Pentium и Pentium Pro /Pentium II.

ограниченное быстродействие. Как уже было сказано, реальная частота VL-bus - не больше 50 МГц. Причем при использовании процессоров с множителем частоты шина использует основную частоту (так, для 486DX2-66 частота шины будет 33 МГц);

схемотехнические ограничения. К качеству сигналов, передаваемых по шине процессора, предъявляются очень жесткие требования, соблюсти которые можно только при определенных параметрах нагрузки каждой линии шины. По мнению Intel, установка недостаточно аккуратно разработанных VL-плат может привести не только к потерям данных и нарушениям синхронизации, но и к повреждению системы;

ограничение количества плат. Это ограничение вытекает также из необходимости соблюдения ограничений на нагрузку каждой линии.

Популярность шины VLB продлилась до 1994 года. Главная особенность шины, которая позволяла достичь высокой производительности, послужила и причиной ухода VLB с рынка. Шина являлась прямым расширением шины 486 процессора/памяти, работающим на той же скорости, что и процессор (отсюда и имя - локальная шина - local bus). Прямое соединение означает, что подключение слишком большого числа устройств приводило к опасности создания помех самому процессору, особенно если сигналы проходили через слот. VESA рекомендовала использовать не более двух слотов на тактовых частотах 33 МГц или трёх слотов, если они использовали специальный буфер. На более высоких тактовых частотах следовало подключать не более двух устройств, а на частоте 50 МГц оба устройства VLB должны быть встроены в материнскую плату.

Поскольку шина VLB работает синхронно с процессором, увеличение частоты процессора приводило к появлению проблем с периферией VLB. Чем быстрее должна была работать периферия, тем она дороже стоила по причине трудностей, связанных с производством высокоскоростных компонент. Лишь немногие устройства VLB поддерживали скорость выше 40 МГц.

Внутримашинный системный интерфейс - система связи и сопряжения узлов и блоков ЭВМ между собой представляет совокупность электрических линий связи (проводов), схем сопряжения с компонентами компьютера, протоколов (алгоритмов) передачи и преобразования сигналов.

Существуют два варианта организации внутримашинного интерфейса:

– многосвязный интерфейс, где каждый блок ПК связан с прочими блоками своими локальными проводами; многосвязный интерфейс применяется, как правило, только в простейших бытовых ПК;

– односвязный интерфейс, где все блоки ПК связаны друг с другом через общую или системную шину.

В подавляющем большинстве современных ПК в качестве системного интерфейса используется системная шина. Функциональными характеристиками системной шины являются: количество обслуживаемых ею устройств и ее пропускная способность, т.е. максимально возможная скорость передачи информации. Пропускная способность шины зависит от ее разрядности (есть шины 8-, 16-, 32- и 64-разрядные) и тактовой частоты, на которой шина работает.

В качестве системной шины в разных ПК использовались и могут использоваться:

– шины расширений шины общего назначения, позволяющие подключать большое число самых разнообразных устройств;

– локальные шины специализирующиеся на обслуживании небольшого количества устройств определенного класса.

Сравнительные технические характеристики некоторых шин приведены в таблице 5.1.

Таблица 5.1 - Основные характеристики шин

Шины расширений.

1. Шина Multibus1 имеет две модификации: PC/XT bus (Persona) Computer eXtended Technology - ПК с расширенной технологией) и PC/AT bus (PC Advanced Technology - ПК с усовершенствованной технологией).

2. Шина PC/XT bus - 8-разрядная шина данных и 20-разрядная шина адреса, рассчитанная на тактовую частоту 4,77 МГц, имеет 4 линии для аппаратных прерываний и 4 канала для прямого доступа в память (каналы DMA - Direct Memory Access). Шина адреса ограничивала адресное пространство микропроцессора величиной 1 Мбайт. Используется с МП 8086,8088.

3. Шина PC/AT bus -16-разрядная шина данных и 24-разрядная шина адреса, рабочая тактовая частота до 8 МГц, но может использоваться и МП с тактовой частотой 16 МГц, так как контроллер шины может делить частоту пополам; имеет 7 линий для аппаратных прерываний и 4 канала DMA.

4. Шина ISA (Industry Standard Architecture - архитектура промышленного стандарта) - 16-разрядная шина данных и 24-разрядная шина адреса, рабочая тактовая частота 8 МГц, но может использоваться и МП с тактовой частотой 50 МГц (коэффициент деления увеличен). По сравнению с шинами PC/XT и PC/AT увеличено количество линий аппаратных прерываний с 7 до 15 и каналов прямого доступа к памяти DMA с 7 до 11. Благодаря 24-разрядной шине адреса адресное пространство увеличилось с 1 до 16 Мбайт. Теоретическая пропускная способность шины данных равна 16 Мбайт/с, реально около 4-5 Мбайт/с, ввиду ряда особенностей ее использования.

5. Шина EISA (Extended ISA) - 32-разрядная шина данных и 32-разрядная шина адреса, создана в 1989 г. Адресное пространство шины 4 Гбайта, пропускная способность 33 Мбайт/с, причем скорость обмена по каналу МП - КЭШ - ОП определяется параметрами микросхем памяти, увеличено число разъемов расширений (теоретически может подключаться до 15 устройств, практически - до 10). Улучшена система прерываний, шина EISA обеспечивает автоматическое конфигурирование системы и управление DMA, полностью совместима с шиной ISA (есть разъем для подключения ISA), шина поддерживает многопроцессорную архитектуру вычислительных систем. Шина EISA применяется в скоростных ПК, сетевых серверах и рабочих станциях.

6. Шина МСА (Micro Channel Architecture) -32-разрядная шина, созданная фирмой IBM в 1987 г. для машин PS/2, пропускная способность 76 Мбайт/с, рабочая частота 10-20 МГц. По прочим характеристикам близка к шине EISA, но не совместима ни с ISA, ни с EISA. Поскольку ЭВМ PS/2 не получили широкого распространения, в первую очередь ввиду отсутствия наработанного обилия прикладных программ, шина МСА также используется не очень широко .

Локальные шины VLB и PCI

Два основных стандарта универсальных локальных шин - VLB и PCI.

1. Шина VLB (VESA Local Bus -локальная шина VESA) - называют шиной VESA. Шина VLB, no существу, является расширением внутренней шины МП для связи с видеоадаптером и реже с винчестером, платами Multimedia, сетевым адаптером. Разрядность шины - 32 бита (возможен 64-разрядный вариант). Реальная скорость передачи данных по VLB - 80 Мбайт/с (теоретически достижимая -132 Мбайт/с).

Недостатки шины:

– рассчитана на работу с МП 80386, 80486, не адаптирована для процессоров Pentium, Pentium Pro, Power PC;

– жесткая зависимость от тактовой частоты МП (каждая шина VLB рассчитана только на конкретную частоту);

– малое количество подключаемых устройств - к шине VLB (только четыре устройства);

– отсутствует арбитраж шины - могут быть конфликты между подключаемыми устройствами.

2. Шина PCI. (Peripheral Component Interconnect - соединение внешних устройств). Шина PCI является более универсальной, чем VLB, имеет свой адаптер, позволяющий ей настраиваться на работу с любым МП, она позволяет подключать 10 устройств самой разной конфигурации с возможностью автоконфигурирования, имеет свой "арбитраж", средства управления передачей данных.

Разрядность PCI - 32 бита с возможностью расширения до 64 бит, при частоте шины 33 МГц теоретическая пропускная способность 132 Мбайт/с, а в 64-битовом варианте -263 Мбайт/с (реальная вдвое ниже).

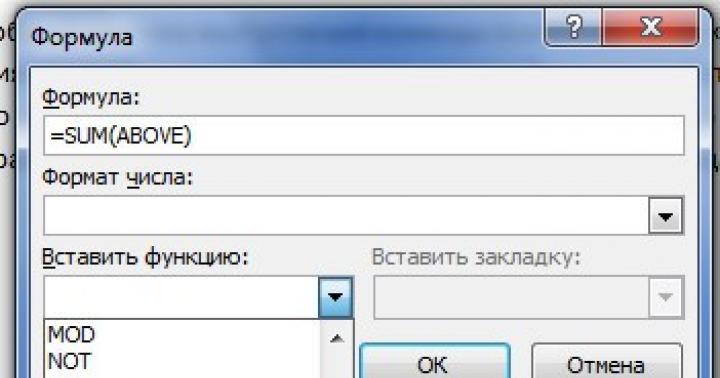

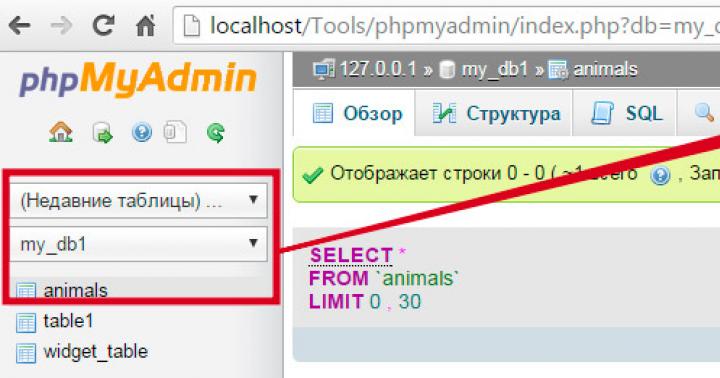

Варианты конфигурации систем с шинами VLB и PCI показаны на рисунке 5.1 и рисунке 5.2 соответсвенно. Использование в ПК шин VLB и PCI возможно только при наличии соответствующей VLB- или PCI-материнской платы.

Рисунок 5.1 - Конфигурация системы с шиной VLB

Рисунок 5.2 - Конфигурация системы с шиной PCI

Для подключения шины PCI к другим шинам применяются специальные аппаратные средства - мосты шины PCI (PCI Bridge). Главный мост (Host Bridge) используется для подключения PCI к системной шине (шине процессора или процессоров). Одноранговый мост (Peer-to-Peer Bridge) используется для соединения двух шин PCI. Две и более шины PCI применяются в серверных платформах - дополнительные шины PCI позволяют увеличить количество подключаемых устройств. Таким образом, совокупность мостов, расположенных вокруг шины PCI, выполняет маршрутизацию (routing) обращений по всем связанным шинам. В общем случае считается, что устройство с конкретным адресом может присутствовать только на одной из шин данного компьютера, а на каком именно, "знают" запрограммированные мосты.

Основные возможности шины.

1. Синхронный 32-х или 64-х разрядный обмен данными. При этом для уменьшения числа контактов используется мультиплексирование, то есть адрес и данные передаются по одним и тем же линиям.

2. Поддержка 5V и 3.3V логики. Разъемы для 5 и 3.3V плат различаются расположением ключей (cуществуют универсальные платы, поддерживающие оба напряжения, но частота 66MHz поддерживается только 3.3V логикой).

3. Частота работы шины 33MHz или 66MHz (в версии 2.1) позволяет обеспечить широкий диапазон пропускных способностей (с использованием пакетного режима):

– 132 МВ/с при 32-bit/33MHz;

– 264 MB/с при 32-bit/66MHz;

– 264 MB/с при 64-bit/33MHz;

– 528 МВ/с при 64-bit/66MHz.

4. Для работы шины на частоте 66MHz необходимо, чтобы все периферийные устройства работали на этой частоте.

5. Полная поддержка multiply bus master (например, несколько контроллеров жестких дисков могут одновременно работать на шине).

6. Поддержка write-back и write-through кэша.

7. Автоматическое конфигурирование карт расширения при включении питания.

8. Спецификация шины позволяет комбинировать до восьми функций на одной карте (например, видео + звук и т.д.).

9. Шина позволяет устанавливать до 5 слотов расширения, однако возможно использование моста PCI-PCI для увеличения количества карт расширения.

10. PCI-устройства оборудованы таймером, который используется для определения максимального промежутка времени, в течении которого устройство может занимать шину.

11. Шина поддерживает метод передачи данных, называемый "linear burst" (метод линейных пакетов). Этот метод предполагает, что пакет информации считывается (или записывается) в непрерывное пространство памяти, то есть адрес автоматически увеличивается для следующего байта. Естественным образом при этом увеличивается скорость передачи собственно данных за счет уменьшения числа передаваемых адресов.

Спецификация шины PCI определяет три типа ресурсов - два обычных (диапазон памяти и диапазон ввода/вывода) и configuration space - "конфигурационное пространство". Автоконфигурирование устройств (выбор адресов, запросов прерываний) поддерживается средствами BIOS и ориентировано на технологию Microsoft/Intel Plug and Play (PnP) PC architecture .

Стандарт PCI определяет для каждого слота конфигурационное пространство размером до 256 восьмибитных регистров, не приписанных ни к пространству памяти, ни к пространству ввода/вывода. Доступ к ним осуществляется по специальным циклам шины Configuration Read и Configuration Write, вырабатываемым контроллером при обращении процессора к регистрам контроллера шины PCI, расположенным в его пространстве ввода/вывода. Дополнительная информация о шине PCI приведено в приложении Е.

Интерфейс PCI Express (3GIO).

Аббревиатура 3GIO расшифровывается как «3-е поколение шины ввода-вывода»(Third Generation Input/Output Interconnection) .

Масштабируемость производительности достигается через повышение частоты и добавление линий к шине. PCI Express призвана обеспечить высокую пропускную способность на контакт с низким количеством служебной информации и низкими задержками. Поддерживаются несколько виртуальных каналов на один физический.

Система адресации полностью совместима со спецификацией PCI, что позволяет подключать устройства PCI к новой шине. Без изменений остался механизм автоматического конфигурирования устройств (Plug-and-Play). Данные пересылаются пакетами по 8 или 10 бит (в последнем случае два бита предназначены для поддержки механизма контроля четности и исправления ошибок).

Спецификация интерфейса PCI Express предусматривает несколько уровней взаимодействия и протоколов:

– физический;

– данных (Data Link);

– транзакций (транспортный);

– приложений и драйверов;

– конфигурационный.

Физической основой PCI Express являются последовательные низковольтные дифференциальные линии связи, по одной паре для передачи и приема данных. Масштабируемость шины достигается кратным (1, 2, 4, 8, 16, 32) увеличением числа линий. Между участниками обмена данными по шине PCI Express устанавливается выделенный канал связи, ширина которого и тактовая частота обговариваются устройствами в процессе инициализации канала. Здесь же происходит представление данных в формате 8 или 10 бит. При необходимости 2 бита используются для контроля за целостностью данных. Тем самым реализуется концепция обмена данными «точка - точка».

Теоретически полоса пропускания самого узкого канала достигает 2,5 Гбит/с в каждом направлении.

Система адресации и команд включает три стандартных поля, совместимых с интерфейсом РСI (область памяти, адрес ввода-вывода, инициализации и конфигурирования), а также дополнительное поле сообщений (Message).

Интерфейсная шина AGP

Выделенная для потока видеоданных интерфейсную шину - AGP (Accelerated Graphics Port - ускоренный графический порт) (рисунок 5.3) .

Рисунок 5.3– Структурная схема графического ускорителя с AGP

Преимуществом новой шины стала ее высокая пропускная способность. Если шина ISA позволяла передавать до 5,5 Мбайт/с, VLB -до 130 Мбайт/с (однако при этом чрезмерно загружала центральный процессор), а PCI до 133 Мбайт/с, то шина AGP теоретически имеет пиковую пропускную способность до 2132 Мбайт/с (в режиме передачи 32-разрядных слов).

Интерфейс AGP обеспечивает прямое соединение между графической подсистемой и оперативной памятью. Таким образом, выполняются требования вывода ЗD-графики в режиме реального времени и, кроме того, более эффективно используется память буфера кадра, тем самым увеличивается скорость обработки 3D-графики. Шина AGP соединяет графическую подсистему с контроллером системной памяти, разделяя доступ с центральным процессором компьютера. Через AGP возможно подключение графических плат.

Основными особенности AGP, влияющими на производительность:

Шина способна передавать два (AGP2x), четыре (AGP4x) или восемь (AGP8x) блоков данных за один цикл;

Устранена мультиплексированность линий адреса и данных (в PCI для удешевления материнских плат адрес и данные передаются по одним и тем же линиям);

Конвейеризация операций чтения/записи позволяет устранить влияние задержек в модулях памяти на скорость выполнения этих операций.

Шина AGP работает в двух основных режимах - DIME (Direct Memory Execute) и DMA (Direct Memory Access). В режиме DMA основной памятью считается память на карте. Текстуры могут храниться в системной памяти, но перед использованием копируются в локальную память видеокарты. Обмен ведется большими последовательными пакетами данных.

В режиме Execute локальная и системная память для видеокарты логически равноправны. Текстуры не копируются в локальную память, а выбираются непосредственно из системной памяти. Таким образом, приходится передавать сравнительно небольшие случайно расположенные куски. Поскольку системная память требуется и другим устройствам, она выделяется динамически, блоками по 4 Кбайт. Поэтому для обеспечения приемлемого быстродействия предусмотрен специальный механизм, отображающий последовательные адреса на реальные адреса блоков в системной памяти.

Шина AGP поддерживает все стандартные операции шины PCI, поэтому поток данных по ней можно представить как смесь чередующихся AGP и РСI-операций чтения/записи. Операции шины AGP являются раздельными (split). Это означает, что запрос на проведение операции отделен от собственно пересылки данных.

Новая спецификация - AGP Pro. Основное отличие этого интерфейса заключается в возможности управления энергопитанием. С этой целью в разъем AGP Pro добавлены новые линии.

Интерфейс AGP Pro предназначен для графических станций. Двукратное увеличение пропускной способности достигнуто за счет повышения тактовой частоты шины до 66 МГц и применения нового уровня сигналов 0,8 В (в AGP 2.0 использовался уровень 1,5 В). Тем самым при сохранении основных параметров интерфейса повышена пропускная способность шины до 2132 Мбайт/с.

Повышенная пропускная способность порта AGP обеспечивается следующими тремя факторами:

– конвейеризацией операций обращения к памяти;

– сдвоенными передачами данных;

– демультиплексированием шин адреса и данных.

Интерфейс SCSI

Системный интерфейс малых компьютеров SCSI (Small Computer System Interface) был стандартизован ANSI в 1986 году. Интерфейс предназначен для соединения устройств различных классов - памяти прямого и последовательного доступа, CD-ROM, оптических дисков однократной и многократной записи, устройств автоматической смены носителей информации, принтеров, сканеров, коммуникационных устройств и процессоров. Устройством SCSI - SCSI Device - называется как хост-адаптер, связывающий шину SCSI с какой-либо внутренней шиной компьютера, так и контроллер целевого устройства - target controller, с помощью которого оно подключается к шине SCSI. К одному контроллеру может подключаться несколько периферийных устройств, по отношению к которым контроллер может быть как внутренним, так и внешним.

По физической реализации интерфейс является 8-битной параллельной шиной с тактовой частотой 5 МГц. Шина допускает подключение до 8 устройств, скорость передачи данных в первоначальной версии достигала 5 Мбайт/с.

Спецификация - SCSI-2, расширяющая возможности шины как в количественных, так и в качественных показателях. Тактовая частота шины Fast SCSI-2 достигает 10 МГц, а Ultra SCSI-2 - 20 МГц. Разрядность данных может быть увеличена до 16 бит - эта версия называется Wide SCSI-2 (широкий), а 8-битную версию назвали Narrow (узкий). 16-битная шина позволяет увеличивать число устройств до 16. Стандарт SCSI-2 определяет и 32-битную версию интерфейса. Комбинации тактовой частоты и разрядности обеспечивают широкий диапазон пропускной способности, достигающей 40 Мбайт/с для реальной версии Ultra Wide SCSI-2.

Спецификация SCSI-2 определяет систему команд, которая включает набор базовых команд для всех периферийных устройств, и специфических команд для периферии различных классов.

Спецификация - SCSI-3 - дальнейшее развитие стандарта, направленное на увеличение количества подключаемых устройств. SCSI-3 существует в виде широкого спектра документов, определяющих отдельные стороны интерфейса.

Современные устройства с интерфейсом SCSI выпускаются в соответствии со стандартом SCSI-2 или SCSI-3. Стандарт SCSI-3 предполагает различные варианты протокольного и физического уровня интерфейса, включающие как параллельные, так и последовательные шины.

Для параллельных шин скорость передачи данных определяется частотой передач, измеряемой в миллионах передач за секунду - MT/sec (Mega Transfer/sec) и разрядностью.

Скорость передачи данных для различных вариантов параллельной шины приведена в таблице 5.2.

Таблица 5.2 - Скорость передачи данных по параллельной шине SCSI

Последовательный интерфейс FCAL (Fibre Channel Arbitrated Loop - арбитражное кольцо волоконного канала) по реализации ближе к интерфейсам локальных сетей. Этот интерфейс, известный также и как Fibre Channel SCSI, может иметь как электрическую (коаксиальный кабель), так и оптоволоконную реализацию. В обоих случаях частота 800 МГц обеспечивает скорость передачи данных 100 Мбайт/с. Медный кабель допускает длину шины до 30 м, оптический - до 10 км. Здесь используется иной протокольный и физический уровни интерфейса и имеется возможность подключения к шине до 126 устройств (а не 8 или 16, как для параллельного интерфейса). Двухпортовые устройства могут достигать пиковой скорости обмена до 200 Мбайт/с.

Физический интерфейс.

Физически 8-битный интерфейс SCSI представляет собой шину, состоящую из 25 сигнальных цепей. Для обеспечения помехозащищенности каждая сигнальная цепь имеет свой отдельный обратный провод. Каждое устройство SCSI, подключенное к шине, должно иметь свой уникальный адрес, назначаемый при конфигурировании. Для 8-битной шины диапазон значений адреса 0-7, для 16-битной - 0-15. Адрес задается предварительной установкой переключателей или джамперов, для хост-адаптера возможно и программное конфигурирование. Дополнительная информация представлена в приложении Ж.

Интерфейс HyperTransport

Высокоскоростная шина ввода-вывода HyperTransport (HT) предназначена для использования в компьютерных системах, прежде всего в качестве внутренней локальной шины. В сравнении с шиной PCI интерфейс HyperTransport позволяет снизить число проводников на системной плате, устранить задержки, связанные с монополизацией шины устройствами с низкой производительностью, уменьшить энергопотребление и повысить пропускную способность.

Шина HyperTransport организована на различных уровнях:

На физическом уровне шина представлена линиями данных,

управления, тактовыми, а также контроллерами и стандартными электрическими сигналами;

На уровне передачи данных определяется порядок инициализации и конфигурирования устройств, установления и прекращения сеанса связи, циклического контроля адекватности данных, выделения пакетов для передачи данных;

На уровне протокола определены команды выделения виртуальных каналов связи, правила управления потоком данных;

На уровне транзакций команды протокола конкретизированы в управляющие сигналы, например чтения или записи;

На уровне сессии определены правила управления энергопотреблением и прочие команды общего характера.

Физические устройства в рамках интерфейса HyperTransport подразделяются на несколько типов:

Cave («пещера») - оконечное устройство на двунаправленном канале связи;

Tunnel («туннель») - устройство на двунаправленном канале связи, установленное «на проходе» (но не мост);

Bridge («мост») - устройство на двунаправленных каналах связи, один из которых считается главным и связывает устройство с контроллером шины (Host), а другие соединяют с прочими устройствами.

Топологию совокупности устройств на шине HyperTransport можно построить в виде цепочки или дерева. Фирма AMD предлагает сторонним производителям готовые схемы с поддержкой шины Hyper Transport: туннель «HT - AGP» (AMD-8151), хаб каналов ввода-вывода (AMD-8111) и туннель «HT - PCI-X» (AMD-8131). Таким образом обеспечивается совместимость с прочими, в том числе морально устаревшими, интерфейсами и плавный переход на новую шину. Что касается схемотехнической организации шины HyperTransport, то надо отметить ее масштабируемость в зависимости от решаемых задач. В минимальной конфигурации (ширина канала 2 бит, на каждый бит требуется две физические линии) потребуется 24 контакта (8 для данных + 4 для тактовых сигналов + 4 для линий управления + 2 сигнальных + 4 заземления + 1 питания + 1 сброса), в максимальной конфигурации (ширина канала 32 бит) речь идет уже о 197 выводах. Для сравнения укажем, что спецификация PCI 2.1 предусматривает 84 вывода, a PCI-X - 150 выводов.

Физически технология HyperTransport основыванется на улучшенной версии низковольтных дифференциальных сигналов (Low Voltage Differential Signaling, LVDS ). Для всех линий (данных, управления, тактовых) используются шины с дифференциальным сопротивлением 100 Ом. Уровень сигнала составляет 1,2 В (в отличие от 2,5 В, установленных спецификацией IEEE LVDS). Благодаря этому длина шины может достигать 24 дюйма (около 61 см) при полосе пропускания на одной линии до 800 Мбит/с. Необходимо заметить, что спецификация HyperTransport предусматривает разделение «восходящих» (Upstream) и «нисходящих» (Downstream) потоков данных (асинхронность). Такой подход обеспечивает возможность существенного увеличения, тактовых частот по сравнению с существующими архитектурами, поскольку каждый сигнал LVDS функционирует в пределах своей физической линии. Кроме того, пакет, объединяющий адреса, команды и данные, всегда кратен 32 бит. Поэтому обеспечивается его безошибочная передача по масштабируемым каналам шириной от 2 до 32 бит. Это позволяет применять единую технологию HyperTransport для соединения потребителей ресурсов шины различной производительности: процессор, оперативная память, видеоконтроллер, низкоскоростные устройства ввода-вывода, используя в каждом случае минимально необходимое число линий. Пиковая пропускная способность соединения Hyper Transport достигает 12,8 Гбайт/с (по 6,4 Гбайт/с на нисходящий и восходящий каналы шириной 32 бит при частоте 800 МГц и передаче данных по фронту и спаду сигнала). Для сравнения укажем, что пиковая пропускная способность системной шины (200 МГц) процессора AMD Athlon составляет 2,128 Гбайт/с. Важной особенностью технологии HyperTransport является совместимость с устройствами PCI на уровне протоколов.

Интерфейс USB

Шина USB (Universal Serial Bus– универсальная последовательная шина) является промышленным стандартом расширения архитектуры персональных компьютеров (РС), ориентированным на интеграцию с телефонией и устройствами бытовой электроники.

Архитектура USB определяется критериями:

– легко реализуемое расширение периферии РС;

– дешевое решение, поддерживающее скорость передачи до 12 Мбит/с (версия 1.0) и до 480 Мбит/с (версия 2.0);

– полная поддержка в реальном времени передачи аудио- и видеоданных;

– гибкость протокола смешанной передачи, изохронных данных и асинхронных сообщений;

– интеграция с выпускаемыми устройствами;

– доступность в РС всех конфигураций и размеров;

– создание новых классов устройств, расширяющих РС;

– простота кабельной системы и подключений;

– скрытие подробностей подключения от конечного пользователя;

– самоидентифицирующиеся ПУ, автоматическая связь устройств с драйверами и конфигурирование;

– возможность динамического подключения ПУ и конфигурирования.

С середины 1996 года выпускаются РС со встроенным контроллером USB, реализуемым чипсетом.

Таблица 5.3 - Схема цоколевки

Таблица 5.4 - Названия и функциональные назначения выводов

Рисунок 5.4 - Топология шины USB

В вершине этой пирамиды, в корневом узле, находится хост-устройство , а все остальные узлы являются функциональными устройствами (функциями ) или соединителями (хабами ).

Система USB состоит из трех основных частей:

– USB хост-устройство;

– USB разветвитель (хаб);

– USB устройство (функция).

USB хост-устройство (устройство – хозяин интерфейса) – это главное устройство в любой USB системе, которое организует все передачи данных и команд по шине интерфейса .

Интерфейс USB в компьютерной системе множественного доступа реализуется хост-контроллером, который является комбинацией аппаратных средств и программного обеспечения.

Хост-контроллер находится в корневом узле главной системы (на материнской плате) компьютера, и обеспечивает, как правило, две точки присоединения.

Основные функции хост-контроллера:

– определение подключения и удаления USB устройств;

– управление потоком команд между корневым узлом и USB устройством;

Типы и характеристики стандартных шин, используемых в настоящее время, приведены в таблице 10.1.

Характеристики стандартных шин.

| Тип/назначение | Разрядность | Тактовая частота (МГц) | Пропускная способность (Мб/с) |

| ISA/общая | |||

| EISA/общая | |||

| VLB (VESA) | |||

| VLB2/локальная | |||

| PCI/ввод/вывод | 33, 66 | 120, 133 | |

| SBUS/ввод/вывод | 32, 64 | 20, 25 | 80, 100 |

| MBUS/процессор-память | 125 (400) | ||

| XDBUS/процессор-память | 310 (400) | ||

| AGP/локальная графическая | |||

| PCI-X |

Системная шина ISA (Industry Standard Architecture) впервые стала применяться в ПК IBM PC/AT на базе процессора 12826. Данная шина позволяет передавать параллельно 16 бит данных и обращаться к 16 Мбайт системной памяти. В современных компьютерах используется как шина ввода/вывода для организации связи с медленно действующими периферийными устройствами. С появлением процессоров i386, i486 системная шина ISA стала "узким местом" ПК на их основе.

Системная шина EISA (Extended Industry Standard Architecture), разработанная в 1988 году, обеспечивает адресное пространство в 4 Гбайта, 32-битовую передачу данных, тактируется частотой около 8 Мгц, имеет максимальную теоретическую скорость передачи данных 33 Мбайт/с и совместима с шиной ISA.

Шина МСА также обеспечивает 32-разрядную передачу данных, тактируется частотой 10 МГц, но не совместима с шиной ISA и используется только в компьютерах компании IBM.

Локальная шина VESA-Local-Bus (VLB) предназначалась для увеличения быстродействия видеоадаптеров и контроллеров дисковых накопителей. Она подключалась непосредственно к процессору i486, и только к нему. После появления процессора Pentium ассоциация VESA приступила к работе над новым стандартом VLB версии 2, который предусматривает использование 64-битовой шины данных и увеличение количества разъемов расширения. Ожидаемая скорость передачи данных - до 400 Мбайт/сек.

Шина PCI (Peripheral Component Interconnection) в первом варианте использовалась как локальная шина и предназначалась для тех же целей, что и предыдущая шина (VLB). В действующем втором варианте шина PCI относится к шинам ввода/вывода. В данном случае соединение шин центрального процессора и PCI осуществляется через так называемую РС1-перемычку, мост PCI или контроллер, которые согласуют шину центрального процессора с шиной PCI. Это означает, что PCI может работать с процессорами различных платформ и поколений.

Шина VME приобрела большую популярность как шина ввода/вывода в рабочих станциях и серверах на базе RISC-процессоров. Эта шина высоко стандартизирована, имеет несколько версий этого стандарта: VME32, VME64.

В однопроцессорных и многопроцессорных рабочих станциях и серверах на основе микропроцессоров архитектуры SPARC одновременно используются несколько типов шин: Sbus, Mbus иXDBus , причем шина Sbus применяется в качестве шины ввода/вывода, a Mbus и XDBus - в качестве шин для объединения большого числа процессоров и памяти.

Локальная шина AGP (Accelerated Graphics Port) первоначально предназначалась исключительно для графики и была способна повысить производительность видео-приложений. Для использования технологии AGP необходим набор микросхем Intel 440LX, который позволяет разгрузить сравнительно "узкую" (133 Мб/с) шину PCI от жадного на ресурсы видеоадаптера и подключить последний к специально предназначенной для него более "широкой" (528 Мб/с) шине AGP. На долю же PCI остаются более медленные устройства, функционирование которых существенно улучшается благодаря отключению от шины более быстродействующих устройств, то и дело создающих "пробки" в стремительном потоке данных. Набор 440LX не только имеет поддержку AGP, но и допускает использование в машинах на базе Pentium II быстродействующей памяти SDRAM, которая обеспечивает более высокую производительность, чем ОЗУ типа EDO DRAM, применяемое в машинах Pentium II со старым набором микросхем.

PCI-X - расширение шины PCI, которая работает на тактовой частоте 133 МГц. Шина PCI-X обладает обратной совместимостью с PCI, требует нового набора микросхем Intel 450 NX, кроме того, благодаря новой схеме обмена регистр-регистр достигается пропускная способность 1,06 Гб/с (8 Гбит/с), что обеспечивает почти шестикратный выигрыш в производительности. В первую очередь PCI-X предназначена для подключения высокопроизводительных адаптеров типа Gigabit Ethernet, Ultra 3SCSI и Fibre Channel (FC-AL).

VLB SVGA-карта

Назначение контактов разъёма VLB

VESA local bus (VL-Bus или VLB) - тип локальной шины , разработанный ассоциацией VESA для персональных компьютеров. Шина VLB, по существу, является расширением внутренней шины микропроцессора Intel 80486 для связи с видеоадаптером и реже с контроллером HDD . Реальная скорость передачи данных по VLB - 80 МБайт/с (теоретически достижимая - 132 Мбайт/с).

История

Как выглядит слот шины

Слот VLB был расширением шины ISA. Поэтому карты для шины ISA могли вставляться в слот VLB и работать. Это делало разъем довольно длинным, и из-за этого аббревиатура VLB в шутку расшифрововалась как Very Long Bus (Очень Длинная Шина). Дополнительная часть VLB разъёма была окрашена в светло-коричневый цвет, для неё использовался тот же самый 116-контактный разъём, что и для MicroChannel. Физический разъём (слот, форм-фактор) шины PCI практически совпадает с дополнительной частью разъёма VLB, но расположен у заднего края системной платы и имеет другие назначения выводов.

Технические подробности

VLB была расширением шины ISA только для процессоров Intel 80486 и использовала его технические особенности. По сути, на контакты дополнительного слота выходили физические линии системной шины (процессор-память). Таким образом, процессор мог напрямую обращаться к буферам и памяти контроллеров, работающих на VLB. Для процессора это выглядело как дополнительные модули обычной памяти (общее адресное пространство). Таким образом, процессор работал с устройством на тех же скоростях, что и с памятью (в то время как ISA использовала тактовую частоту 8 МГц и 16-битную шину), что и обеспечивало высокое быстродействие.

В случае процессоров Pentium и NexGen функциональность шины VLB реализовывалась с помощью дополнительных мостов в чипсете, что приводило к катастрофическому падению производительности.

В шинах видеоконтроллеров (AGP , PCI-Express) данный подход применяется до сих пор («северный мост » - микросхема, связывающая процессор, память и графическую шину).

В новых процессорах Intel и AMD доступ к памяти и графической шине осуществляется напрямую через контроллер, встроенный непосредственно в процессор.

Шина VLB практически перестала применяться вместе с процессором i486 и базовой шиной ISA, электрические и временные параметры которых использовала и расширением которых была.

Шина PCI не была конструктивно совместима ни с одной из предшественниц, разработана как дальнейшее развитие шин MicroChannel и SBus), и принципиально отличается от VLB большим количеством возможностей как по автоматической настройке аппаратуры, так и по удобству её использования, например, наличием прямого доступа к памяти (direct memory access , DMA ) - способностью шины в фоновом режиме (без участия процессора) переносить данные между буфером внешней платы и оперативной памятью . Кроме того, шина PCI не была так сильно привязана к определённому типу центрального процессора и могла обслуживать большее число разъёмов. Это предопределило вытеснение шины VLB шиной PCI.

Платы VLB, за редким исключением, не могли работать только в слоте ISA.