Posiadacze patentu RU 2559705:

Wynalazek dotyczy dziedziny techniki komputerowej, automatyki i może być stosowany w różnych strukturach cyfrowych i systemach automatycznego sterowania, transmisji informacji itp.

W różnych systemach obliczeniowych i sterowania szeroko stosowane są dekodery, realizowane w oparciu o logikę tranzystorowo-tranzystorową i emiterową, działające zgodnie z prawami algebry Boole'a i posiadające na wyjściu dwa stany logiczne „0” i „1”, charakteryzują się niskimi i wysokimi potencjałami. Klasyczna architektura dekodera została opublikowana w artykułach i książkach, mikroukłady są produkowane masowo.

Istotną wadą dekoderów tej klasy jest to, że ich elementy logiczne, wykorzystujące potencjalne sygnały binarne, mają wielopoziomową strukturę, która nie może lub jest nieefektywnie wykorzystywana w nowoczesnych niskonapięciowych procesach technologicznych, a także nieliniowość trybów pracy elementy i krytyczność parametrów struktury elementów logicznych i sygnałów wejściowych. Ostatecznie prowadzi to do spadku wydajności znanych dekoderów.

Jako urządzenia do przetwarzania informacji cyfrowych stosuje się również stopnie tranzystorowe do przetwarzania wejściowych zmiennych logicznych (prądów), realizowane w oparciu o zwierciadła prądowe, które realizują funkcję logicznego przetwarzania wejściowych zmiennych prądowych.

Istotną wadą znanych obwodów tej klasy jest to, że nie realizują one funkcji przetwarzania dwóch wejściowych sygnałów prądowych o czterech stanach „00”, „01”, „10”, „11” na cztery wyjściowe sygnały prądowe. Nie pozwala to na jej podstawie stworzyć kompletnej podstawy przetwarzania sygnałów ze zmiennymi prądowymi, działającej na zasadach algebry liniowej.

W artykułach, a także w monografiach współautora tej aplikacji pokazano, że algebra Boole'a jest szczególnym przypadkiem ogólniejszej algebry liniowej, praktyczne wdrożenie co w strukturze urządzeń obliczeniowych i logicznych nowej generacji automatyki wymaga stworzenia specjalnej bazy elementów, realizowanej w oparciu o logikę z dwuwartościową i wielowartościową wewnętrzną reprezentacją sygnałów, w której odpowiednik standardowym sygnałem logicznym jest bieżący kwant Ι 0. Zastrzeżone urządzenie „Dekoder 2 w 4” odnosi się do tego typu urządzeń logicznych i działa z wejściowymi sygnałami prądowymi i generuje wyjściowy sygnał prądowy.

Najbliższym prototypem zastrzeganego urządzenia jest urządzenie logiczne „Dekoder 2 w 4”, przedstawione w patencie US 5742154, zawierające pierwsze 1 i drugie 2 wejścia logiczne urządzenia, pierwsze 3, drugie 4, trzecie 5, czwarte 6 prądowe wyjścia logiczne urządzenia, pierwsze 7, drugie 8 i trzecie 9 tranzystorów wyjściowych, których podstawy są połączone i podłączone do pierwszego źródła napięcia polaryzacji 10, czwartego 11, piątego 12 i szóstego 13 tranzystorów wyjściowych innego typ przewodności, którego podstawy są połączone i połączone z drugim źródłem napięcia polaryzacji 14, emiter pierwszego tranzystora 7 wyjściowego połączony z emiterem czwartego tranzystora wyjściowego 11, emiter drugiego tranzystora 8 wyjściowego jest podłączony do emiter piątego tranzystora 12 wyjść, emiter trzeciego tranzystora 9 wyjść jest podłączony do emitera szóstego tranzystora 13 wyjścia, pierwsze 3 wyjścia logiki prądowej urządzenia są połączone z kolektorem pierwszego tranzystora 7 wyjść, drugie 4 prądowe wyjścia logiczne urządzeń a jest podłączony do kolektora trzeciego tranzystora 9-wyjściowego, kolektor czwartego tranzystora 11-wyjściowego jest podłączony do trzeciego 5-go wyjścia logiki prądowej urządzenia, kolektor szóstego tranzystora 13-wyjściowego jest podłączony do czwartej szóstej logiki prądowej wyjście urządzenia, pierwsze 15 i drugie 16 zwierciadeł prądowych, dopasowane do pierwszego źródła zasilania szyny 17, trzecie 18 zwierciadeł prądowych, dopasowane do drugiej linii 19 zasilacza, pomocnicze źródło prądu odniesienia 20.

Głównym celem niniejszego wynalazku jest stworzenie elementu logicznego, który zapewnia dekodowanie stanu dwóch wejściowych zmiennych logicznych i tworzenie czterech sygnałów wyjściowych w postaci bieżącej. Docelowo umożliwia to zwiększenie szybkości znanych urządzeń do konwersji informacji za pomocą proponowanego dekodera i tworzenia podstawa elementu urządzenia obliczeniowe działające na zasadach wielowartościowej algebry liniowej.

Problem rozwiązuje fakt, że w urządzeniu logicznym „Dekoder 2 do 4” (rys. 1), zawierającym pierwsze 1 i drugie 2 wejścia logiczne urządzenia, pierwsze 3, drugie 4, trzecie 5, czwarte 6, aktualne wyjścia logiczne urządzenia, pierwsze 7, drugie 8 i trzecie 9 tranzystorów wyjściowych, których podstawy są połączone i połączone z pierwszym 10 źródłem napięcia polaryzacji, czwartym 11, piątym 12 i szóstym 13 tranzystorów wyjściowych o różnym typie przewodności, których podstawy są połączone i podłączone do drugiego źródła napięcia polaryzacji 14, emiter pierwszego 7 wyjścia tranzystor jest podłączony do emitera czwartego ORAZ tranzystor wyjściowy, emiter drugi 8-wyjściowy tranzystor jest podłączony do emitera piątego 12-wyjściowego tranzystora, emiter trzeciego 9-wyjściowego tranzystora jest połączony z emiterem szóstego 13-go tranzystora wyjściowego, pierwsze 3 wyjścia logiki prądowej urządzenia są połączone z kolektor pierwszego tranzystora z 7 wyjściami, drugie 4 wyjścia logiki prądowej urządzenia są połączone z kolektorem trzeciego wyjścia 9 o tranzystorze, kolektor czwartego 11 tranzystora wyjściowego jest podłączony do trzeciego trzeciego wyjścia logiki prądowej urządzenia, kolektor szóstego tranzystora wyjściowego 13 jest podłączony do czwartego 6 wyjścia logiki prądowej urządzenia, pierwsze 15 i drugie 16 zwierciadeł prądowych dopasowanych do pierwszej szyny 17 zasilacza, trzecie 18 to zwierciadło prądowe dopasowane do drugiej szyny 19 zasilacza, źródło pomocnicze prądu odniesienia 20, przewidziano nowe elementy i połączenia - pierwsze 1 wejście logiczne urządzenia jest połączone z wejściem trzeciego 18 zwierciadła prądowego, drugie 2 wejścia logiczne urządzenia jest połączone z wejściem pierwszego 15 zwierciadła prądowego, pierwsze 21 wyjście prądowe pierwszych 15 zwierciadeł prądowych lustro jest połączone z połączonymi emiterami drugiego 8 i piątego 12 tranzystora wyjściowego i poprzez pomocnicze źródło prądu odniesienia 20 jest połączone z drugą szyną zasilającą 19, drugie 22 wyjście prądowe pierwszego 15 zwierciadła prądowego jest połączone z połączonym emitery pierwszego 7 i czwartego 11 tranzystora wyjściowego tranzystora ov i jest podłączony do pierwszego 23 wyjścia prądowego trzeciego 18 zwierciadła prądowego, kolektor drugiego 8 tranzystora wyjściowego jest podłączony do wejścia drugiego 16 zwierciadła prądowego, którego wyjście prądowe jest połączone z połączonymi emiterami trzeciego 9 i szóstego 13 tranzystora wyjściowego i jest podłączony do drugiego 24 wyjścia prądowego trzecich 18 zwierciadeł prądowych, a kolektor piątego wyjściowego tranzystora 12 jest podłączony do drugiej 19 szyny zasilacza.

Schematyczny diagram prototypowego urządzenia logicznego pokazano na FIG. 1. Na RYS. 2 przedstawia schemat zastrzeganego urządzenia zgodnie z zastrzeżeniem 1 zastrzeżeń.

FIGA. 3 przedstawia schemat zastrzeganego urządzenia zgodnie z klauzulą 2, klauzulą 3, klauzulą 4 zastrzeżeń.

FIGA. 4 pokazy Schemat obwodu Figa. 3 w środowisku Symulacja komputerowa MC9 ze specyficzną implementacją głównych jednostek funkcjonalnych (zwierciadła prądowe, referencyjne źródła prądowe).

FIGA. 5 przedstawia wyniki symulacji komputerowej obwodu z FIG. 4.

Urządzenie logiczne „Dekoder 2 na 4” z FIG. 2 zawiera pierwsze 1 i drugie 2 wejścia logiczne urządzenia, pierwsze 3, drugie 4, trzecie 5, czwarte 6 prądowych wyjść logicznych urządzenia, pierwsze 7, drugie 8 i trzecie 9 tranzystorów wyjściowych, których podstawy są połączone i połączone z pierwszym 10 źródłem napięcia polaryzacji, czwartym 11, piątym 12 i szóstym 13 tranzystorami wyjściowymi o innym typie przewodności, których podstawy są połączone i połączone z drugim 14 źródłem napięcia polaryzacji, emiterem pierwszego 7 tranzystor wyjściowy jest połączony z emiterem czwartego 11 tranzystora wyjściowego, emiter drugiego 8 tranzystora wyjściowego jest połączony z emiterem piątego tranzystora wyjściowego 12 tranzystora, emiter trzeciego 9 tranzystora wyjściowego jest połączony z emiterem szósty 13-wyjściowy tranzystor, pierwsze 3 wyjścia logiki prądowej urządzenia są połączone z kolektorem pierwszego 7 tranzystora wyjściowego, drugie 4 wyjścia logiczne prądowe urządzenia są połączone z kolektorem trzeciego 9-wyjściowego tranzystora, kolektor czwartego 11 tranzystora wyjściowego jest podłączone do trzeciego 5 prądu lo przez wyjście logiczne urządzenia kolektor szóstego 13 tranzystora wyjściowego jest połączony z czwartymi 6 prądowymi wyjściami logicznymi urządzenia, pierwsze 15 i drugie 16 zwierciadeł prądowych, dopasowane do pierwszej 17 szyny zasilacza, trzecie 18 zwierciadła prądowego, dopasowane do drugiej szyny 19 zasilacza, pomocnicze źródło prądu odniesienia 20. Pierwsze 1 wejście logiczne urządzenia jest połączone z wejściem trzeciego 18 zwierciadła prądowego, drugie 2 wejścia logiczne urządzenia jest podłączone do wejścia pierwszego 15 zwierciadła prądowego, pierwsze 21 wyjście prądowe pierwszego 15 zwierciadła prądowego jest połączone z połączonymi emiterami drugiego 8 i piątego 12 tranzystora wyjściowego i poprzez pomocnicze źródło prądu odniesienia 20 jest podłączone do drugiej szyny 19 zasilacza, drugie 22 wyjście prądowe pierwszego 15 zwierciadła prądowego jest połączone z połączonymi emiterami pierwszego 7 i czwartego 11 tranzystora wyjściowego i jest połączone z pierwszym 23 wyjściem prądowym trzeciego 18 lustro prądowe, kolektor drugiego tranzystora wyjściowego 8 jest podłączony od wejścia; dom drugiego 16 zwierciadła prądowego, którego wyjście prądowe jest połączone z połączonymi emiterami trzeciego 9 i szóstego 13 tranzystora wyjściowego i jest podłączone do drugiego 24 wyjścia prądowego trzeciego 18 zwierciadła prądowego, oraz kolektora Piąty 12 tranzystor wyjściowy jest podłączony do drugiej magistrali 19 zasilacza.

FIGA. 3 zgodnie z zastrzeżeniem 2 zastrzeżeń, pierwsze 1 wejście logiczne urządzenia jest połączone z wejściem trzeciego 18 zwierciadła prądowego przez pierwszy dodatkowy stopień odwracający wykonany w postaci pierwszego 26 dodatkowego zwierciadła prądowego dopasowanego do pierwszego 17 szyna zasilacza.

FIGA. 3 zgodnie z zastrzeżeniem 3 zastrzeżeń, kolektor czwartego tranzystora wyjściowego 11 jest połączony z trzecim wyjściem logiki prądowej 5 urządzenia poprzez drugi dodatkowy stopień odwracający wykonany w postaci drugiego 27 dodatkowego zwierciadła prądowego dopasowanego do druga szyna 19 zasilacza.

Ponadto na RYS. 3 zgodnie z zastrzeżeniem 4 zastrzeżeń, kolektor szóstego tranzystora wyjściowego 13 jest połączony z czwartym wyjściem logicznym 6 prądowym urządzenia poprzez trzeci dodatkowy stopień odwracający wykonany w postaci trzeciego dodatkowego zwierciadła prądowego 28 dopasowanego do druga szyna 19 zasilacza.

Rozważmy działanie proponowanego układu dekodera z wejściami i wyjściami prądowymi z FIG. 2.

Dekoder 2 w 4 realizuje dobrze znane funkcje:

gdzie A0, A¯0 są sygnałami bezpośrednimi i odwrotnymi na wejściu 1 urządzenia z FIG. 2,

A 1, A ¯ 1 - sygnały bezpośrednie i odwrotne na wejściu 2 urządzenia z FIG. 2.

Cechą ich implementacji w algebrze liniowej jest wykorzystanie do tego celu operacji obciętej różnicy:

którego tabela prawdy jest podana poniżej

Z tabeli wynika, że spośród czterech możliwych kombinacji wartości zmiennych wejściowych, jednostkowa wartość funkcji odpowiada tylko jednej kombinacji odpowiadającej warunkowi A 0> A 1. Określając w tabeli prawdy bezpośrednie i odwrotne zmienne wejściowe, można uzyskać wartość jednostkową funkcji odpowiadającą dowolnej z możliwych kombinacji wartości zmiennych wejściowych.

Zastosowanie tej operacji prowadzi do następującej reprezentacji funkcji logicznych dekodera:

Operacje te są realizowane w następujący sposób.

Sygnały zmiennych wejściowych A 0 i A 1 poprzez wejścia logiczne 1 i 2 są podawane do pierwszych 15 i trzecich 18 zwierciadeł prądowych, za pomocą których sygnały te są zwielokrotniane i zmieniany jest ich znak. W tym przypadku sygnał A 0 jest przesyłany w postaci płynącego prądu (tj. w postaci A 0) i za pomocą trzeciego zwierciadła prądowego 18 jest przekształcany na dopływający prąd (tj. do postaci -A 0), a A 1 jest dostarczany w postaci bezpośredniej w postaci prądu dopływającego (tj. w postaci -A 1) i za pomocą pierwszego zwierciadła prądowego 15 jest przekształcany w prąd wychodzący (tj. , do formularza A 1).

W punkcie połączenia wyjść 22 pierwszego zwierciadła prądowego 15 i 23 trzeciego zwierciadła prądowego 18 zaimplementowana jest operacja A1-A0. Sygnał różnicowy jest podawany do połączonych emiterów tranzystorów 7 i 11, których tryby pracy są ustalane przez pierwsze 10 i drugie 14 źródeł napięcia polaryzacji.

Jeśli sygnał różnicowy jest dodatni, tj. A 0 -A 1> 0, tranzystor 7 jest zamknięty, a tranzystor 11 jest otwarty, a kwant przepływającego prądu jest wyprowadzany na wyjście 5, co odpowiada - (A 0 -A 1) = A 1 -A 0, realizując wyrażenie (2). W przypadku jakichkolwiek innych kombinacji wartości bieżących kwantów na wyjściu 5 nie będzie prądu.

Jeśli A 0 -A 1 ≤ 0, wówczas tranzystor 7 jest otwarty, a tranzystor 11 jest zamknięty, a kwant przepływającego prądu jest wyprowadzany na wyjście 3, odpowiadające A 0 -A 1, które realizuje wyrażenie (3 ). W przypadku jakichkolwiek innych kombinacji wartości bieżących kwantów na wyjściu 3 nie będzie prądu.

W punkcie połączenia wyjścia 21 pierwszego zwierciadła prądowego i pomocniczego źródła prądu odniesienia 20 odejmowane jest A1-1. Sygnał różnicowy jest podawany do połączonych emiterów tranzystorów 8 i 12, których tryby pracy są ustalane przez pierwsze 10 i drugie 14 źródeł napięcia polaryzacji. Jeśli sygnał różnicowy jest dodatni, tj. A 1-1>0, tranzystor 8 jest wyłączony, a tranzystor 12 jest włączony. Jeżeli sygnał różnicowy jest mniejszy lub równy zero, wówczas tranzystor 8 jest włączony, a tranzystor 12 jest wyłączony.

W pierwszym przypadku sygnał przechodzący przez tranzystor 12 jest zwarty do masy. W drugim przypadku kwant wychodzącego prądu różnicowego A 1-1 za pomocą trzeciego zwierciadła prądowego 16 jest przekształcany w kwant prądu wychodzącego 1-A 1 i od niego odejmowany jest kwant prądu wpływającego -A 0 . Sygnał różnicowy jest podawany do połączonych emiterów tranzystorów 9 i 13, których tryby pracy są ustalane przez pierwsze 10 i drugie 14 źródeł napięcia polaryzacji. Jeśli sygnał różnicowy jest dodatni, tj. tranzystor 9 jest wyłączony, a tranzystor 13 jest włączony. W tym przypadku na wyjście 6 wyprowadzany jest sygnał różnicowy (1-A 1) -A 0 w postaci przepływającego kwantu prądu, który realizuje wyrażenie (4). W przypadku jakichkolwiek innych kombinacji wartości bieżących kwantów na wyjściu 4 nie będzie prądu.

Specyficzność to urządzenie jest reprezentacją sygnałów wyjściowych w postaci kwantów prądu wpływającego (na wyjściach 3 i 4) i wychodzącego (na wyjściach 5 i 6). W przypadku, gdy wymagane są wszystkie wyjścia w tym samym kierunku, obwód dekodera pokazany na FIG. 3. Jego różnica w stosunku do obwodu na RYS. 2 to zastosowanie dwóch dodatkowych zwierciadeł prądowych 27 i 28, do których wejść podłączone są kolektory tranzystorów 11 i 13, a wyjściami są wyjścia 5 i 6 dekodera. W rezultacie wszystkie sygnały wyjściowe są reprezentowane przez kwanty prądu przychodzącego.

Jak widać z powyższego opisu, implementacja urządzenia „2 w 4” odbywa się w postaci standardowych funkcji logicznych zgodnie z prawami algebry liniowej tworząc różnicę bieżących kwantów 10. Implementacja elementów na zwierciadłach prądowych pozwala w wielu przypadkach obniżyć napięcie zasilania, a ponieważ wszystkie obwody pracują w trybie aktywnym, przy założeniu braku nasycenia podczas procesu przełączania, ogólna wydajność urządzenia wzrasta. Zastosowanie stabilnych wartości kwantów prądu I 0, a także wyznaczenie sygnału wyjściowego różnicą tych prądów zapewnia niewielką zależność funkcjonowania układu od zewnętrznych czynników destabilizujących (odchylenie napięcia zasilania, promieniowania i wpływ temperatury, zakłócenia w trybie wspólnym itp.).

Pokazano na RYS. 9, ryc. 10 wyniki symulacji potwierdzają określone właściwości deklarowanych schematów.

Zatem rozważane rozwiązania obwodowe urządzenia logicznego „Dekoder 2 w 4” charakteryzują się binarną reprezentacją prądową sygnału i mogą być wykorzystane jako podstawa do obliczania i sterowania urządzeniami wykorzystującymi algebrę liniową, której szczególnym przypadkiem jest algebra Boole'a .

BIBLIOGRAFIA

1. Patent US 6243319 B1, ryc. 13.

2. Patent US 5604712 A.

3. Patent US 4514829 A.

4. Patent US 201200020179 A1.

5. Patent US 6920078 B2.

6. Patent US 6324117 B1, ryc. 3.

7. Zgłoszenie patentowe US 20040018019 A1.

8. Patent US 5568061 A.

9. Patent US 5148480 A, ryc. 4.

10. Brzozowski I., Zachara L., Kos A. Uniwersalna metoda projektowania dekoderów n-to-2n // Mixed Design of Integrated Circuits and Systems (MIXDES), 2013 Proceedings of the 20th International Conference, 2013. - P. 279 -284, ryc. 1.

11. Subramanyam M.V. Teoria przełączania i projektowanie logiki / Firewall Media, 2011. Po drugie, - 783 s, ryc. 3.174.

12. SN74LVC1G139 Dekoder linii 2 do 4 [zasób elektroniczny]. URL: http://www.ti.com/lit/ds/symlink/sn741vc1g139.pdf.

13. Patent US 8159304, ryc. 5.

14. Patent USA nr 5977829, ryc. 1.

15. Patent USA nr 5789982, ryc. 2.

16. Patent USA nr 5140282.

17. Patent USA nr 6624701, ryc. 4.

18. Patent USA nr 6529078.

19. Patent USA nr 5734294.

20. Patent USA nr 5557220.

21. Patent USA nr 6624701.

22. Patent RU nr 2319296.

23. Patent RU nr 2436224.

24. Patent RU nr 2319296.

25. Patent RU nr 2321157.

26. Patent US 6556075, ryc. 2.

27. Patent US 6556075, ryc. 6.

28. Chernov N.I., Yugai V.Y., Prokopenko N.N. i inni Podstawowa koncepcja syntezy liniowej wielowartościowych struktur cyfrowych w przestrzeniach liniowych // XI sympozjum East-West Design & Test (EWDTS 2013). - Rostów nad Donem, 2013. - C. 146-149.

29. Malyugin V. D. Implementacja funkcji logicznych za pomocą wielomianów arytmetycznych // Automation and Remote Control, 1982. nr 4. S. 84-93.

30. Czernow N.I. Podstawy teorii syntezy logicznej struktur cyfrowych na polu liczb rzeczywistych // Monografia. - Taganrog: TRTU, 2001 .-- 147 s.

31. Czernow N.I. Synteza liniowa struktur cyfrowych ASOIU "// Tutorial. - Taganrog: TRTU, 2004 - 118 pkt.

1. Dekoder 2 na 4, zawierający pierwsze (1) i drugie (2) wejścia logiczne urządzenia, pierwsze (3), drugie (4), trzecie (5), czwarte (6) prądowe wyjścia logiczne urządzenia , pierwszy (7), drugi (8) i trzeci (9) tranzystory wyjściowe, których podstawy są połączone i podłączone do pierwszego (10) źródła napięcia polaryzacji, czwartego (11), piątego (12) i szóstego (13) tranzystory wyjściowe o innym typie przewodności, których podstawy są połączone i podłączone do drugiego (14) źródła napięcia polaryzacji, emiter pierwszego (7) tranzystora wyjściowego jest podłączony do emitera czwartego (11 ) tranzystor wyjściowy, emiter drugiego (8) tranzystora wyjściowego jest połączony z emiterem piątego (12) tranzystora wyjściowego, emiter trzeciego (9) tranzystora wyjściowego jest połączony z emiterem szóstego (13) tranzystor wyjściowy, pierwsze (3) wyjście logiki prądowej urządzenia jest połączone z kolektorem pierwszego (7) tranzystora wyjściowego, drugie (4) wyjście logiki prądowej urządzenia jest połączone z kolektorem trzeciego (9) tranzystor wyjściowy, kolektor Czwarty (11) tranzystor wyjściowy jest podłączony do trzeciego (5) wyjścia logiki prądowej urządzenia, kolektor szóstego (13) tranzystora wyjściowego jest podłączony do czwartego (6) wyjścia logiki prądowej urządzenia, pierwsze ( 15) i drugie (16) zwierciadła prądowe są dopasowane do pierwszej (17) szyny zasilacza, trzecie (18) zwierciadła prądowe dopasowane do drugiej (19) szyny zasilacza, pomocnicze źródło prądu odniesienia (20), charakteryzujący się tym, że pierwsze (1) wejście logiczne urządzenia jest połączone z wejściem trzeciego (18) aktualnego lustra, drugie (2) wejście logiczne urządzenia jest połączone z wejściem pierwsze (15) zwierciadło prądowe, pierwsze (21) wyjście prądowe pierwszego (15) zwierciadła prądowego jest połączone z połączonymi emiterami drugiego (8) i piątego (12) tranzystora wyjściowego oraz poprzez pomocnicze źródło prądu odniesienia (20 ) jest podłączony do drugiej (19) szyny zasilającej, drugie (22) wyjście prądowe pierwszego (15) zwierciadła prądowego jest podłączone do połączonych emiterów pierwszego (7) i czwartego (11) wyjścia tranzystorów i podłączony do pierwszego (23) wyjścia prądowego trzeciego (18) zwierciadła prądowego, kolektor drugiego (8) tranzystora wyjściowego jest podłączony do wejścia drugiego (16) zwierciadła prądowego, którego wyjście prądowe jest podłączony do połączonych emiterów trzeciego (9) i szóstego (13) tranzystora wyjściowego i podłączony do drugiego (24) wyjścia prądowego trzeciego (18) zwierciadła prądowego, a kolektor piątego (12) tranzystora wyjściowego jest podłączony do drugiej (19) szyny zasilającej.

2. Dekoder 2 do 4 według zastrzeżenia 1, znamienny tym, że pierwsze (1) wejście logiczne urządzenia jest połączone z wejściem trzeciego (18) zwierciadła prądowego poprzez pierwszy dodatkowy stopień odwracający, wykonany w postaci pierwsze (26) dodatkowe lustro prądowe, dopasowane do pierwszej (17) szyny zasilającej.

3. Dekoder 2 do 4 według zastrzeżenia 1, znamienny tym, że kolektor czwartego (11) tranzystora wyjściowego jest połączony z trzecim (5) logicznym wyjściem prądowym urządzenia poprzez drugi dodatkowy stopień odwracający, wykonany w postaci drugie (27) dodatkowe lustro prądowe, dopasowane do drugiej (19) szyny zasilającej.

4. Dekoder 2 do 4 według zastrzeżenia 1, znamienny tym, że kolektor szóstego (13) tranzystora wyjściowego jest połączony z czwartym (6) logicznym wyjściem prądowym urządzenia poprzez trzeci dodatkowy stopień odwracający, wykonany w postaci trzecie (28) dodatkowe lustro prądowe, dopasowane do drugiej (19) szyny zasilającej.

Podobne patenty:

Wynalazek dotyczy środków do kodowania wykorzystujących zredukowany słownik z instalacja adaptacyjna do pozycji wyjściowej. Wynik techniczny polega na zmniejszeniu ilości informacji przesyłanych ze strony odbiorczej do strony nadawczej.

Wynalazek dotyczy informatyki, a mianowicie kodowania informacji wideo. Efektem technicznym jest zwiększenie wydajności kodowania i dekodowania strumienia bitów informacji wideo poprzez podział danych na warstwy entropii.

Wynalazek dotyczy sposobu kodowania sekwencji liczb całkowitych, urządzenia pamięciowego i sygnału przenoszącego taką zakodowaną sekwencję, jak również sposobu dekodowania tej zakodowanej sekwencji.

Wynalazek dotyczy sposobu wstępnego kodowania, jak również systemu i sposobu konstruowania książki kodowania wstępnego w systemie z wieloma wejściami i wieloma wyjściami (MIMO).

Wynalazek dotyczy dziedziny technologii, która wykorzystuje sygnały cyfrowe i może być stosowana w urządzeniach komunikacyjnych, rejestracji, nagrywaniu, odtwarzaniu, konwersji, kodowaniu i kompresji sygnałów, automatycznych systemach sterowania.

Wynalazek dotyczy dziedziny telekomunikacji, a mianowicie dziedziny urządzeń kryptograficznych i sposobów sprawdzania elektroniki podpis cyfrowy(EDS). ...

Wynalazek dotyczy dziedziny przetwarzania sygnałów cyfrowych, w szczególności kompresji danych i poprawy kodowania entropijnego sekwencji wideo. Rezultatem technicznym jest zwiększenie wydajności i zmniejszenie złożoność obliczeniowa kodowanie entropijne. Sposób przetwarzania strumienia danych składającego się z wielu elementów syntaktycznych polega na zastępowaniu elementów syntaktycznych, których wartości mają duże prawdopodobieństwo wystąpienia, elementami syntaktycznymi, których wartości mają małe prawdopodobieństwo. Kontekst jest definiowany dla elementu składni i obliczane jest prawdopodobieństwo wystąpienia wartości tych elementów składni w modelu przepływu danych, które mają określony kontekst. Zastąp elementy składni strumienia danych, które mają określony kontekst, jeśli obliczone prawdopodobieństwo wystąpienia wartości elementu składni jest wyższe niż określony próg, elementami składni, których wartości mają niskie prawdopodobieństwo. 3 rz. i 10 c.p. f-kryształy, 4 rys., 2 tbl.

Wynalazek dotyczy techniki komunikacyjnej i jest przeznaczony do pomiaru widma informacyjnych sygnałów akustycznych. Efektem technicznym jest zwiększenie dokładności pomiaru widma dźwiękowych sygnałów informacyjnych, rozwinięcie funkcjonalność urządzenia ze względu na powiązanie wartości chwilowych widma z segmentami czasowego sygnału akustycznego o regulowanym czasie trwania. W tym celu metoda pomiaru widma wykorzystuje dyskretną transformatę cosinus (DCT) zamiast szybkiej transformaty Fouriera (FFT), co umożliwia zwiększenie dokładności pomiaru widma sygnałów akustycznych poprzez zwiększenie rozdzielczości, zmniejszenie poziomu przekształcenia bocznych listków okna w widmie, oraz zmniejszenie oscylacji oszacowania amplitudy składowych widmowych, a także pozwala skrócić czas trwania segmentów sygnału akustycznego, na których mierzone jest chwilowe widmo, podczas gdy realizowane jest tworzenie dwóch sygnałów (głównego i dodatkowego) zamiast jednego, a dodatkowy cyfrowy sygnał akustyczny jest ortogonalny względem głównego, mierzone wartości chwilowe widma są również powiązane, moduł widmo i charakterystykę fazowo-częstotliwościową sygnału do segmentów czasowego sygnału akustycznego, z możliwością regulacji położenia w czasie i czasu trwania, na którym to widmo jest mierzone. 2 n.p. mucha, 8 dwg

Wynalazek dotyczy bezprzewodowy... Rezultatem technicznym jest zwiększenie odporności na zakłócenia, niezawodności i wydajności komunikacji przy jednoczesnym zmniejszeniu zużycia energii. W tym celu sposób obejmuje: etap S1, w którym urządzenie nadrzędne generuje kod sekwencji przez określony koder i przesyła kod sekwencji do każdego urządzenia podrzędnego w sposób ciągły przez z góry określony czas zgodnie z żądaniem komunikacji, przy czym konkretny koder jest przesunięciem Zarejestruj się z sprzężenie zwrotne wykonywane dla określonego wielomianu, którego kolejność i współczynniki są skorelowane z żądaniem komunikacji, natomiast wszystkie współczynniki i Wartości początkowe nie jest równy 0 w tym samym czasie; z góry określony okres czasu jest większy lub równy sumie okresu uśpienia i okresu wykrywania urządzenia podrzędnego, co stanowi cykl uśpienia i przebudzenia; etap S2, w którym urządzenie podrzędne odbiera ciągłą część kodu sekwencji w okresie wykrywania, dekoduje kod sekwencji przez dekoder odpowiadający koderowi i wykonuje odpowiednią operację zgodnie z wynikiem dekodowania. 2 rz. i 10 c.p. mucha, 5 dwg

Wynalazek dotyczy technologii komunikacyjnej i jest przeznaczony do kodowania i dekodowania sygnałów. Efektem technicznym jest poprawa dokładności kodowania i dekodowania sygnałów. Sposób kodowania sygnału obejmuje uzyskanie sygnału w dziedzinie częstotliwości zgodnie z sygnałem wejściowym; przydzielanie z góry określonych bitów do sygnału w dziedzinie częstotliwości zgodnie z ustaloną regułą alokacji; regulowanie przydziału bitów dla sygnału w dziedzinie częstotliwości, gdy najwyższa częstotliwość sygnału w dziedzinie częstotliwości, do której przydzielane są bity, przekracza z góry określoną wartość; oraz kodowanie sygnału w dziedzinie częstotliwości zgodnie z przydziałem bitów dla sygnału w dziedzinie częstotliwości. 4 rz. i 16 c.p. mucha, 9 chor.

Wynalazek dotyczy dziedziny telekomunikacji i jest przeznaczony do ochrony przesyłanych tajnych informacji. Efektem technicznym jest wysoki poziom bezpieczeństwa zaszyfrowanych informacji. Metoda szyfrowania informacji, w tym budowa tablicy odpowiedników symboli i ich odpowiedników w przestrzeni (00; FF) w systemie liczb szesnastkowych, generowanie nowy stół dopasowania, zmieniając oryginalną tabelę, przesuwając oryginalną tabelę, tj. ciąg dopasowania jest przesuwany o określoną liczbę znaków, informacje źródłowe są kodowane i kompresowane do żądanego rozmiaru przy użyciu odpowiedniej tabeli kodowania Unicode. 2 zakładka.

SUBSTANCJA: wynalazek dotyczy kodowania/dekodowania sygnału cyfrowego składającego się z kolejnych bloków próbek. Efektem technicznym jest poprawa jakości kodowanego dźwięku. Kodowanie obejmuje zastosowanie okna ważenia do dwóch bloków M kolejnych próbek. W szczególności takie okno ważenia jest asymetryczne i zawiera cztery oddzielne sekcje, ciągnące się sekwencyjnie wzdłuż dwóch wyżej wymienionych bloków, przy czym pierwsza sekcja wzrasta w pierwszym przedziale czasowym, druga sekcja ma stałą wartość ważenia w drugim przedziale czasowym, trzecia sekcja malejąca wraz z biegiem trzeciego przedziału czasowego, a czwarta część ma stałą wartość ważenia podczas czwartego przedziału czasowego. 6 rz. i 11 c.p. mucha, 10 chor.

Wynalazek dotyczy dziedziny przetwarzania sygnałów cyfrowych, w szczególności sposobów kodowania-dekodowania cyfrowych obrazów wideo. Wynikiem technicznym jest zwiększenie współczynnika kompresji obrazów wideo z niewielkim spadkiem jakości dekodowanego obrazu, stosowanego do obrazów o wysokiej częstotliwości charakteru widma sygnału. Zaproponowano metodę kodowania-dekodowania cyfrowych obrazów wideo. Zgodnie z tą metodą, w procesie kodowania dodatkowa składowa wysokiej częstotliwości jest dodawana linia po linii do składowej niskiej częstotliwości transformacji falkowej, aby wygładzić oryginalną funkcję, która jest używana do kodowania, ale jest tłumiona po stronie dekodowania za pomocą filtra dolnoprzepustowego. Ponadto kodowanie realizowane jest z wykorzystaniem funkcji, której celem jest zwiększenie stopnia kompresji danych i zachowanie jakości dekodowanego obrazu, a charakterystyki filtra dekodera są brane pod uwagę jako ograniczenie komunikacji na etapie kodowania. 8 dwg, 3 łyżki

Wynalazek dotyczy dziedziny komunikacji bezprzewodowej. Efektem technicznym jest poprawa jakości komunikacji poprzez tłumienie kolejnych zakłóceń pomiędzy strumieniami sygnału. Sposób wstępnego kodowania obejmuje: wykonanie wstępnego przetwarzania wstępnego kodowania na sygnale, który ma być przesłany, przy czym wstępne przetwarzanie powoduje wzrost mocy przesyłanego sygnału; wybór algorytmu ograniczania mocy zgodnie z regułą wyboru; wykonywanie operacji ograniczania mocy na wstępnie przetworzonym sygnale zgodnie z wybranym algorytmem ograniczania mocy; oraz generowanie wstępnie zakodowanego sygnału zgodnie z sygnałem o ograniczonej mocy. Przykład wykonania niniejszego wynalazku ujawnia ponadto nadajnik, odbiornik i system wstępnego kodowania. W niniejszym wynalazku niekorzystny wpływ wywierany przez operację ograniczania mocy na transmisję sygnału można zmniejszyć tak bardzo, jak to możliwe, podczas gdy moc transmisji jest ograniczana przez zastosowanie operacji ograniczania mocy. 5 rz. i 12 pkt. mucha, 8 dwg

Niniejszy wynalazek dotyczy dziedziny kodowania i dekodowania i jest przeznaczony do kwantyzacji wektorów obwiedni częstotliwości. EFEKT: zwiększona wydajność kwantyzacji wektorów obwiedni częstotliwości. Sposób obejmuje: podzielenie N obwiedni częstotliwości w jednej ramce na N1 wektorów, gdzie każdy wektor w N1 wektorach zawiera M obwiedni częstotliwości; kwantowanie pierwszego wektora w N1 wektorach przy użyciu pierwszego słownika w celu uzyskania słowa kodowego odpowiadającego skwantowanemu pierwszemu wektorowi, przy czym wspomniany pierwszy słownik jest podzielony na sekcje 2B1; określanie zgodnie ze słowem kodowym odpowiadającym skwantowanemu pierwszemu wektorowi, że skwantowany pierwszy wektor jest powiązany z i-tym regionem w regionach 2B1 wspomnianego pierwszego słownika; określanie drugiego słownika zgodnie ze słownikiem i-tego regionu; oraz kwantowanie drugiego wektora na wektory N1 w oparciu o wspomniany drugi słownik. W przykładach wykonania niniejszego wynalazku obwiednie częstotliwości są podzielone na wiele wektorów o mniejszych wymiarach tak, że kwantyzacja wektorowa może być przeprowadzana na wektorach obwiedni częstotliwości przy użyciu słownika z mniejszą liczbą bitów. 2 rz. i 6 c.p. mucha, 3 dwg

Grupa wynalazków dotyczy dziedziny kodowania. Efektem technicznym jest poprawa wydajności kompresji danych. Sposób kodowania danych wejściowych (D1) obejmuje definiowanie zasadniczo powtarzających się bloków danych i/lub pakietów danych w co najmniej jednym z fragmentów danych wejściowych (D1), przy czym bloki danych i/lub pakiety danych zawierają odpowiednią liczbę elementów , gdzie elementy zawierają wiele bitów; określanie, czy elementy w zasadniczo powtarzających się blokach danych i/lub pakietach danych są niezmienione i/lub określanie, że elementy w zasadniczo powtarzających się blokach danych i/lub pakietach danych zmieniają się; kodowanie niezmienionych elementów do zakodowanych danych (E2) przy użyciu co najmniej jednego odpowiadającego symbolu lub co najmniej jednego odpowiedniego bitu, wskazując, że nie ma zmiany w niezmienionych elementach w porównaniu z odpowiadającymi im elementami w bloku danych odniesienia i/lub pakiecie danych; oraz kodowanie zmienionych elementów w zakodowane dane (E2). 6 rz. i 28 z.p. mucha, 8 dwg

Wynalazek dotyczy dekoderów. Efektem technicznym jest zwiększenie szybkości urządzeń do konwersji informacji za pomocą nowatorskiego dekodera. Pierwsze wejście logiczne urządzenia jest połączone z wejściem trzeciego zwierciadła prądowego, drugie wejście logiczne urządzenia jest połączone z wejściem pierwszego zwierciadła prądowego, pierwsze wyjście prądowe pierwszego zwierciadła prądowego jest połączone z połączonym emitery drugiego i piątego tranzystora wyjściowego i poprzez pomocnicze referencyjne źródło prądu są podłączone do drugiej szyny źródła zasilania, drugie wyjście prądowe pierwszego zwierciadła prądowego jest połączone z połączonymi emiterami pierwszego i czwartego tranzystora wyjściowego i jest podłączony do pierwszego wyjścia prądowego trzeciego zwierciadła prądowego, kolektor drugiego tranzystora wyjściowego jest podłączony do wejścia drugiego zwierciadła prądowego, którego wyjście prądowe jest połączone z połączonymi emiterami trzeciego i szóstego tranzystora wyjściowego i jest połączony z drugim wyjściem prądowym trzeciego zwierciadła prądowego, a kolektor piątego tranzystora wyjściowego jest podłączony do drugiej szyny zasilacza. 3 rz. mucha, 5 dwg

3. Schemat funkcjonalny, konwencjonalne oznaczenie graficzne i tablica prawdy kompletnego dekodera dla 3 wejść.

4. Dekodery liniowe: funkcja przełączania, UGO i obwód.

5. Dekodery piramidalne: funkcja przełączania, UGO i obwód.

6. Wielostopniowe dekodery prostokątne: funkcja przełączania, UGO i obwód.

7. Dekodery taktowane i zintegrowane.

Dekoder to kombinowana jednostka operacyjna, która zamienia słowo wejściowe na sygnał na jednym ze swoich wyjść.

Zatem dekoder jest węzłem, w którym każda kombinacja sygnałów wejściowych odpowiada obecności sygnału na jednym z wyjść.

Rysunek 4 przedstawia schemat funkcjonalny dekodera z n wejściami i 2 n -1 wyjściami.

Technika syntezy dekodera

Warunki pracy dekodera dla dwóch wejść można przedstawić za pomocą tabeli prawdy (tabela 3). Liczba wyjść takiego dekodera to m = 2 2 = 4.

|

Tabela 3 |

||||||||||||||||||||||||||||||||||||

|

Tabela prawdy dekodera 2 × 4

|

||||||||||||||||||||||||||||||||||||

Funkcje przełączania wyjść dekodera zgodnie z tą tabelą prawdy zostaną zapisane w następujący sposób:

Przekształcamy wyrażenia (4) do implementacji w bazie NAND:

Warunkowe obrazy dekodera używanego w budownictwie schematy funkcjonalne, pokazano na Fig. 7, gdzie a jest ogólnym oznaczeniem dekodera; b - oznaczenie dekodera macierzowego. Wejścia dekodera oznaczone są liczbami dziesiętnymi reprezentującymi wagi binarne, wyjścia - obrazami dziesiętnymi odpowiednich kombinacji kodów.

Oznaczenie dekoderów: 155 NS 1, 555NS 6 itd.

3. Analiza działania scramblera

Cel i zasada działania enkoderów.

Rozpatrzenie sprawy odbywa się poprzez przeprowadzanie wywiadów z uczniami z ich miejsc i przy tablicy zgodnie z następującym planem:

Spotkanie

Tabela prawdy

Metody syntezy obwodów

Przykłady najprostszych schematów

Pytania skierowane do stażystów

Szyfratory:

1. Cel, logika działania i klasyfikacja scramblerów.

2. Schemat funkcjonalny, konwencjonalne oznaczenie graficzne i tablica prawdy enkodera dla n wejść.

3. Schemat funkcjonalny, konwencjonalne oznaczenie graficzne i tabela prawdy enkodera dla 4 wejść.

4. Synteza scramblerów w różnych bazach.

5. Zasady budowania szyfratorów priorytetów.

Mieszaniec jest jednostką funkcjonalną komputera cyfrowego i jest przeznaczony do konwersji jednolitego kodu (kodu, w którym tylko jedna zmienna przyjmuje pojedynczą wartość) na pewien (binarny) kod pozycyjny.

Innymi słowy, scrambler wykonuje funkcje przeciwne do funkcji deszyfratora.

Kompletny enkoder ma 2 m wejść i m wyjść. W tym przypadku, jeżeli do jednego z obwodów wejściowych enkodera doprowadzony zostanie sygnał wejściowy, to na jego wyjściach powstaje słowo odpowiadające numerowi obwodu wzbudzonego.

Synteza równoważnego kodera

Niech m = 2, to liczba wejść enkodera wynosi cztery. Tabela działania takiego enkodera będzie wyglądać następująco (Tabela 4).

|

Tabela 4 |

||||||||||||||||||||||||||||||

|

Tabela stanów enkodera 4 × 2

Priorytetowa synteza scramblera Rozważ zasadę działania enkodera „4 × 2 ". Tabela prawdy dla tego enkodera jest przedstawiona w tabeli. 5. Z tabeli widać, że przy konstruowaniu enkodera priorytetowego używane są zestawy 1, 2, 4 i 8, dla pozostałych zestawów funkcja przyjmuje obojętną wartość - F. | ||||||||||||||||||||||||||||||

.

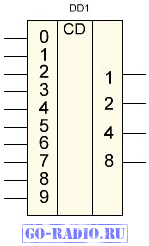

Mikroukład K176ID1, K561ID1

Częściowy dekoder BCD ma 4 wejścia do odbioru kodu binarnego i 10 wyjść dla jego dziesiętnego odpowiednika.

Aktywny poziom wejścia i wyjścia jest wysoki. Gdy do mikroukładu zostanie zastosowany kod binarny w zakresie 8-15, na wszystkich wyjściach ustawiany jest niski poziom logiczny (dekodowanie nie jest wykonywane). Mikroukład nie ma dodatkowych wejść do strobowania, jednak rozszerzenie szerokości bitowej jest łatwe do zaimplementowania, jeśli poświęcisz ostatnie dwa miejsca po przecinku:

Na powyższym schemacie odwrócony najbardziej znaczący bit kodu wejściowego jest używany jako sygnał strobujący dla DD2. W tym przypadku piny 4,5 (najbardziej znaczące miejsca dziesiętne 8,9) mikroukładów nie są używane, a obwód jest pełnym 4-bitowym dekoderem BCD.

Na poniższym rysunku, dzięki zastosowaniu oddzielnego mikroukładu do sterowania dekoderami, liczba wyjść została zwiększona do 64 (6-bajtowy kod wejściowy).

——————————————-

Mikroukład K176ID2

Dekoder-konwerter. Zaprojektowany do konwersji kodu binarnego na kod dla wskaźnika siedmiosegmentowego. W mikroukładzie nie ma obwodów do kontrolowania przecinka dziesiętnego. Oprócz samego dekodera mikroukład ma wyzwalacz zatrzaskowy, który pozwala zapamiętać bieżące dane.

Posiada czterocyfrowe wejście danych i siedem wyjść do podłączenia siedmiosegmentowego wskaźnika cyfrowego. Aktywne poziomy wejścia i wyjścia są wysokie, ale w razie potrzeby można je odwrócić sygnałem na wejściu serwisowym S. Przy niskim poziomie na tym wejściu aktywny sygnał wyjściowy jest wysoki, z „1” na S , jest niski. Pozwala to na podłączenie matryc cyfrowych zarówno ze wspólną anodą, jak i wspólną katodą bez dodatkowych falowników. Kolejne wejście serwisowe K służy do sterowania matrycą. „0” na wejściu K włącza wyświetlanie, „1” wygasza matrycę.

A trzecie wejście usługi C służy do zatrzaśnięcia informacji wchodzącej do wejścia dekodera. Gdy poziom C jest wysoki, sygnał jest natychmiast dekodowany i podawany do wskaźnika. Gdy zmienisz go na „0”, kod wejścia zostanie zatrzaśnięty i wyświetlony niezależnie od zmian na wejściu, dopóki poziom na wejściu C nie wzrośnie ponownie. Zapamiętywanie następuje przy spadku wysokiego poziomu.

Przełączniki wyjściowe mikroukładu K176ID2 są w stanie wytrzymać prądy zwarciowe liczbowo równe poziomowi napięcia zasilania (w mA) i dlatego mogą być ładowane bezpośrednio na wskaźniki LED (na przykład AL305, ALS324, ALS321) bez dodatkowego prądu wzmacniacze.

Mikroukład K176IDZ

Kompletny analog K176ID2 pod względem pinoutu i algorytmu działania. Różnica polega na przełącznikach wyjściowych otwartego drenu. Umożliwia to bezpośrednie podłączenie anod wskaźników fluorescencyjnych wymagających stosunkowo wysokiego napięcia (do 15 V) do ich zasilania do wyjścia dekodera. W przypadku korzystania z mikroukładu wraz z takimi wskaźnikami, dziennik należy przesłać do wejścia serwisowego S. „0”.

——————————————-

Mikroukład 564ID4

Dekoder-konwerter. Zaprojektowany do konwersji kodu binarnego na kod dla wskaźnika siedmiosegmentowego (w tym LCD). Nie ma łańcuchów do kontrolowania przecinka dziesiętnego.

Główną różnicą w stosunku do K176ID2 jest obecność trzeciego wyjścia do zasilania przełączników wyjściowych, które wytrzymują napięcie do 15 V. W przypadku przeciwfazowego zasilania wyświetlacza LCD znajduje się specjalny wzmacniacz (wejście S, wyjście P). Rozważmy bardziej szczegółowo jego pracę na przykładzie podłączenia wskaźnika LCD IZhKTs1-1 / 18.

Główną różnicą w stosunku do K176ID2 jest obecność trzeciego wyjścia do zasilania przełączników wyjściowych, które wytrzymują napięcie do 15 V. W przypadku przeciwfazowego zasilania wyświetlacza LCD znajduje się specjalny wzmacniacz (wejście S, wyjście P). Rozważmy bardziej szczegółowo jego pracę na przykładzie podłączenia wskaźnika LCD IZhKTs1-1 / 18.

Załóżmy, że sam dekoder, podobnie jak wszystkie poprzednie węzły urządzenia, jest zasilany napięciem 5 V (pin 16), a wskaźnik LCD wymaga Napięcie AC o amplitudzie 15 V. Aby uporządkować zasilanie wyświetlacza LCD, postępujemy następująco: do pinu 7 dostarczamy 15 V (trzeci pin zasilania), a do pinu 6 (wejście S) sygnał poziomu TTL (5 V ) i częstotliwości 100 Hz. Sygnał ten trafia do pinu 1 (pin P) bez inwersji, ale jego amplituda wzrasta do napięcia 15 V.

Załóżmy, że sam dekoder, podobnie jak wszystkie poprzednie węzły urządzenia, jest zasilany napięciem 5 V (pin 16), a wskaźnik LCD wymaga Napięcie AC o amplitudzie 15 V. Aby uporządkować zasilanie wyświetlacza LCD, postępujemy następująco: do pinu 7 dostarczamy 15 V (trzeci pin zasilania), a do pinu 6 (wejście S) sygnał poziomu TTL (5 V ) i częstotliwości 100 Hz. Sygnał ten trafia do pinu 1 (pin P) bez inwersji, ale jego amplituda wzrasta do napięcia 15 V.

Ten sam sygnał, gdy poziom jest aktywny (logika 1), odwraca sygnały z wyjścia dekodera (podobnie do 176ID2,3). Ponieważ przełączniki wyjściowe mikroukładu są zasilane ze źródła 15 V, poziom na nich zmieni się od 0 do 15 V z częstotliwością 100 Hz i w przeciwfazie z sygnałem P. W ten sposób napięcie przemienne będzie obecne na aktywne segmenty wskaźnika, a 0 na nieaktywnych.

Należy zauważyć, że dekoder jest kompletny – tj. w stanie wyświetlać nie tylko liczby od 0 do 9, ale także symbole „L”, „H”, „P”, „A”, „-” odpowiadające kodowi binarnemu 10-14. Przy kodzie 15 wszystkie segmenty są wygaszone.

Chociaż głównym celem mikroukładu jest sterowanie wskaźnikiem LCD, jego moc wyjściowa wystarcza do zapalenia matrycy LED (przy napięciu zasilania do 10 V - nawet bez rezystorów ograniczających prąd). Zmieniając poziom na wejściu S, można zasilić matryce zarówno wspólną anodą, jak i wspólną katodą. W tym przypadku wyjście P nie jest używane.

——————————————-

Mikroukład 564ID5

Dekoder różni się od 564ID4 brakiem wyjścia P i posiada czterobitowy rejestr zatrzaskowy podobny do K176ID2.

Rejestr sterowany jest przez wejście C: „1” – bezpośrednie przejście kodu do dekodera a następnie do wyjść do podłączenia segmentów wskaźnika, „0” – podtrzymanie informacji do wyświetlenia. W tym trybie mikroukład nie reaguje na zmianę kodu binarnego na wejściu. Zatrzaskiwanie informacji następuje w momencie spadku poziomu na wejściu C.

Ciekawą cechą dekoderów K176ID2, K176ID3, 564ID4 i 564ID5 jest to samo okablowanie pinów wejściowych i wyjściowych o tej samej nazwie.

——————————————-

Mikroukład KR1561ID6

Jedna obudowa mikroukładu zawiera dwa niezależne dekodery BCD dla dwóch wejść i czterech wyjść. Każdy dekoder wyposażony jest w wejście bramkujące.

Poziomy aktywnych wejść i wyjść są wysokie, a wejścia bramkowane są niskie. Przy "0" na wejściu S działa dekoder (na wyjściu pojawia się dziesiętny odpowiednik kodu wejściowego), przy "1" - wszystkie wyjścia są ustawione na "0".

Poziomy aktywnych wejść i wyjść są wysokie, a wejścia bramkowane są niskie. Przy "0" na wejściu S działa dekoder (na wyjściu pojawia się dziesiętny odpowiednik kodu wejściowego), przy "1" - wszystkie wyjścia są ustawione na "0".

Mikroukład KR1561ID7

Kompletny analog KR1561ID6 pod względem okablowania i algorytmu działania, ale na wyjściach obu dekoderów zainstalowane są falowniki (aktywny poziom wyjściowy jest niski).

Ze względu na obecność odwróconych wyjść, mikroukład idealnie nadaje się do sterowania większością dekoderów CMOS, gdy są one połączone kaskadowo. Na poniższym rysunku w obwodzie sterującym grupy K561ID1 zastosowano jeden dekoder mikroukładu KR1561ID7, co umożliwiło zbudowanie dekodera z 32 wyjściami tylko w pięciu przypadkach.

Ze względu na obecność odwróconych wyjść, mikroukład idealnie nadaje się do sterowania większością dekoderów CMOS, gdy są one połączone kaskadowo. Na poniższym rysunku w obwodzie sterującym grupy K561ID1 zastosowano jeden dekoder mikroukładu KR1561ID7, co umożliwiło zbudowanie dekodera z 32 wyjściami tylko w pięciu przypadkach.

Aby zbudować kompletny dekoder na 8 wyjść do mikroukładu KR1561ID6 (kod wyjściowy - bezpośredni) lub KR1561ID7 (kod wyjściowy - odwrotny), wystarczy dodać tylko jeden falownik:

——————————————-

Urządzenia logiczne dzielą się na dwie klasy: kombinacyjną i sekwencyjną.

Urządzenie nazywa się kombinacyjny jeśli jego sygnały wyjściowe w określonym momencie są jednoznacznie określone przez sygnały wejściowe, które występują w tym momencie.

W przeciwnym razie urządzenie nazywane jest maszyną sekwencyjną lub skończoną (maszyna cyfrowa, maszyna z pamięcią). W urządzeniach sekwencyjnych koniecznie są elementy pamięci. Stan tych pozycji zależy od historii sygnałów wejściowych. Sygnały wyjściowe urządzeń szeregowych są określane nie tylko przez sygnały dostępne na wejściach do ten moment czas, ale także stan elementów pamięci. Tak więc odpowiedź urządzenia szeregowego na określone sygnały wejściowe zależy od historii jego działania.

Wśród urządzeń zarówno kombinowanych, jak i sekwencyjnych, są typowe, najczęściej stosowane w praktyce.

Szyfratory

Enkoder to urządzenie kombinowane, które przekształca liczby dziesiętne na system liczb binarnych, a każdemu wejściu można przypisać liczbę dziesiętną, a zestaw wyjściowych sygnałów logicznych odpowiada określonemu kodowi binarnemu. Koder jest czasami nazywany „koderem” i jest używany na przykład do konwersji liczb dziesiętnych wpisanych na klawiaturze klawiatury na liczby binarne.

Jeżeli liczba wejść jest tak duża, że w enkoderze wykorzystywane są wszystkie możliwe kombinacje sygnałów wyjściowych, to taki enkoder nazywamy kompletnym, jeśli nie wszystkimi, to niekompletnym. Liczba wejść i wyjść w kompletnym enkoderze jest powiązana stosunkiem n = 2 m, gdzie n to liczba wejść, m to liczba wyjść.

Czyli, aby zamienić kod manipulatora na czterocyfrową liczbę binarną, wystarczy użyć tylko 10 wejść, a łączna liczba możliwych wejść wyniesie 16 (n = 2 4 = 16), czyli koder 10×4 ( od 10 do 4) będzie niekompletny...

Rozważmy przykład konstrukcji kodera do konwersji dziesięciocyfrowego kodu jednostki (liczby dziesiętne od 0 do 9) na kod binarny. W tym przypadku zakłada się, że sygnał odpowiadający jednostce logicznej jest podawany tylko na jedno wejście na raz. Konwencjonalne oznaczenie takiego enkodera i tabelę korespondencji kodów pokazano na ryc. 3.35.

Za pomocą ten stół korespondencja, piszemy wyrażenia logiczne, w tym w sumie logicznej te zmienne wejściowe, które odpowiadają jednostce jakiejś zmiennej wyjściowej. Tak więc na wyjściu 1 będzie logiczna „1”, gdy logiczna „1” będzie znajdować się na wejściu X 1 lub X 3, lub X 5, lub X 7, lub X 9, czyli 1 = X 1 + X 3 + X 5 + X 7 + X 9

Podobnie otrzymujemy y 2 = X 2 + X 3 + X 6 + X 7 y 3 = X 4 + X 5 + X 6 + X 7 y 4 = X 8 + X 9

Zaprezentujmy na ryc. 3.36 schemat takiego enkodera z wykorzystaniem elementów OR.  W praktyce często używany jest koder priorytetowy. W takich enkoderach binarny kod liczbowy odpowiada najwyższemu numerowi wejścia, do którego podawany jest sygnał „1”, czyli dozwolone jest wysyłanie sygnałów do kilku wejść do enkodera priorytetowego i ustawia kod numer odpowiadający nadrzędnemu wejściu na wyjściu.

W praktyce często używany jest koder priorytetowy. W takich enkoderach binarny kod liczbowy odpowiada najwyższemu numerowi wejścia, do którego podawany jest sygnał „1”, czyli dozwolone jest wysyłanie sygnałów do kilku wejść do enkodera priorytetowego i ustawia kod numer odpowiadający nadrzędnemu wejściu na wyjściu.

Rozważmy jako przykład (ryc. 3.37) enkoder priorytetowy (enkoder priorytetowy) K555IVZ z serii mikroukładów K555 (TTLSh).

Enkoder posiada 9 wejść odwróconych, oznaczonych PR l,…, PR 9. PR oznacza priorytet. Enkoder ma cztery wyjścia odwrotne B l, ..., B 8. Skrót B oznacza „bus” (z angielskiego. Bus). Cyfry określają wartość aktywnego poziomu (zero) w odpowiednim bicie liczby binarnej. Na przykład B 8 oznacza, że zero na tym wyjściu odpowiada liczbie 8. Oczywiście jest to niekompletny enkoder.

Jeżeli na wszystkich wejściach - jednostka logiczna, to na wszystkich wyjściach również jednostka logiczna, której odpowiada liczba 0 w tzw. kodzie odwrotnym (1111). Jeżeli co najmniej jedno wejście ma logiczne zero, to stan sygnałów wyjściowych jest określony przez największą liczbę wejść, która ma logiczne zero i nie zależy od sygnałów na wejściach o mniejszej liczbie.

Np. jeśli wejście PR 1 jest zerem logicznym, a wszystkie inne wejścia są logiczne, to na wyjściach są następujące sygnały: B 1 - 0, B 2 - 1, B 4 - 1, B 8 - 1, co odpowiada cyfrze 1 w odwrotnym kodzie (1110).

Jeżeli wejście PR 9 jest zerem logicznym, to niezależnie od innych sygnałów wejściowych na wyjściach znajdują się następujące sygnały: V 1 - 0, V 2 - 1, V 4 - 1, V 8 - 0, co odpowiada liczbie 9 w odwrotnym kodzie (0110) ...

Głównym celem enkodera jest przekształcenie numeru źródła sygnału na kod (na przykład numer wciśniętego przycisku jakiejś klawiatury).

Dekodery

Urządzenie kombinowane nazywa się, przekształcając n-bitowy kod binarny na sygnał logiczny, który pojawia się na wyjściu, którego liczba dziesiętna odpowiada kodowi binarnemu. Liczba wejść i wyjść w tzw. pełnym dekoderze jest powiązana stosunkiem m = 2 n, gdzie n to liczba wejść, a m to liczba wyjść. Jeżeli w operacji dekodera używana jest niepełna liczba wyjść, to taki dekoder nazywamy niekompletnym. Czyli na przykład dekoder z 4 wejściami i 16 wyjściami byłby kompletny, a gdyby było tylko 10 wyjść, byłby niekompletny.

Spójrzmy na przykład na dekoder K555ID6 z serii K555 (ryc. 3.38).

Dekoder posiada 4 wejścia bezpośrednie, oznaczone jako А 1, ..., А 8. Skrót A oznacza „adres” (od angielskiego adresu). Wejścia te nazywane są adresowalnymi. Liczby określają wartości aktywnego poziomu (jednostki) w odpowiednim bicie liczby binarnej. Dekoder posiada 10 odwróconych wyjść Y 0, ..., Y 9. Cyfry określają liczbę dziesiętną odpowiadającą podanej liczbie binarnej na wejściach. Oczywiście ten dekoder jest niekompletny.

Wartość poziomu aktywnego (zero) ma wyjście, którego liczba jest równa liczbie dziesiętnej, określonej przez liczbę binarną na wejściu. Na przykład, jeśli wszystkie wejścia mają logiczne zera, to wyjście Y 0 jest zerem logicznym, a na pozostałych wyjściach jest logiczne jedyne. Jeżeli wejście A2 jest logicznym jedynką, a pozostałe wejścia są logicznym zerem, to wyjście Y2 jest logicznym zerem, a pozostałe wyjścia są logicznym zerem. Jeżeli wejście jest liczbą binarną większą niż 9 (na przykład wszystkie wejścia są jedynką, co odpowiada binarnemu 1111 i dziesiętnemu 15), to wszystkie wyjścia są logiczne.

Dekoder jest jednym z najczęściej używanych urządzeń logicznych. Służy do budowy różnych urządzeń kombinowanych.

Rozważane skramblery i dekodery to przykłady najprostszych konwerterów kodu.

Konwertery kodu

Na ogół nazywają urządzenia przeznaczone do konwersji jednego kodu na drugi i często wykonują niestandardowe konwersje kodu. Konwertery kodu są oznaczone X / Y.

Rozważmy cechy implementacji konwertera na przykładzie trzyelementowego konwertera kodu na kod pięcioelementowy. Załóżmy, że konieczne jest zaimplementowanie tabeli korespondencji kodów pokazanej na ryc. 3.39.

Tutaj N oznacza liczbę dziesiętną odpowiadającą wejściowemu kodowi binarnemu. Konwertery kodu często tworzą schemat dekoder-szyfrujący. Dekoder konwertuje kod wejściowy na pewną liczbę dziesiętną, a następnie dekoder tworzy kod wyjściowy. Schemat konwertera, utworzony zgodnie z tą zasadą, pokazano na ryc. 3.40, gdzie stosowany jest koder matrycowy diody. Zasada działania takiego konwertera jest dość prosta. Np. gdy na wszystkich wejściach dekodera występuje logiczne „O”, to na jego wyjściu 0 pojawia się logiczna „1”, co prowadzi do pojawienia się „1” na wyjściach 4 i 5, czyli zaimplementowany jest pierwszy wiersz tabeli korespondencji kodów.

Przemysł produkuje duża ilość scramblerów, dekoderów oraz konwertery kodu, takie jak dekoder bramkowany 4×16 (K555IDZ), konwerter kodu do sterowania matrycą LED 7×5 (K155ID8), konwerter kodu do sterowania wskaźnikiem słupkowym (K155ID15) itp.

Jednym z bardzo ważnych elementów techniki cyfrowej, a zwłaszcza w komputerach i systemach sterowania, są enkodery i dekodery.

Kiedy słyszymy słowo scrambler lub dekoder, przychodzą na myśl frazy z filmów szpiegowskich. Coś w rodzaju: odszyfruj przesyłkę i zaszyfruj odpowiedź.

Nie ma w tym nic złego, ponieważ szyfratory i deszyfratory są używane w maszynach szyfrujących w naszych i zagranicznych rezydencjach.

Mieszarki.

Tak więc koder (enkoder) jest urządzenie elektroniczne, w tym przypadku mikroukład, który konwertuje kod jednego systemu liczbowego na kod innego systemu. Najbardziej rozpowszechnione w elektronice są szyfratory, które przekształcają pozycyjny kod dziesiętny na równoległy kod binarny. W ten sposób enkoder można wskazać na schemacie ideowym.

Na przykład wyobraźmy sobie, że trzymamy w rękach zwykły kalkulator, z którego korzysta teraz każdy uczeń.

Ponieważ wszystkie czynności w kalkulatorze wykonywane są na liczbach binarnych (przypomnijmy sobie podstawy elektroniki cyfrowej), za klawiaturą znajduje się enkoder, który zamienia wprowadzone liczby na postać binarną.

Wszystkie przyciski kalkulatora są podłączone do wspólnego przewodu i naciskając np. przycisk 5 na wejściu enkodera, natychmiast otrzymamy binarną postać tej liczby na jego wyjściu.

Oczywiście enkoder przelicznika ma większą ilość wejść, gdyż oprócz liczb trzeba w nim wprowadzić jeszcze jakieś inne symbole arytmetyczne, dlatego z wyjść enkodera usuwane są nie tylko liczby w postaci binarnej, ale także polecenia.

Jeśli weźmiemy pod uwagę wewnętrzną strukturę enkodera, łatwo jest upewnić się, że jest on wykonywany na najprostszych podstawowych elementach logicznych.

We wszystkich urządzeniach sterujących, które działają na logice binarnej, ale dla wygody operatora mają klawiaturę dziesiętną, stosowane są enkodery.

Dekodery.

Dekodery należą do tej samej grupy, ale działają dokładnie odwrotnie. Konwertują równoległy kod binarny na pozycyjny dziesiętny. Konwencjonalne oznaczenie graficzne na schemacie może wyglądać następująco.

Albo tak.

Jeśli mówimy pełniej o dekoderach, należy powiedzieć, że potrafią konwertować kod binarny na różne systemy liczbowe (dziesiętny, szesnastkowy itp.). Wszystko zależy od konkretnego celu i przeznaczenia mikroukładu.

Najprostszy przykład... Wielokrotnie widziałeś cyfrowy siedmiosegmentowy wskaźnik, na przykład diodę LED. Wyświetla cyfry dziesiętne i liczby, do których jesteśmy przyzwyczajeni od dzieciństwa (1, 2, 3, 4…). Ale, jak wiecie, elektronika cyfrowa działa z liczbami binarnymi, które reprezentują kombinację 0 i 1. Co przekształciło kod binarny na dziesiętny i dało wynik na cyfrowym siedmiosegmentowym wyświetlaczu? Pewnie już się domyślałeś, że zrobił to dekoder.

Działanie dekodera można ocenić na żywo, jeśli złożysz prosty obwód, który składa się z mikroukładu dekodera K176ID2 oraz siedmiosegmentowy wskaźnik LED, zwany również „ósemką”. Spójrz na schemat, łatwiej zrozumieć, jak działa dekoder. Do szybkiego montażu obwodów można użyć płytki stykowej bez lutowania.

Na przykład. Mikroukład K176ID2 został opracowany do sterowania 7-segmentowym wskaźnikiem LED. Ten mikroukład jest w stanie konwertować kod binarny z 0000 przed 1001 , co odpowiada cyfrom dziesiętnym od 0 do 9 (jedna dekada). Pozostałe, starsze kombinacje po prostu nie są wyświetlane. Wnioski C, S, K mają charakter pomocniczy.

Mikroukład K176ID2 ma cztery wejścia (1, 2, 4, 8). Są też czasami oznaczane D0 - D3... Do tych wejść stosowany jest równoległy kod binarny (na przykład 0001). W tym przypadku kod binarny ma 4 bity. Mikroukład konwertuje kod tak, aby na wyjściach ( a - g), pojawiają się sygnały tworzące cyfry dziesiętne i liczby na siedmiosegmentowym wskaźniku, do którego jesteśmy przyzwyczajeni. Ponieważ dekoder K176ID2 może wyświetlać cyfry dziesiętne w zakresie od 0 do 9, na wskaźniku zobaczymy tylko je.

Do wejść dekodera K176ID2 podłączone są 4 przełączniki dwustabilne (S1 - S4), za pomocą których do dekodera można podać równoległy kod binarny. Na przykład podczas zamykania przełącznika dwustabilnego S1 jednostka logiczna jest dostarczana do piątego pinu mikroukładu. Jeśli otworzysz styki przełącznika dwustabilnego S1- będzie to odpowiadać logicznemu zerowi. Za pomocą przełączników dwustabilnych możemy ręcznie ustawić logikę 1 lub 0 na wejściach mikroukładu.Myślę, że z tym wszystko jest jasne.

Schemat pokazuje, w jaki sposób kod 0101 jest podawany na wejścia dekodera DD1. Wskaźnik ledowy wyświetli się cyfra 5. Jeśli zamkniesz tylko przełącznik S4, wskaźnik wyświetli cyfrę 8. Aby wpisać liczbę od 0 do 9 w kod binarny wystarczą cztery cyfry: a 3 * 8 + a 2 * 4 + a 1 * 2 + a 0 * 1, gdzie 0 - 3, to liczby z systemu liczbowego (0 lub 1).

Zaprezentujmy liczbę 0101 w postaci dziesiętnej 0101 = 0*8 + 1*4 + 0*2 + 1*1 = 4 + 1 = 5 ... Spójrzmy teraz na diagram i zobaczmy, że waga cyfry odpowiada cyfrze, przez którą we wzorze pomnożono 0 lub 1.

Dekoder oparty na technologii TTL - K155ID1 był kiedyś używany do sterowania cyfrowym wskaźnikiem wyładowania gazu typu IN8, IN12, który był bardzo poszukiwany w latach 70-tych, ponieważ niskonapięciowe wskaźniki LED były nadal bardzo rzadkie.

Wszystko zmieniło się w latach 80-tych. Można było swobodnie nabyć siedmiosegmentowe matryce LED (wskaźniki) oraz boom w montażu zegarów elektronicznych ogarnął radioamatorów. Domowej roboty Zegarek cyfrowy tylko leniwi nie zbierali dla domu.