L'architettura della famiglia MCS-51 è in gran parte predeterminata dal suo scopo: la costruzione compatto e a buon mercato dispositivi digitali... Tutte le funzioni di un microcomputer sono implementate utilizzando un singolo microcircuito. La famiglia MCS-51 comprende una gamma di microcircuiti dai microcontrollori più semplici a quelli più complessi. I microcontrollori della famiglia MCS-51 consentono di eseguire sia attività di controllo per vari dispositivi, sia di implementare singoli nodi di un circuito analogico. Tutti i microcircuiti di questa famiglia funzionano allo stesso modo sistema di comando MCS-51, la maggior parte di essi viene eseguita negli stessi casi con piedinatura corrispondente(numerazione delle gambe per il corpo). Ciò consente di utilizzare microcircuiti di diverse aziende per il dispositivo sviluppato: Maxim, Atmel, NXP, ecc. (pagina catalogo..php? = elenco_componenti & id = 39 "> vedi ricerca per parametri) senza alterazione diagramma schematico dispositivi e programmi.

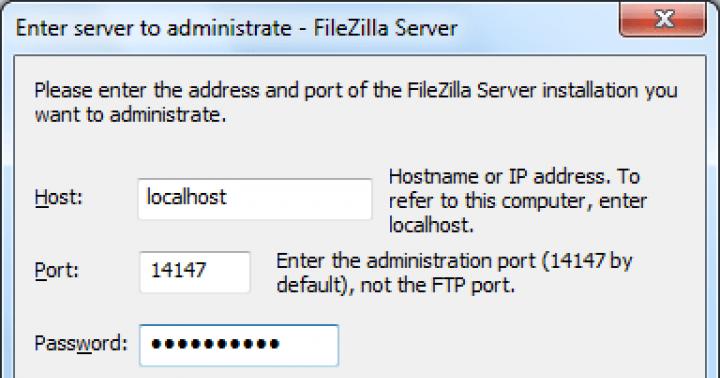

Immagine 1. Schema strutturale controller I8751

Lo schema a blocchi del controllore è mostrato in Figura 1. ed è composto dalle seguenti unità funzionali principali: unità di controllo, dispositivo logico aritmetico, unità temporizzatore/contatore, unità di interfaccia seriale e di interrupt, contatore di programma, memoria dati e memoria di programma. Lo scambio bidirezionale viene effettuato utilizzando un'autostrada dati interna a 8 bit.

Diamo un'occhiata più da vicino allo scopo di ogni blocco. Quasi tutti i rappresentanti della famiglia MCS-51 sono costruiti secondo questo schema.... Vari microcircuiti di questa famiglia differiscono solo nei registri per scopi speciali (compreso il numero di porte). Set di comandi per tutti i controller della famiglia MCS-51 contiene 111 comandi di base con un formato di 1, 2 o 3 byte e non cambia quando si passa da un microcircuito all'altro. Ciò garantisce un'eccellente portabilità dei programmi da un microcircuito all'altro.

Unità di controllo e sincronizzazione

L'unità di temporizzazione e controllo è progettata per generare segnali di temporizzazione e controllo per garantire il coordinamento lavorare insieme Unità OEVM in tutte le modalità di funzionamento consentite L'unità di controllo comprende:

- - un dispositivo per la formazione di intervalli di tempo,

- - Logica I/O,

- - registro dei comandi,

- - registro di controllo del consumo di energia elettrica,

- - decodificatore di comando, logica di controllo del computer.

Dispositivo di sagomatura della fascia orariaè destinato alla formazione e all'emissione di segnali di sincronizzazione interni di fasi, orologi e cicli. Il numero di cicli macchina determina la durata dell'esecuzione dell'istruzione. Quasi tutti i comandi OEVM vengono eseguiti in uno o due cicli macchina, ad eccezione dei comandi di moltiplicazione e divisione, la cui durata è di quattro cicli macchina. Designiamo la frequenza dell'oscillatore principale con F g. Quindi la durata del ciclo della macchina è 12 / F g o 12 periodi del segnale dell'oscillatore principale. La logica input-output è progettata per ricevere ed emettere segnali che forniscono lo scambio di informazioni con dispositivi esterni attraverso le porte input/output P0-P3.

Registro di comandoè destinato alla registrazione e alla memorizzazione del codice operativo a 8 bit del comando in esecuzione. Il codice operativo, con l'ausilio di un decodificatore di comandi e di una logica di controllo del computer, viene convertito in un microprogramma per l'esecuzione dei comandi.

Registro di controllo dei consumi (PCON) consente di arrestare il microcontrollore per ridurre il consumo energetico e ridurre il livello di rumore del microcontrollore. Un'ulteriore riduzione del consumo di energia e riduzione del rumore può essere ottenuta arrestando l'oscillatore principale del microcontrollore. Ciò può essere ottenuto sfogliando un po' il registro di controllo del consumo PCON. Per n-MOS (serie 1816 o microcircuiti estranei senza "c" al centro), il registro di controllo del consumo PCON contiene un solo bit che controlla la velocità di trasmissione della porta seriale SMOD e non ci sono bit di controllo dell'alimentazione.

Unità logica aritmetica (ALU)è un dispositivo parallelo a otto bit che esegue operazioni aritmetiche e logiche. L'ALU è composta da:

- - registri accumulatori, holding register TMP1 e TMP2,

- - costanti ROM,

- - sommatore,

- - registro aggiuntivo (registro B),

- - batteria (ACC),

- - registro dello stato del programma (PSW).

Registrati batteria e registri di detenzione- registri a otto bit destinati a ricevere e memorizzare operandi per la durata delle operazioni su di essi. Questi registri non sono accessibili a livello di codice.

costanti ROM fornisce la generazione di un codice di correzione per la rappresentazione dei dati binari-decimali, un codice maschera per le operazioni a bit e un codice costante.

Sommatore parallelo a otto bit rappresenta circuito combinatorio con trasferimento sequenziale, progettato per eseguire operazioni aritmetiche di addizione, sottrazione e operazioni logiche di addizione, moltiplicazione, disuguale e identica.

Registro B- un registro a otto bit utilizzato durante le operazioni di moltiplicazione e divisione. Per altre istruzioni, può essere visto come un ulteriore registro super-operativo.

Batteria- un registro a otto bit atto a ricevere e memorizzare il risultato ottenuto durante l'esecuzione di operazioni aritmetico-logiche o operazioni di spostamento

Interfaccia seriale e unità di interruzione (PIP)è destinato all'organizzazione dell'input-output di flussi sequenziali di informazioni e all'organizzazione di un sistema di interruzione dei programmi. Il blocco comprende:

- - Buffer PIP,

- - logica di controllo,

- - registro di controllo,

- - buffer del trasmettitore,

- - buffer del ricevitore,

- - ricetrasmettitore per porta seriale,

- - registro di priorità di interruzione,

- - registro di abilitazione interruzione,

- - logica per l'elaborazione dei flag di interruzione e un circuito di generazione del vettore.

Contatore di programma progettato per formare l'attuale indirizzo a 16 bit della memoria interna del programma e l'indirizzo a 8/16 bit memoria esterna programmi. Il contatore di istruzioni include un buffer PC a 16 bit, un registro PC e un circuito di incremento (aumentando il contenuto di 1).

Memoria dati (RAM)è destinato alla memorizzazione temporanea delle informazioni utilizzate nel processo di esecuzione del programma.

Porte P0, P1, P2, P3 sono porte input-output quasi bidirezionali e sono progettate per garantire lo scambio di informazioni tra il computer e dispositivi esterni, formando 32 linee input-output.

Dispositivo timer V modelli base La famiglia dispone di due temporizzatori/contatori programmabili a 16 bit (T/C0 e T/C1), utilizzabili sia come temporizzatori che come contatori eventi esterni

Registro dello stato del programma (PSW) destinato a memorizzare informazioni sullo stato dell'ALU durante l'esecuzione del programma.

Memoria di programma (EPROM)è destinato alla memorizzazione di programmi ed è una memoria di sola lettura (ROM). Diversi microcircuiti utilizzano ROM maschera, cancellabili da radiazioni ultraviolette o VELOCE ROM.

Registro puntatore dati (DPTR)è progettato per memorizzare un indirizzo a 16 bit di memoria dati esterna o memoria di programma.

Puntatore stack (SP)è un registro a otto bit progettato per organizzare un'area speciale di memoria dati (stack), in cui è possibile memorizzare temporaneamente qualsiasi cella di memoria.

Versione base MCS-51 Brevi informazioni. I moderni microcontrollori (MC) a 8 bit possiedono tali risorse di controllo in tempo reale, che in precedenza erano ottenute utilizzando costosi layout multichip sotto forma di schede separate per microcomputer, vale a dire:

● avere una capacità di memoria sufficiente, la sua suddivisione fisica e logica in memoria di programma e memoria di dati (architettura Harvard) e un sistema di comando focalizzato sull'esecuzione di algoritmi di controllo;

● include tutti i dispositivi (processore, ROM, RAM, porte I/O, sistema di interrupt, funzionalità di elaborazione delle informazioni di bit, ecc.) necessari per implementare un sistema di controllo a microprocessore di configurazione minima. Negli anni '70 del secolo scorso, l'azienda Intel ha sviluppato e padroneggiato la produzione industriale della famiglia di microcontrollori MCS-48 a 8 bit, uniti da una serie di caratteristiche comuni (profondità di bit, sistema di comando, un insieme di blocchi funzionali di base, ecc.). La versione base di questa famiglia comprende:

● Processore a 8 bit;

● memoria interna del programma (1/2/4K byte);

● memoria dati interna (64/128/256 byte);

● fino a 27 linee I/O interne e 16 linee esterne;

● un contatempo a 8 bit;

● sistema di interrupt a livello singolo con due fonti di richiesta. Nel 1980, la stessa azienda ha sviluppato una nuova famiglia di microcontrollori MCS-51 a otto bit, che è compatibile con l'architettura della famiglia MCS-48, ma ha più capacità.

L'architettura della famiglia MCS-51 si è rivelata un tale successo che è ancora uno degli standard per gli MCU a 8 bit. Pertanto, come oggetto di studio sono stati scelti MC di questa famiglia, che si sono diffusi in sistemi di controllo relativamente semplici.

Per la famiglia MCS-51 sono stati sviluppati vari strumenti di preparazione del programma (compilatori, emulatori hardware-software, ecc.) ed esiste un gran numero di librerie di subroutine standard. La famiglia comprende varie modifiche di microcircuiti (versioni in cristallo) di microcontrollori. Negli articoli di questa sezione viene considerata in modo sufficientemente dettagliato la versione base dei microcontrollori della famiglia MCS-51 (il microcircuito 8051 corrisponde all'analogo domestico di KP1816BE51), che è il più semplice in termini di struttura e funzione e dal punto di vista della comprensione.

Le successive serie di microcircuiti, pur mantenendo la compatibilità con la versione base, differiscono da essa per tecnologia di produzione migliorata, parametri elettrici, hardware aggiuntivo e funzionalità. I seguenti articoli sono dedicati alle caratteristiche strutturali e funzionali delle successive modifiche dei microcircuiti della famiglia MCS-51.  Schema a blocchi generalizzato di MCS-51. La composizione del MC, il cui schema a blocchi generalizzato è mostrato in Fig. 7.1.1 include:

Schema a blocchi generalizzato di MCS-51. La composizione del MC, il cui schema a blocchi generalizzato è mostrato in Fig. 7.1.1 include:

● 8 bit processore CPU composta da ALU, dispositivi di controllo Uu e generatore di indirizzi F;

● mask ROM con capacità di 4K byte per la memorizzazione dei programmi;

● RAM con una capacità di 128 byte per la memorizzazione dei dati;

● quattro porte programmabili P0 – P3 per ingresso– uscita di informazioni;

● blocco dell'interfaccia seriale BPI per lo scambio di informazioni con dispositivi esterni tramite linea bifilare;

● blocco dei timer/contatori BT/C per il mantenimento della modalità real time;

● blocco di interrupt BP per l'organizzazione di interrupt di programmi eseguibili. Questi fondi si formano residente parte del microcontrollore posizionato direttamente sul chip. L'MC include un gran numero di registri assegnati a blocchi funzionali separati e non mostrati nel diagramma.

Il diagramma inoltre non mostra i circuiti di controllo. Lo scambio di informazioni bidirezionale tra i blocchi avviene tramite un 8 bit interno bus datiШД-8.

16 bit interni bus di indirizzi SHA-16, l'indirizzo formato nella CPU viene visualizzato nella ROM (12 bit dell'indirizzo) e nella RAM (8 bit meno significativi).

Quando si utilizza la memoria esterna, gli 8 bit meno significativi dell'indirizzo vengono inviati alla porta P0 e 3 o 8 bit più significativi alla porta P2.

Per l'estensione logica dell'interfaccia viene utilizzata una combinazione delle funzioni delle port line. A titolo di esempio, la Fig. 7.1.1 la linea tratteggiata mostra le linee della porta P3, in esecuzione alternativa funzioni per la trasmissione di segnali di controllo, il cui scopo sarà discusso di seguito. Per creare un generatore di clock interno, un risonatore al quarzo e due condensatori sono collegati ai terminali del microcircuito MK (Fig. 7.1.1). Invece di un clock interno, per la sincronizzazione è possibile utilizzare un oscillatore esterno. La designazione grafica convenzionale del microcircuito MK è mostrata in Fig. 2, designazione e scopo delle conclusioni - in tabella. 7.1.1. Considera i blocchi funzionali di MK e il principio del loro funzionamento.  Unità aritmetico-logica. L'unità aritmetico-logica è progettata per eseguire operazioni aritmetiche (incluse moltiplicazione e divisione) e logiche su operandi a otto bit, nonché operazioni di spostamento logico, azzeramento, impostazione, ecc. Lo schema a blocchi dell'ALU è mostrato in Fig. 7.1.3.

Unità aritmetico-logica. L'unità aritmetico-logica è progettata per eseguire operazioni aritmetiche (incluse moltiplicazione e divisione) e logiche su operandi a otto bit, nonché operazioni di spostamento logico, azzeramento, impostazione, ecc. Lo schema a blocchi dell'ALU è mostrato in Fig. 7.1.3.

L'ALU include

● otto bit paralleli sommatore SM di tipo combinatorio con trasferimento sequenziale, che esegue operazioni aritmetiche (addizioni e sottrazioni) e logiche (addizioni, moltiplicazioni, disuguali e identiche);

● batteria A, fornire le funzioni del registro aritmetico principale;

● Registrati B, utilizzato per realizzare operazioni di moltiplicazione e divisione o come ulteriore registro superoperativo, le cui funzioni sono definite dall'utente;

● registri(non disponibile a livello di codice) deposito temporaneoРВХ1, РВХ2, destinati a ricevere e memorizzare operandi per la durata dell'operazione;

● ROM costanti ROMK, che memorizza un codice di correzione per la rappresentazione dei dati binari e decimali, un codice maschera per le operazioni di bit e un codice costante;

● registro delle parole di stato del programma PSW, che corregge lo stato dell'ALU dopo l'operazione eseguita. Tavolo 7.1.2 fornisce informazioni sull'assegnazione dei bit dei singoli bit del registro PSW. Dispositivo di controllo. Unità di controllo (CU) del processore centrale previsto per coordinare il lavoro congiunto di tutti i nodi MK utilizzando gli impulsi di sincronizzazione generati e i segnali di controllo. Comprende (fig. 7.1.4):

● unità di sincronizzazione e controllo USU, che genera impulsi di sincronismo che impostano i cicli macchina e i loro singoli stati (S) e fasi (P) e, a seconda della modalità di funzionamento dell'MC, genera il necessario set di segnali di controllo. Per l'esecuzione di un comando vengono assegnati uno, due o quattro cicli macchina.

Ogni ciclo macchina ha sei stati S1 – S6, A include ogni stato due fasi P1, P2, la cui durata è il periodo di oscillazione del generatore di clock T 0SC.

La durata del ciclo macchina è 12T 0SC. Tutti i cicli macchina sono uguali, a partire dalla fase S1P1 e termina con la fase S6P2.

Oltre agli impulsi di sincronizzazione, il dispositivo di sincronizzazione in ogni ciclo macchina genera due (a volte uno) segnali strobe del byte basso dell'indirizzo ALE sotto forma di impulso positivo nelle fasi S1P2 – S2P1 e S4P2 – S5P1. Diagrammi temporali in Fig. 7.1.5 illustrare l'organizzazione dei cicli macchina;

● registro dei comandi RK, decodificatore di comando DC e PLM, consentendo in ogni ciclo macchina di formare un insieme di microoperazioni in accordo con il microprogramma del comando in esecuzione;

● logica I/O LVV per la ricezione e l'emissione di segnali che prevedono lo scambio di informazioni MC con dispositivi esterni attraverso le porte P0-P3;

● un registro PCON con un singolo bit SMOD abilitato nella posizione PCON.7 per raddoppiare la velocità di trasmissione della porta seriale. Il resto dei bit è riservato per un uso futuro.  Generatore di indirizzi. Generatore di indirizzi (FA) o contatore di comandi del PC, previsto per generare l'indirizzo della memoria di programma a 16 bit corrente e l'indirizzo della memoria dati esterna a 8/16 bit. Comprende (Fig. 7.1.6):

Generatore di indirizzi. Generatore di indirizzi (FA) o contatore di comandi del PC, previsto per generare l'indirizzo della memoria di programma a 16 bit corrente e l'indirizzo della memoria dati esterna a 8/16 bit. Comprende (Fig. 7.1.6):

● 16 bit respingente B, che comunica tra il bus dati a 8 bit dell'SM e il bus interno (ID) a 16 bit del generatore di indirizzi;

● Schema di incremento SI per aumentare di uno il valore dell'indirizzo di memoria di programma corrente;

● registro per la memorizzazione dell'indirizzo attuale dei comandi PTA provenienti dal SI;

● Registro puntatore dati DPTR , costituito da due registri a 8 bit DPH e DPL. Serve a memorizzare l'indirizzo a 16 bit della memoria dati esterna e può essere utilizzato come due RON indipendenti accessibili da software;

● registro dello shaper di indirizzi XPA per la memorizzazione dell'indirizzo esecutivo a 16 bit della memoria di programma o dell'indirizzo a 8/16 bit della memoria dati esterna. Questo registro viene utilizzato anche per trasferire i dati attraverso la porta P0 a dispositivi esterni durante l'esecuzione dei comandi MOVX @Rm, A e MOVX @DPRT, A.

Memoria dati. Memoria dati previsto per ricevere, memorizzare ed emettere informazioni utilizzate nel processo di esecuzione del programma. I dati della memoria interna (residente) (Fig. 7.1.7) sono costituiti da RAM con una capacità di 128 byte, puntatore della pila SP, registro degli indirizzi RAM RA e decodificatore Dsh.  Stack Pointer SP è un registro a 8 bit utilizzato per ricevere e memorizzare l'indirizzo della cella dello stack a cui è stato effettuato l'ultimo accesso. Dopo il reset, nello stack pointer viene impostato l'indirizzo 07H, che corrisponde all'inizio dello stack con indirizzo 08H. Il registro dell'indirizzo PA insieme al decoder Dsh permette di accedere alla cella di memoria richiesta contenente un byte o un bit di informazione.

Stack Pointer SP è un registro a 8 bit utilizzato per ricevere e memorizzare l'indirizzo della cella dello stack a cui è stato effettuato l'ultimo accesso. Dopo il reset, nello stack pointer viene impostato l'indirizzo 07H, che corrisponde all'inizio dello stack con indirizzo 08H. Il registro dell'indirizzo PA insieme al decoder Dsh permette di accedere alla cella di memoria richiesta contenente un byte o un bit di informazione.

L'MK offre la possibilità di aumentare la quantità di memoria dati fino a 64 KB tramite connessione dispositivi di archiviazione esterni. A titolo di esempio, la Fig. 7.1.8 mostra l'organizzazione del paging della memoria dati esterna dell'FPD con una capacità di 2K byte utilizzando istruzioni di tipo MOVX @

Rm (m = 0; 1). In questo caso la porta P0 funziona come un bus dati/indirizzo multiplex, tre linee della porta P2 servono per indirizzare una pagina della RAM esterna, e le restanti cinque linee possono essere usate come linee I/O.  Nella fig. 7.1.9 mostra i diagrammi di temporizzazione dei cicli di lettura e scrittura quando l'MK lavora con RAM esterna. I diagrammi indicano:

Nella fig. 7.1.9 mostra i diagrammi di temporizzazione dei cicli di lettura e scrittura quando l'MK lavora con RAM esterna. I diagrammi indicano:

● PCN - byte alto del contatore dei comandi del PC;

● DPL, DPH - byte bassi e alti del registro del puntatore di dati DPTR, utilizzato come registro per l'indirizzamento indiretto nelle istruzioni MOVX @ DPTR, A e MOVX A, @ DPTR;

● P2 SFR - Latch porta P2;

● Rm (m = 0, 1) - registri utilizzati nelle istruzioni MOVX @Rm, A e MOVX A, @Rm come registri di indirizzi indiretti;

● Z - stato ad alta resistenza;

● D - il periodo durante il quale i dati dalla porta P0 vengono inseriti nel microcontrollore.  Memoria di programma. La memoria del programma è destinata alla memorizzazione dei programmi, dispone di un proprio spazio di indirizzi (separato dalla memoria dati) ed è disponibile solo per la lettura. Include un decoder Dsh e ROM (Fig. 7.1.10).

Memoria di programma. La memoria del programma è destinata alla memorizzazione dei programmi, dispone di un proprio spazio di indirizzi (separato dalla memoria dati) ed è disponibile solo per la lettura. Include un decoder Dsh e ROM (Fig. 7.1.10).  Un contatore PC a 16 bit viene utilizzato per indirizzare la memoria del programma, quindi la sua capacità massima è di 64 K byte. La memoria interna del programma è costituita da una ROM da 4K byte e da un decoder a 12 bit. La memoria esterna è collegata secondo lo schema in Fig. 7.1.11.

Un contatore PC a 16 bit viene utilizzato per indirizzare la memoria del programma, quindi la sua capacità massima è di 64 K byte. La memoria interna del programma è costituita da una ROM da 4K byte e da un decoder a 12 bit. La memoria esterna è collegata secondo lo schema in Fig. 7.1.11.  Se si applica 0 V al pin ¯EA dell'MK (come mostrato in Fig. 7.1.11), la memoria interna del programma è disabilitata. Tutti gli accessi alla memoria iniziano all'indirizzo 0000h. Quando il pin ¯EA è collegato all'alimentazione, si accede automaticamente alla memoria di programma interna agli indirizzi 0000h – FFFFh e alla memoria di programma esterna agli indirizzi 0FFFh – FFFFh.

Se si applica 0 V al pin ¯EA dell'MK (come mostrato in Fig. 7.1.11), la memoria interna del programma è disabilitata. Tutti gli accessi alla memoria iniziano all'indirizzo 0000h. Quando il pin ¯EA è collegato all'alimentazione, si accede automaticamente alla memoria di programma interna agli indirizzi 0000h – FFFFh e alla memoria di programma esterna agli indirizzi 0FFFh – FFFFh.

Per leggere la memoria esterna dei programmi MK, viene generato il segnale ¯PSEN. Quando si lavora con la memoria interna, il segnale di lettura non viene utilizzato. Quando si accede alla memoria di programma esterna, viene sempre formato un indirizzo a 16 bit. Il byte meno significativo dell'indirizzo viene trasmesso attraverso la porta P0 nella prima metà del ciclo macchina e viene fissato al bordo dello strobe ALE nel registro Nella seconda metà del ciclo la porta P0 viene utilizzata per inserire un dato byte dalla memoria esterna nell'MC.

Il byte di ordine superiore dell'indirizzo viene trasmesso attraverso la porta P2 durante l'intero tempo di accesso alla memoria.

I diagrammi temporali dei cicli di lettura e scrittura quando l'MC funziona con RAM esterna sono mostrati in Fig. 7.1.12.  I diagrammi indicano:

I diagrammi indicano:

● PCL OUT - emissione del byte basso del contatore dei comandi del PC;

● РСН OUT - emissione del byte alto del contatore dei comandi del PC;

● DPH - byte alto del registro del puntatore dati DPTR, utilizzato come registro per l'indirizzamento indiretto nelle istruzioni MOVX @ DPTR, A e MOVX A, @ DPTR;

● P2 SFR - Latch porta P2;

● INS IN - immissione del byte di istruzione (comando) dalla memoria del programma;

● ADDR OUT - emissione del byte basso dell'indirizzo della memoria dati esterna dai registri Rm (m = 0, 1) o dal registro DPL (registro DPTR basso). Porte I/O. Assegnazione delle porte. Porte P0, P1, P2, P3 previsto per scambiare informazioni tra MK e dispositivi esterni, e anche per eseguire le seguenti funzioni:

● tramite la porta P0 viene emesso il byte meno significativo dell'indirizzo A7 ... A0; uscita dall'MK e input nel byte di dati MK quando si lavora con una memoria di programma esterna e una memoria di dati esterna (con divisione del tempo);

● il byte alto dell'indirizzo A15 ... A8 viene emesso attraverso la porta P2 quando si lavora con memoria di programma esterna e memoria dati esterna (solo quando si utilizzano i comandi MOVX A, @ DPTR e MOVX @ DPTR, A);

● Le linee della porta P3 possono essere utilizzate per eseguire funzioni alternative se nel latch-latch di questa linea è immesso 1, altrimenti sull'uscita di linea è fissato 0. Le funzioni alternative delle uscite della porta P3 sono riportate nella tabella. 7.1.3.

Caratteristiche dello schema delle porte

Nella fig. 7.1.13 mostra i diagrammi per un canale di ciascuna delle porte MK, tra cui:

● latch per il latch del bit di dati ricevuto;

● amplificatore di uscita cascata(autista);

● nodo legami con stadio di uscita (tranne P2);

● una catena per la trasmissione di un bit di dati dalla porta lato uscita, costituita dai buffer B2 e B3 (per la porta P4). Il latch è un D-flip-flop con clock da un segnale interno "Write to latch". Il bit di dati dall'uscita diretta del D-flip-flop può essere letto nel software attraverso il buffer B1 dal segnale "Read latch" alla linea del bus dati interno (SD) dell'MK.

Stadio di uscita la porta P0 è un inverter, le cui caratteristiche si manifestano nel fatto che il transistor di carico VT2 si apre solo quando si accede alla memoria esterna (durante il trasferimento di indirizzi e dati attraverso la porta). In tutte le altre modalità, il transistor di carico è chiuso. Pertanto, utilizzare P0 (Fig. 7.1.13, a) come porta di uscita scopo generale le resistenze di carico esterne devono essere collegate ai suoi terminali. Quando si scrive 1 sul latch della porta, il transistor dell'inverter VT1 è bloccato e l'uscita esterna della porta P0.X viene trasferita in uno stato ad alta resistenza. In questa modalità, il pin della porta P0.X può fungere da ingresso. Se la porta P0 viene utilizzata come porta I/O generica, ciascuno dei suoi pin P0.X può funzionare indipendentemente dagli altri come ingresso o uscita. Stadi di uscita porte P1, P2, P3 (Fig. 7.1.13, b, c, d) realizzato secondo circuiti inverter con un resistore di carico interno, che viene utilizzato come transistor VT2.

Per ridurre il tempo di commutazione durante il passaggio delle uscite della porta dallo stato 0 allo stato 1, in parallelo al transistor di carico VT2 viene introdotto un transistor aggiuntivo VT3. Il transistor VT3 con l'aiuto di elementi nel circuito di gate viene sbloccato per un tempo pari a due periodi di oscillazione dell'oscillatore a cristallo principale (durante le fasi S1P1, S2P2 del ciclo macchina). Stadi di uscita le porte P0, P2 (Fig. 7.1.13, A, c) utilizzando il multiplexer MX possono essere collegate sia ai latch che ai bus interni "Address / data" e "Address". Lo stadio di uscita della porta P1 (Fig. 7.1.13, 6) è collegato permanentemente al latch.

Se il pin della porta P3 è un'uscita e il suo latch contiene 1, il suo stadio di uscita è controllato dal segnale interno hardware "Funzione di uscita alternativa", che garantisce l'esecuzione della corrispondente funzione alternativa, ovvero uno dei segnali ¯WR, ¯RD o RxD viene generato sul pin esterno. Se il pin della porta viene utilizzato come ingresso, un segnale alternativo che arriva ad esso (TxD, ¯INT0, ¯INT1, T0, T1) viene trasmesso all'interno "Funzione di ingresso alternativo".

Modalità di scrittura della porta.

Quando viene eseguito il comando di scrittura sulla porta, il nuovo valore viene scritto nel latch nella fase S6P2 e viene inviato direttamente al pin di uscita della porta nella fase S1P1 del ciclo macchina successivo.

Modalità di lettura della porta

I comandi di lettura della porta leggono le informazioni direttamente da contatti esterni perni o fermi della porta. Nel primo caso, il bit di dati dall'uscita della porta viene letto programmaticamente attraverso il buffer B2 dal segnale "Leggi pin" alla linea del bus dati interno (SD) dell'MK. Si noti che i segnali "Write to latch", "Read latch", "Read pins" sono generati dall'hardware quando vengono eseguiti i comandi corrispondenti.

Nel secondo caso viene implementata la cosiddetta modalità "Leggi-Modifica-Scrivi", in cui il comando legge il segnale di stato del latch, lo modifica se necessario, quindi riscrive sul latch. La modalità "Leggi-Modifica-Scrivi" è implementata quando vengono eseguiti i seguenti comandi: ANL, ORL, XRL, JBC; CPL; INC; DIC; DJNC; MOV PX, Y; CLR PX.Y; SETB PX, Y.

La lettura delle informazioni dalle uscite dei latch elimina gli errori durante l'interpretazione del livello logico sul pin della porta. Leggi il seguito dell'articolo in.

Intel è l'antenato dell'architettura della famiglia MCS-51, che ha preso il nome dal primo rappresentante di questa famiglia: il microcontrollore 8051, rilasciato nel 1980 basato sulla tecnologia n-MOS. Una serie di dispositivi periferici di successo, una scelta flessibile di memoria di programma esterna o interna e un prezzo ragionevole hanno assicurato il successo di questo microcontrollore sul mercato. Dal punto di vista della tecnologia, il microcontrollore 8051 era un prodotto molto complesso per l'epoca: nel cristallo venivano utilizzati 128 mila transistor, che era 4 volte superiore al numero di transistor nel microprocessore 8086 a 16 bit. Questo microcontrollore rimane il nucleo della famiglia MCS-51 fino ad oggi.

Gli elementi principali dell'architettura di base della famiglia (architettura del microcontrollore 8051) sono:

ALU a 8 bit;

4 banche di registri, 8 ciascuna;

Memoria di programma interna (residente) 4 Kbytes, di tipo ROM o EPROM (8751);

Memoria dati interna (residente) 128 byte;

21 registro delle funzioni speciali;

Processore booleano;

Due timer/contatori a 16 bit;

Controller della porta seriale (UART);

Controller di interrupt con due livelli di priorità;

Quattro porte I/O a 8 bit, di cui due utilizzate come bus di indirizzi/dati per l'accesso a programmi esterni e memoria dati;

Generatore di clock integrato.

Quindi è stato rilasciato il microcontrollore 8052, che si distingueva per una maggiore quantità di programma residente e memoria di dati, introdotta da un terzo timer e, di conseguenza, un controller di interrupt ampliato.

Il successivo passo fondamentale nello sviluppo di MCS-51 è stato il trasferimento della tecnologia di produzione a CMOS (modifica 8xC51). Ciò ha permesso di implementare le modalità Idl (idle) e Power Down (ridotto consumo), che assicurano una forte diminuzione del consumo di energia del cristallo e hanno aperto la strada all'utilizzo del microcontrollore in applicazioni volatili, ad esempio in dispositivi autonomi alimentati a batteria.

E l'ultima fase importante nello sviluppo di MK 8051 da parte di Intel è stata il rilascio dei microcontrollori 8xC51FA / FB / FC e 8xC51RA / RB / RC, che in breve sono spesso indicati come 8xC51Fx e 8xC51Rx. Il principale caratteristica distintiva questo gruppo di cristalli è che hanno un timer/contatore (PCA) dedicato. Inoltre, i microcontrollori 8xC51Rx contengono anche un watchdog timer (WDT). Diamo un'occhiata più da vicino all'architettura e alla funzionalità del PCA.

L'APC include:

timer/contatore a 16 bit;

Cinque moduli di campionamento e confronto a 16 bit, ognuno dei quali è collegato ad una propria linea della porta I/O del microcontrollore.

Il timer/contatore serve tutti e cinque i moduli di campionamento e confronto, che possono essere programmati per eseguire una delle seguenti funzioni:

Campionamento a 16 bit del valore del timer sul fronte positivo del segnale esterno;

Campionamento a 16 bit del valore del timer sul fronte negativo del segnale esterno;

Campionamento a 16 bit del valore del timer su qualsiasi fronte del segnale esterno;

timer programmabile a 16 bit;

Dispositivo di uscita ad alta velocità a 16 bit;

PWM a 8 bit.

Tutte le funzioni di cui sopra vengono eseguite nella PCA a livello hardware e non caricano il processore centrale. Ciò consente di aumentare il throughput complessivo, migliorare l'accuratezza delle misurazioni e dell'elaborazione del segnale e ridurre il tempo di risposta del microcontrollore agli eventi esterni, il che è particolarmente importante per i sistemi in tempo reale. Il PCA implementato in 8xC51Fx (8xC51Rx) si è rivelato tale

|

Designazione |

Massimo frequenza (MHz) |

ROM/EPROM (byte) |

contatori | ||

È una fortuna che l'architettura di questi microcontrollori sia diventata uno standard industriale e che lo stesso PCA sia stato ripetutamente riprodotto in varie modifiche dell'MK 8051.

Alcune caratteristiche di un certo numero di microcontrollori MCS-51 prodotti da Intel sono mostrate nella Tabella 1.1.

I colli di bottiglia iniziali dell'architettura MCS-51 erano l'ALU a batteria a 8 bit e l'esecuzione dei comandi relativamente lenta (i comandi più veloci richiedono 12 pe-

Tabella 1.1

|

input Output |

ADC, ingressi x bit |

periferia, particolarità |

U pit. (V) |

||

|

Opzione bassa tensione | |||||

|

4 livelli IRQ, clock out | |||||

|

4 livelli IRQ, clock out | |||||

|

Versione bassa tensione 8xC51Fx | |||||

|

4 livelli IRQ, clock out | |||||

|

4 livelli IRQ, clock out | |||||

|

4 livelli IRQ, clock out | |||||

frequenza di clock del periodo (frequenza di clock MK)). Ciò ha limitato l'uso dei microcontrollori della famiglia in applicazioni che richiedono prestazioni superiori e calcoli complessi (16 e 32 bit). Una questione urgente era la modernizzazione fondamentale dell'architettura MCS-51. Il problema della modernizzazione è stato complicato dal fatto che all'inizio degli anni '90 erano già stati creati molti sviluppi nel campo del software e dell'hardware della famiglia MCS-51, in relazione ai quali uno dei principali compiti di progettazione nuova architetturaè stata l'implementazione della compatibilità hardware e software con gli sviluppi basati su MCS-51.

Per risolvere questo problema è stato creato un gruppo congiunto di specialisti di Intel e Philips, ma in seguito i percorsi di queste due società hanno preso strade separate. Di conseguenza, nel 1995 sono apparse due famiglie significativamente diverse: MCS-251/151 per Intel e MCS-51XA per Philips (vedi sottosezione 1.2).

Caratteristiche principali dell'architettura MCS-251:

Spazio di indirizzi lineare a 24 bit per indirizzare fino a 16 MB di memoria;

Un'architettura di registro che consente l'accesso ai registri come byte, parole e doppie parole;

Modalità di indirizzamento delle pagine per velocizzare il recupero delle istruzioni dalla memoria di programma esterna;

Coda di istruzioni;

Set di istruzioni esteso che include operazioni aritmetiche e logiche a 16 bit;

Spazio di indirizzi esteso dello stack (fino a 64 KB);

Fare di più comando rapido in 2 cicli di clock.

Il set di istruzioni MCS-251 contiene due set di istruzioni: il primo set è una copia del set di istruzioni MCS-51 e il secondo è costituito da istruzioni estese che sfruttano l'architettura MCS-251. Prima di utilizzare il microcontrollore, è necessario configurarlo, ad es. con l'aiuto del programmatore, "brucia" i bit di configurazione che determinano quale dei set di istruzioni diventerà attivo dopo l'accensione. Se installi la prima serie di istruzioni, in e questo caso La famiglia MCS-251 MCS sarà binaria compatibile con MCS-51. Questa modalità è chiamata modalità binaria. Se inizialmente si installa una serie di istruzioni estese (modalità sorgente), i programmi scritti per MCS-51 richiederanno la ricompilazione su cross-mean per MCS-251. La modalità sorgente consente di sfruttare al meglio l'architettura MCS-251 e ottenere le massime prestazioni.

Per gli utenti orientati all'utilizzo dei microcontrollori MCS-251 in sostituzione meccanica di MCS-51, Intel produce i microcontrollori MCS-151, già programmati nello stato Binary Mode.

Alcune caratteristiche di un certo numero di microcontrollori MCS-251/151 sono mostrate nella Tabella 1.1.

Attualmente, Intel, puntando al mercato dei processori Pentium, sta gradualmente eliminando la produzione di cristalli MCS-51. In generale, per un particolare sviluppatore, questo può passare inosservato, a meno che non utilizzi microcontrollori 8xC51GB e 80C152Jx, che non hanno la loro esatta controparte tra prodotti di altre aziende. Come per tutti gli altri microcontrollori della famiglia MCS-51, tutti sono stati replicati molte volte da altre aziende.

Attualmente, varie aziende producono molte modifiche e analoghi di questa famiglia, sia da parte di Intel che di altri produttori, la frequenza di clock e la capacità di memoria sono cresciute di dieci volte e continuano ad aumentare. Anche il set di moduli integrati nell'LSI viene integrato; un gran numero di modelli moderni è dotato di un ADC residente ad alta velocità, che ha fino a 12, e ora potrebbero esserci più cifre. Ma il cuore della famiglia MCS51 sono i BIS 8051, 80C51, 8751, 87C51, 8031, 80C31 di Intel, i cui primi campioni sono stati rilasciati nel 1980.

I microcontrollori della famiglia MCS51 sono realizzati secondo la tecnologia n-MOS di alta qualità (serie 8XXX, analogica - serie 1816 in Russia e Bielorussia) e la tecnologia k-MOS (serie 8ХСХХ, analogica - serie 1830). Il secondo carattere dopo l'8 significa: 0 - non c'è EPROM su chip, 7 - EPROM 4K con cancellazione ultravioletta. Il terzo simbolo: 3 - la ROM sarà cristallizzata, 5 - se non c'è EPROM, la maschera sarà sul chip.

E così 80S51 - LSI secondo tecnologia k-MOS con ROM mascherata su chip, 8031 - LSI n-MOS senza memoria di programma (ROM, EPROM) su chip, 8751 - LSI n-MOS con residente (posizionato su un chip) EPROM con cancellazione ultravioletta. Considereremo ulteriormente l'LSI 8751, facendo, se necessario, riserve sulle differenze in altri circuiti, fornendo quei parametri che sono stati pubblicati per il primo LSI seriale. Se necessario, puoi trovare ulteriori informazioni su tutte le modifiche moderne nei manuali aziendali e nella documentazione tecnica.

A. Caratteristiche generali e assegnazione dei pin

La famiglia MCS51 si basa su cinque modifiche di MK (con caratteristiche di base identiche), la principale differenza tra le quali è l'implementazione della memoria del programma e il consumo di energia (vedi Tabella 3.1). Il microcontrollore è a otto bit, ovvero dispone di comandi per l'elaborazione di parole a otto bit, ha un'architettura Harvard, la frequenza di clock dei campioni base della famiglia è di 12 MHz.

Tabella 3.1.

|

Microcircuiti |

Memoria interna del programma, byte |

Tipo di memoria di programma |

Memoria dati interna, byte |

Frequenza di clock, MHz |

Consumo di corrente, mA |

MK 8051 e 80C51 contengono una ROM programmabile con maschera della memoria di programma con una capacità di 4096 byte durante la produzione di un cristallo e sono progettati per l'uso nella produzione di massa. MK 8751 contiene una EPROM con una capacità di 4096 byte con cancellazione ultravioletta ed è conveniente nella fase di sviluppo del sistema durante il debug dei programmi, nonché durante la produzione in piccoli lotti o durante la creazione di sistemi che richiedono re-

adeguamento periodico.

MK 8031 e 80C31 non contengono memoria di programma integrata. Come le modifiche precedentemente descritte, possono utilizzare fino a 64 Kbyte di memoria di programma esterna e possono essere efficacemente utilizzati in sistemi che richiedono un volume molto maggiore (di 4 Kbyte su un chip) di memoria di programma.

Ogni MC della famiglia contiene una memoria dati residente con una capacità di 128 byte con la possibilità di espandere la quantità totale di dati RAM fino a 64 Kbyte tramite l'utilizzo di IC RAM esterna.

processore centrale a otto bit;

4 KB di memoria di programma (solo 8751 e 87C51);

memoria dati di 128 byte;

quattro porte I/O programmabili a otto bit;

due timer/contatori multimodali a 16 bit;

un sistema di interruzioni autovettoriali con cinque vettori e due livelli di priorità controllati da software;

un'interfaccia seriale comprendente un ricetrasmettitore duplex universale in grado di funzionare in quattro modalità;

generatore di orologio.

Il sistema di comando MK contiene 111 comandi di base con il formato 1, 2 o 3 byte. Il microcontrollore ha:

32 registri generici RON, organizzati in quattro banchi di otto registri ciascuno con i nomi R0 ... R7, la scelta dell'uno o dell'altro banco è determinata dal programma impostando i bit corrispondenti nel registro di stato del programma PSW;

128 flag controllati da software (processore di bit, vedi sotto);

un insieme di registri di funzioni speciali che controllano gli elementi MK. Esistono le seguenti modalità di funzionamento del microcontrollore:

uno). Ripristino generale. 2) Normale funzionamento. 3) Modalità a basso consumo e modalità inattiva. 4). Modalità di programmazione EPROM residente, se presente.

Qui ci concentreremo sulle prime due modalità di funzionamento, una descrizione dettagliata della composizione e del funzionamento dell'MC in tutte le modalità è fornita nell'Appendice A1.

RON e la zona del processore di bit si trovano nello spazio degli indirizzi della RAM residente con indirizzi da 0 a 80h.

Nella zona superiore degli indirizzi della memoria ad accesso casuale residente sono presenti i registri delle funzioni speciali (SFR, Special Function Registers). Il loro scopo è riportato nella tabella. 3.2.

Tabella 3.2.

|

Designazione |

Nome | |

|

Batteria | ||

|

Registro B | ||

|

Registro dello stato del programma | ||

|

Puntatore di pila | ||

|

Puntatore dati. 2 byte: | ||

|

Byte meno significativo | ||

|

Byte alto | ||

|

Registro di priorità di interruzione | ||

|

Registro di abilitazione interruzione | ||

|

Registro modalità timer/contatore | ||

|

Registro di controllo timer/contatore | ||

|

Timer/contatore 0. Byte alto | ||

|

Timer/contatore 0. Byte basso | ||

|

Timer/contatore 1. Byte alto | ||

|

Timer/contatore 1. Byte basso | ||

|

Controllo della porta seriale | ||

|

Buffer della porta seriale | ||

|

Gestione dei consumi |

* - registri, ammettendo bit a bit indirizzamento

Diamo una rapida occhiata alle funzioni dei registri SFR mostrate in Tabella 3.2.

Batteria ACC - registro della batteria. Comandi progettati per funzionare

tu con una batteria, usa il mnemonico "A", ad esempio, MOV UN, P2 ... Il mnemonico "ACC" viene utilizzato, ad esempio, per l'indirizzamento della batteria bit a bit. Quindi, il nome simbolico del quinto bit dell'accumulatore quando si utilizza l'assembler A5M51 sarà il seguente: ACC. 5. .

Registrati V ... Usato durante le operazioni di moltiplicazione e divisione. Per altre istruzioni, il registro B può essere considerato un ulteriore registro superoperativo.

Registrati fortune programmi PSW contiene informazioni sullo stato del programma e viene installato in parte automaticamente in base al risultato dell'operazione eseguita, in parte dall'utente. La designazione e lo scopo dei bit di registro sono riportati rispettivamente nelle tabelle 3.3 e 3.4.

Tabella 3.3.

|

Designazione |

Tabella 3.4.

|

Designazione |

Assegnazione dei bit |

Accesso al bit |

||||

|

Porta bandiera. Modifiche durante l'esecuzione di una serie di istruzioni aritmetiche e logiche. |

Hardware o software |

|||||

|

Bandiera di trasporto aggiuntiva. Hardware impostato / cancellato durante le istruzioni di addizione o sottrazione per indicare riporto o prestito nel bit 3 quando viene generato il nibble meno significativo del risultato (D0-D3). |

Hardware o software |

|||||

|

Flag 0. Flag definito dall'utente. |

Programmaticamente |

|||||

|

Programmaticamente |

||||||

|

Puntatore della banca del registro di lavoro |

Programmaticamente |

|||||

|

Banco 0 con indirizzi (00Н - 07Н) Banco 1 con indirizzi (08Н - 0FН) Banco 2 con indirizzi (10Н - 17Н) Banco 3 con indirizzi (18Н - 1FН) | ||||||

|

Bandiera di overflow. L'hardware viene impostato o cancellato durante l'esecuzione di istruzioni aritmetiche per indicare una condizione di overflow |

Hardware o software |

|||||

|

Ricambio. Contiene un trigger di lettura/scrittura che può essere utilizzato | ||||||

|

Bit di parità. Hardware cancellato o impostato in ogni ciclo di istruzione per indicare un numero pari o dispari di bit della batteria nello stato "1". |

Hardware o software |

|||||

Puntatore pila SP - Registro a 8 bit, il cui contenuto viene incrementato prima di scrivere i dati nello stack durante l'esecuzione dei comandi PUSH e CALL. Al ripristino iniziale, il puntatore dello stack è impostato su 07H e l'area dello stack nella RAM dati inizia alle 08H. Se necessario, ridefinendo il puntatore dello stack, l'area dello stack può essere posizionata ovunque nella RAM dati interna dei microcontrollori.

Puntatore dati DPTR è costituito da byte alto (DPH) e byte basso

(DPL). Contiene un indirizzo a 16 bit quando si accede alla memoria esterna. Può essere utilizzato

essere scritto come un registro a 16 bit o come due registri indipendenti a otto bit.

Porta0 - PortZ. I bit separati dei registri delle funzioni speciali P0, P1, P2, P3 sono bit - "latch" delle uscite delle porte P0, P1, P2, P3.

Respingente coerente porta SBUF è costituito da due registri separati: il buffer del trasmettitore e il buffer del ricevitore. Quando i dati vengono scritti su SBUF, entrano nel buffer del trasmettitore e la scrittura di un byte su SBUF avvia automaticamente la sua trasmissione sulla porta seriale. Quando i dati vengono letti da SBUF, vengono recuperati dal buffer del ricevitore.

Registri Timer. Registra le coppie (TH0, TL0) e (TH1, TL1) modulo 16-

registri di conteggio bit per bit rispettivamente per timer/contatore 0 e timer/contatore 1.

Registri gestione. I registri delle funzioni speciali IP, IE, TMOD, TCON, SCON e PCON contengono bit di comando e bit di stato del sistema di interrupt,

contatori/contatori e porta seriale. Saranno discussi in dettaglio di seguito.

RxD TxD INT0 INT1 T0 T1 WR

P1.2 P1.3 P1.4 P1.5 P1.6 P1.7

RST BQ2 BQ 1 EA

P3.0 P3.1 P3.2 P3.3 P3.4 P3.5 P3.6 P3.7

P2.0 P2.1 P2.2 P2.3 P2.4 P2.5 P2.6 P2.7

P0.0 P0.1 P0.2 P0.3 P0.4 P0.5 P0.6 P0.7

Durante il funzionamento, MK fornisce:

il tempo minimo per eseguire i comandi di addizione è 1 μs;

moltiplicazione e divisione hardware con un tempo minimo di esecuzione di 4 μs.

L'MK offre la possibilità di impostare la frequenza dell'oscillatore interno utilizzando un quarzo, una catena LC o un oscillatore esterno.

Il sistema di istruzioni esteso fornisce indirizzamento a byte e bit per bit, aritmetica binaria e binario-decimale, indicazione di overflow e parità pari/dispari e la possibilità di implementare un processore logico.

La caratteristica più importante e distintiva dell'architettura della famiglia MCS51 è che l'ALU può manipolare dati a bit singolo oltre ad eseguire operazioni su tipi di dati a 8 bit. I singoli bit accessibili tramite software possono essere impostati, cancellati o sostituiti con il loro complemento, possono essere inviati, controllati e

Figura 3.2. Conclusioni esterne

microcontrollore

utilizzato nel calcolo logico. Considerando che il supporto per tipi di dati semplici (se esiste

la tendenza all'aumento della lunghezza delle parole) può sembrare a prima vista un passo indietro, questa qualità rende i microcontrollori MCS51 particolarmente adatti per applicazioni che utilizzano controllori. Gli algoritmi di quest'ultimo, a loro modo, presuppongono la presenza di variabili booleane di ingresso e di uscita, difficilmente implementabili utilizzando i microprocessori standard. Tutte queste proprietà sono denominate collettivamente la famiglia di processori booleani MCS51. Questa potente ALU rende la famiglia di microcontrollori MCS51 un set di istruzioni ugualmente adatto per applicazioni di controllo in tempo reale e algoritmi ad alta intensità di dati.

Il diagramma schematico del microcontrollore è mostrato in Fig. 3.2. Nella versione base, è confezionato in un pacchetto DIP a 40 pin. Consideriamo lo scopo delle conclusioni.

Cominciamo con i pin di alimentazione «0 V" e "5 V" , per il quale riceve il cibo principale. La corrente di consumo è riportata nella tabella. 3.1.

Conclusione "RST" - reset del microcontrollore. Quando viene applicato un livello alto attivo a questo pin, modalità Comune dumping e MK esegue le seguenti azioni:

Imposta a zero il contatore dei comandi del PC e tutti i registri delle funzioni speciali, ad eccezione dei latch delle porte P0-P3, del puntatore dello stack SP e del registro SBUF;

il puntatore dello stack è impostato su 07H;

disabilita tutte le sorgenti di interrupt, contatori temporizzatori e seriali

seleziona BANK 0 RAM, prepara le porte P0-P3 per la ricezione dei dati e determina

separa i pin ALE e PME come ingressi per la sincronizzazione esterna;

nei registri di funzioni speciali PCON, IP e IE, i bit di riserva sono impostati a valori casuali e tutti gli altri bit sono impostati a zero;

il registro SBUF è impostato su valori casuali.

imposta i latch-latch delle porte P0-P3 su "1".

Gli stati dei registri del microcontrollore dopo il ripristino sono mostrati nella Tabella 3.5.

Tabella 3.5.

|

Informazione |

|

|

Indefinito |

|

|

0ХХХ0000В per k-MOS 0XXXXXXXB per n-MOS |

Il pin RST ha anche una funzione alternativa. Attraverso di essa viene fornita alimentazione di backup per mantenere inalterato il contenuto della RAM del microcontrollore quando viene rimossa quella principale.

conclusioni BQ1, BQ2 – progettato per collegare un risonatore al quarzo, che determina la frequenza di clock dell'MK.

Conclusione EA` (e esterno UN vestire – esterno l'indirizzo) - progettato per attivare la modalità di lettura dei codici di controllo dalla memoria di programma esterna, quando a questa uscita viene applicato un livello basso attivo. Il pin ha uno scopo alternativo (funzione). Viene fornito con la tensione di programmazione della EPROM in modalità programmazione.

Conclusione PME (P programma m emotività e abile – autorizzazione memoria programmi) - predisposto per controllare il ciclo di lettura dalla memoria del programma e viene attivato automaticamente dal MC in ogni ciclo macchina.

Conclusione Ale (UN vestire l lunghezza e abile – autorizzazione junior indirizzi) lampeggia l'uscita della parte inferiore dell'indirizzo sulla porta P0. L'uscita viene utilizzata anche durante la programmazione dell'EPROM, mentre ad essa viene fornito un impulso stroboscopico.

MK contiene quattro gruppi di porte: P0, P1, P2 e P3. Questi sono il resto dei 40 pin del microcontrollore. Queste porte possono servire per informazioni I/O bit per bit, ma a parte questo, ognuna di esse ha la propria specializzazione. Lo schema funzionale generalizzato della porta è mostrato in Fig. 3.3. La porta contiene gli interruttori FET di uscita collegati al pin, l'interruttore di funzione, il latch sul D-flip-flop e la logica di controllo. Il latch sul bus interno MK può essere scritto uno o zero. Queste informazioni passano attraverso l'interruttore di funzione ai tasti di output e al pin MK. Nello stato di uno, entrambi i transistor N e N1 sono spenti, ma N2 è acceso. Nello stato di zero, N si apre

Xia e N2 chiude. Nel momento in cui la porta svolge la funzione alternativa per la quale è specializzata, lo stato del pin viene rilasciato. Il microcontrollore può leggere separatamente lo stato del port latch e lo stato della sua uscita, impostati da un segnale esterno. Per questo nell'assembler MK ci sono comandi speciali che attivano le righe corrispondenti. Per leggere lo stato del pin, è necessario il fermo della porta corrispondente

essere preregistrato

Da interno

Controllo a scatto

Selettore di funzioni

Vcc

Fine settimana

unità. Quando viene attivata la linea "read latch" all'uscita della cella "AND" a cui questa linea è collegata, il

stanca MK D Q

Latch scrive C Q

Lettura del chiavistello

Perno della porta

lo stato del latch, che viene fornito al bus MC interno, quando attivato

"Leggi uscita" - lo stato dell'uscita esterna della porta.

Porta P0 - porta bidirezionale universale

input Output. Oltre questo porto

la funzione di organizzare bus di indirizzi esterni e

Riso. 3.3. Schema funzionale della porta del microcontrollore

dati per espandere la memoria del programma e la memoria dei dati

microcontrollore. Quando c'è un accesso alla memoria di programma esterna o viene eseguito un comando per accedere alla memoria dati esterna, la parte di ordine inferiore dell'indirizzo (A0 ... A7) viene impostata sui pin della porta, che è gated in alto sul pin ALE . Quindi, durante la scrittura nella memoria dati, le informazioni registrate dal bus interno dell'MK arrivano ai pin della porta P0. Nelle operazioni di lettura, invece, le informazioni dai pin della porta vanno al bus interno. Una caratteristica della porta P0 è l'assenza di un transistor "pull-up" N2, che fornisce alimentazione all'uscita. La scrittura sul latch della porta dell'unità lo mette semplicemente in uno stato di alta impedenza, necessario per il normale funzionamento del bus di dati. Se è necessario alimentare dispositivi esterni tramite l'uscita, è necessario fornire resistori esterni dai circuiti di alimentazione all'uscita della porta.

Porta Р1 - porta I/O bidirezionale universale senza funzioni alternative.

Porta P2 - una porta I/O bidirezionale universale, in alternativa alla funzione, che esegue l'emissione della parte senior dell'indirizzo (A8…A15) in caso di accesso alla memoria esterna.

Porta P3 - porta ingresso-uscita bidirezionale universale, ogni bit della quale prevede l'implementazione di diverse funzioni alternative. In questo caso, le funzioni alternative vengono implementate solo se vengono scritte sui latch dei pin della porta, altrimenti viene bloccata l'esecuzione delle funzioni alternative. Elenchiamoli separatamente per ogni bit:

P3.0 – RxD (R ead e X terna D ate, leggere dati esterni) - ingresso del ricetrasmettitore seriale integrato.

P3.1 – TxD (T sì e X terna D ate, trasmettere dati esterni) - uscita del ricetrasmettitore seriale integrato.

P3.2 – INT0` (INT errupt, interrupt) - ingresso di interrupt esterno 0.

P3.3 – INT1` - ingresso interrupt esterno 1.

P3.4 – C/T0 - immissione del temporizzatore/contatore incorporato zero.

P3.5 – C/T1 - inserimento del primo timer/contatore integrato.

P3.6 – WR` (w rite, write) - uscita di controllo del ciclo di scrittura nella memoria dati.

P3.7 – RD` (R ead, read) - uscita di controllo del ciclo di lettura dalla memoria dati.

I pin della porta P1, P2 e P3 sono in grado di erogare corrente di circa 0,2 mA in un'unità e di ricevere una corrente di 3 mA a zero, i pin della porta P0 sono più potenti e in grado di erogare una corrente di circa 0,8 mA per unità e ricevendo una corrente di 5 mA a zero. Brevi informazioni sullo scopo dei pin del microcontrollore sono fornite nella tabella 3.6.

Tabella 3.6.

|

Designazione |

Assegnazione dei pin | ||

|

Porta bidirezionale a 8 bit P1. Input di indirizzo A0-A7 durante il controllo della ROM interna (EPROM) |

entra esci |

||

|

Segnale di ripristino generale. Uscita dell'alimentazione della RAM di backup da una sorgente esterna (per 1816) | |||

|

Porta P3 bidirezionale a 8 bit con funzioni aggiuntive |

entra esci |

||

|

Dati seriali ricevitore - RxD | |||

|

Trasmettitore Dati Seriali - TxD | |||

|

Ingresso interrupt esterno 0- INT0` | |||

|

Ingresso interrupt esterno 1-INT1` | |||

|

Ingresso Timer / Contatore 0: - T0 | |||

|

Ingresso Timer/Contatore 1: - T1 | |||

|

Uscita segnale stroboscopico durante la scrittura su memoria dati esterna: - WR` | |||

|

Uscita del segnale stroboscopico durante la lettura dalla memoria dati esterna - RD` | |||

|

Cavi per il collegamento di un risonatore al quarzo. |

uscita ingresso |

||

|

Conclusione generale | |||

|

Porta P2 bidirezionale a 8 bit. Indirizzare l'uscita A8-A15 nel modo di funzionamento con memoria esterna. Nella modalità di verifica della ROM interna, i pin P2.0 - P2.6 vengono utilizzati come input dell'indirizzo A8-A14. Conclusione P2.7 - permesso di leggere ROM. |

entra esci |

||

|

Risoluzione della memoria di programma | |||

|

Segnale di uscita dell'abilitazione al mantenimento dell'indirizzo. Durante la programmazione del segnale EPROM: PROG |

entra esci |

||

|

Blocco del lavoro con memoria interna. Durante la programmazione della EPROM viene emesso il segnale UPR |

entra esci |

||

|

Porta P0 bidirezionale a 8 bit. Indirizzo / bus dati r funziona con memoria esterna. Uscita dati D7-D0 nella modalità di controllo della ROM interna (EPROM). |

entra esci |

||

|

Uscita di potenza da una sorgente di tensione + 5V |

Lo stato del sistema di interrupt viene interrogato al termine di ogni ciclo macchina nella fase S5P2, ad eccezione dei comandi RETI ed eventuali comandi riferiti ai registri IE e IP. Dal momento della correzione della richiesta di interruzione alla manutenzione dell'interruzione, occorrono da 38 a 86 periodi della frequenza fOSC, a seconda della fase della richiesta e del numero di cicli macchina del comando durante l'esecuzione di cui è stata ricevuta la richiesta .

Quando l'interrupt è implementato nell'hardware, viene eseguita l'istruzione LCALL addr16, che assicura di memorizzare nello stack lo stato corrente del contatore di programma (memorizzazione dell'indirizzo di ritorno) e di andare all'indirizzo di partenza addr16 della relativa procedura di servizio. Ogni fonte di richiesta di interruzione ha la sua

indirizzo iniziale (vettore di interruzione): |

||||

Interruzione esterna INT0. |

||||

Temporizzatore/contatore di interruzione TC0. |

||||

Interruzione esterna INT1. |

||||

Temporizzatore di interruzione/contatore TC1. |

||||

Interruzione della porta seriale. |

||||

2.7. Metodi di indirizzamento e sistema di comando della famiglia MCS-51

Il sistema di comando della famiglia MCS-51 è focalizzato sull'organizzazione flessibile dei dati di input-output attraverso le porte universali P0 ... P3 e l'elaborazione delle informazioni primarie. Attenzione speciale pagato alle operazioni con bit e trasferimento del controllo dal loro valore. Le istruzioni che eseguono tali operazioni costituiscono un grande gruppo e insieme all'hardware corrispondente formano il cosiddetto "processore booleano" nell'architettura MCS-51.

Il sistema di comando fornisce al programmatore la possibilità di utilizzare la maggior parte delle operazioni con set completo metodi di indirizzamento e risorse hardware accessibili tramite software.

2.7.1. Metodi di indirizzamento

Ciascuna istruzione indica al processore l'operazione da eseguire e le modalità di accesso agli operandi. Il codice di comando ha diversi campi che hanno uno scopo funzionale specifico. I campi più importanti di qualsiasi comando sono il codice operativo (CPC), che determina l'azione del comando, e la parte dell'indirizzo. I campi della parte indirizzo contengono informazioni sugli indirizzi degli operandi e sul risultato dell'operazione, e in alcuni casi informazioni sull'indirizzo del comando successivo.

Se l'indirizzo indica il numero della cella di memoria in cui si trova l'operando o in cui è stato immesso, viene chiamato indirizzo diretto.

I metodi di indirizzamento sono una raccolta di meccanismi per accedere agli operandi. Alcuni di essi sono semplici, portano a un formato di comando compatto e accesso veloce all'operando, ma hanno una quantità limitata di risorse disponibili. Altri permettono di operare con tutte le risorse disponibili nel sistema, ma il comando risulta essere lungo, sul suo

l'input e l'esecuzione richiedono molto tempo. L'insieme dei metodi di indirizzamento in ciascun insieme di istruzioni è una combinazione di compromesso di noti meccanismi di indirizzamento scelti dagli architetti in base all'insieme di compiti da risolvere.

Di seguito sono riportati i principali metodi di indirizzamento utilizzati nei comandi della famiglia MCS-51.

Indirizzamento implicito... Il comando non contiene istruzioni esplicite sull'indirizzo dell'operando che partecipa all'operazione o sull'indirizzo a cui è collocato il risultato dell'operazione, ma questo indirizzo è implicito. Nei comandi, l'accumulatore è spesso implicitamente indirizzato come destinatario del risultato di un'operazione. Ad esempio, il risultato della somma del contenuto dell'accumulatore (A) e del registro R1 della banca dati corrente con il comando ADD A, R1 viene scritto nell'accumulatore indirizzabile implicitamente. L'intero comando specificato occupa un byte di memoria, mentre l'indirizzo del solo accumulatore (8Eh dell'area SFR) contiene un byte.

Indirizzamento diretto... Il campo dell'indirizzo del comando contiene

L'indirizzo non è l'indirizzo dell'operando, ma l'operando stesso. L'indirizzamento diretto è indicato dal carattere speciale # davanti al numero. Ad esempio, con il comando MOV A, # 15h, il numero esadecimale 15 (il secondo byte del comando) viene caricato nell'accumulatore. Nel sistema di comando, l'indirizzamento diretto è designato come #data, dove data è un numero

(dati = 00h ... FFh).

Indirizzamento diretto... Il campo dell'indirizzo del comando indica l'indirizzo diretto della cella di memoria dati in cui si trova l'operando o dove è scritto. Ad esempio, con il comando MOV A, 15h, il contenuto della cella DSEG con indirizzo 15h viene caricato nell'accumulatore. La cella di memoria è direttamente indirizzabile, mentre l'accumulatore è implicito. A seconda della posizione dell'operando indirizzato, l'indirizzamento diretto è suddiviso in registro diretto e assoluto.

Indirizzamento diretto del registro... Il campo dell'indirizzo di comando contiene l'indirizzo diretto del registro della banca di registro corrente. Ci sono otto registri in ogni banca e per indirizzarli è necessario un indirizzo di inoltro a tre bit. Nella mnemonica dei comandi, il registro indirizzabile è designato Rn, dove n = 0 ... 7. Tutti i campi di comando rientrano in un byte. Questo è chiamato indirizzamento breve. Ad esempio, MOV R4, R1.

Indirizzamento assoluto diretto consente di fare riferimento a qualsiasi cella DSEG e area SFR. L'indirizzo diretto in questo caso è di un byte e il comando è di due byte. Nel sistema di comando, il byte di indirizzo diretto è designato dalla parola direct (direct = 00h… FFh). Ad esempio, l'istruzione MOV 80h, R2 (o MOV P0, R2) carica il contenuto del registro R2 della banca dati corrente nella porta P0 (posizione 80h dell'area SFR). Se entrambi gli operandi sono indirizzati direttamente, l'istruzione diventa a tre byte (ad es. MOV 80h, 15h).

Indirizzamento indiretto... Il campo indirizzo contiene l'indirizzo della cella di memoria in cui si trova l'indirizzo diretto dell'operando. Nel sistema di comando, il carattere speciale @ indica l'indirizzamento indiretto. Proprietà

i registri R0 e R1 (@Ri, i = 0,1) di ciascuna banca registri possiedono l'indirizzo diretto. Ad esempio, se il contenuto del registro R1 del banco di registri corrente è 15h, l'istruzione MOV A, @ R1 eseguirà la stessa azione dell'istruzione precedente MOV A, 15h - caricherà il contenuto della cella di memoria DSEG con indirizzo 15h nell'accumulatore. Tuttavia, il comando MOV A, @ R1 è a byte singolo, ma soprattutto esiste una possibilità programmaticamente modificare l'indirizzo modificando il contenuto del registro R1.

Indirizzamento relativo... Con l'indirizzamento relativo, l'indirizzo diretto viene formato sommando l'indirizzo base con il campo indirizzo di comando. Il contenuto del contatore del programma viene utilizzato come indirizzo di base e il campo dell'indirizzo del comando è un offset a otto bit rel (relativo). Il numero rel viene interpretato dal comando come un intero con segno, rappresentato in complemento a due. La gamma della sua presentazione è (-128 ... + 127). Quando si determina il numero rel, tenere presente che il contatore del programma punta al comando successivo da eseguire. L'indirizzamento relativo è ampiamente utilizzato nei comandi di trasferimento del controllo, che consente di creare moduli di programma riposizionabili. I comandi di trasferimento del controllo con relativo indirizzamento consentono di organizzare le ramificazioni relative alla posizione corrente del contatore di programmi del PC in entrambe le direzioni per (-128 ... + 127) byte.

Nei programmi in linguaggio assembly, puoi specificare l'etichetta a cui passare nel campo offset. Come risultato della traslazione, l'assemblatore calcolerà il valore di offset se non supera (-128 ... + 127). In caso contrario, verrà visualizzato un messaggio di errore.

Indirizzamento di base rappresenta una sorta di indirizzamento relativo. L'indirizzo diretto in questo caso si ottiene sommando l'indirizzo specificato nel comando con il contenuto del registro di base, che memorizza l'indirizzo di base. La funzione del registro di base nella famiglia MCS-51 è il registro del puntatore di dati DPTR o il contatore del programma per PC. Questo tipo di indirizzamento è particolarmente utile durante l'elaborazione di tabelle e array di dati. Nelle istruzioni MOVC A, @ A + DPTR e MOVC A, @ A + PC, l'indirizzo forward a 16 bit è formato dalla somma del contenuto di DPTR e A o PC e A.

Indirizzamento delle pagine... Quando si utilizza il paging, la memoria viene suddivisa in una serie di pagine di uguale lunghezza. Le pagine sono indirizzate da un registro di pagina separato e le celle di memoria all'interno della pagina sono indirizzate dall'indirizzo contenuto nel comando. L'indirizzo diretto è formato concatenando (aggiungendo) l'indirizzo delle pagine e l'indirizzo della cella di memoria all'interno della pagina. Nell'istruzione MOVX A, @ Ri, la porta P2 (indirizzo high byte) svolge la funzione del registro di pagina e il contenuto del registro Ri (indirizzo low byte) imposta l'indirizzo all'interno della pagina. In questo caso, la memoria è suddivisa in 256 pagine di 256 celle in ciascuna di esse.

Indirizzamento dello stack viene utilizzato nei comandi non indirizzabili ed è una combinazione di metodi di indirizzamento autoincrementali e autodecrementali, operanti sul principio LIFO (Last I nput - First O utput) - "last in - first out". Lo stack si trova in DSEG e cresce nella direzione dell'indirizzo crescente. L'indirizzo della parte superiore dello stack è contenuto nel puntatore dello stack SP. Quando un byte viene scritto nello stack, il contenuto SP viene prima incrementato e quindi viene eseguita una scrittura su questo indirizzo. Durante la lettura di un byte dallo stack, legge prima l'indirizzo indicato da SP, quindi decrementa SP. Quando si utilizza uno stack, tenere presente che la profondità dello stack (il numero massimo di celle di memoria occupate dallo stack) non è controllata dall'hardware. Con un aumento eccessivo dello stack, le celle di memoria che non sono destinate a questo possono essere occupate con la perdita di informazioni in esse. Lo stack hardware viene utilizzato per memorizzare l'indirizzo di ritorno durante la manutenzione dell'interrupt.

2.7.2. Set di comandi della famiglia MCS-51

Il sistema di comando è presentato nelle tabelle A2.1 ... A2.6 dell'Appendice 2. Le tabelle indicano il nome del comando, i suoi mnemonici, codice binario operazioni, l'influenza del comando eseguito sui flag C, OV, AC e P, la lunghezza del comando in byte (B) e il tempo di esecuzione in cicli macchina (C), nonché il contenuto della trasformazione eseguita da il comando. Una virgola viene utilizzata come separatore per i campi degli indirizzi nei comandi. Per migliorare la leggibilità, puoi aggiungere spazi dopo la virgola se l'assembler utilizzato li supporta.

L'intera serie di comandi può essere suddivisa in 5 gruppi: operazioni di trasferimento dati, operazioni aritmetiche, operazioni logiche, operazioni di bit e operazioni di trasferimento di controllo.

Gruppo di comandi per operazioni di trasferimento dati(tabella A2.1) con-

contiene MOV (trasferimento dati tra DSEG e RSEG), MOVC (tra CSEG e A), MOVX (tra XSEG e A), comandi di accesso allo stack PUSH e POP e due comandi di scambio XCH e XCHD. Tutti i comandi di trasferimento dati, in cui il ricevitore è la batteria, impostano il flag di parità P del contenuto della batteria e i comandi di indirizzo diretto, in cui il registro PSW è il ricevitore, cambiano tutti i flag. La più capiente è l'istruzione MOV, che utilizza quattro metodi di indirizzamento: register direct (A, Rn, DPTR), direct (direct), indirect (@Ri), direct (#data, # data16). Il secondo operando dell'istruzione è la sorgente, il primo è la destinazione. Esistono tre metodi di indirizzamento (tranne diretto) per indicare la destinazione e tutti e quattro per indicare la fonte. Il comando diretto e diretto MOV a tre byte trasferisce tra due posizioni di memoria qualsiasi (DSEG e SFR), incluso RSEG. Per lo scambio con RSEG sono previsti formati speciali a due e un byte:

L'istruzione speciale MOV DPTR, # data16, carica il puntatore DPTR a 16 bit con data16.

L'istruzione MOVC consente di leggere le informazioni dalla memoria del programma CSEG non nel registro dei comandi del dispositivo di controllo, ma nella batteria del dispositivo operativo. Il comando utilizza due metodi di indirizzamento: basato su DPTR e relativo al PC. In entrambi i casi, l'offset intero senza segno (indice) viene memorizzato nell'accumulatore. La batteria funge anche da ricevitore del risultato. Il comando consente di eseguire la transcodifica rapida tra tabelle.

Si accede alla memoria esterna usando l'istruzione MOVX. Lo scambio avviene per byte tra la batteria e l'XSEG esterno. La cella XSEG può essere indirizzata in due modi: indirettamente tramite il puntatore DPTR a 16 bit e paginata indirettamente tramite Ri a 8 bit, i = 0,1. In quest'ultimo caso, il registro delle pagine è il registro P2.

I comandi PUSH e POP non indirizzati forniscono il trasferimento dei dati

tra DSEG, RSEG e SFR.

L'istruzione di scambio XCH fornisce uno scambio bidirezionale di byte e l'istruzione XCHD fornisce le tetradi meno significative di operandi di byte.

Gruppo di comandi aritmetici(tabella A2.2) co-

contiene istruzioni per addizione ADD, addizione con riporto ADDC, sottrazione con prestito SUBB, incremento e decremento di un INC e DEC, correzione decimale additiva BCD formato compresso, moltiplicazione MUL e divisione DIV. Le operazioni vengono eseguite su numeri interi senza segno. Nelle operazioni di addizione e sottrazione, l'accumulatore è il primo operando e ricevitore del risultato. Il registro diretto, l'indirizzamento diretto assoluto, diretto e indiretto vengono utilizzati per definire il secondo operando. Le operazioni INC e DEC si applicano a un accumulatore, un registro direttamente indirizzabile o una posizione di memoria indirizzabile direttamente o indirettamente. Inoltre, l'operazione INC si applica al contenuto del registro del puntatore DPTR a 16 bit.

Le operazioni di moltiplicazione e divisione di interi senza segno coinvolgono l'accumulatore e il registro B. Nella moltiplicazione, il valore a 8 bit di A viene moltiplicato per il valore a 8 bit di B e il risultato a 16 bit viene scritto nella coppia BA. In questo caso, il registro B memorizza la parte superiore del prodotto. Il flag OV viene impostato se il prodotto è maggiore di 255. Quando un valore A a 8 bit viene diviso per un valore B a 8 bit, il quoziente viene scritto in A e il resto viene scritto in B. Un tentativo di dividere per 0 imposta il flag di overflow OV.

Il comando di correzione decimale dell'accumulatore DA viene inserito dopo il comando di aggiunta. I termini devono essere rappresentati nel codice BCD. La correzione viene eseguita in modo standard.

Gruppo di comandi per operazioni logiche(tabella A2.3 ) contiene tre operazioni tipiche: ANL - AND logico, ORL - OR logico, XRL - OR logico esclusivo. La sorgente del primo operando

serve l'accumulatore A o la cella di memoria direttamente indirizzabile. Il secondo operando è specificato da uno dei quattro metodi di indirizzamento di base. Il gruppo comprende anche singole operazioni sul contenuto dell'accumulatore: CLR - clear, CPL - inversione, e anche RL, RLC, RR e RRC - operazioni di spostamenti ciclici ed estesi a destra e a sinistra. Ciò include anche l'operazione di scambio di notebook nell'accumulatore SWAP, che può essere interpretato come uno spostamento ciclico di un byte di quattro cifre.

Gruppo di comandi per operazioni sui bit(tabella A2.6) contiene co-

Comandi SETB - impostazione di un bit a 1, CLR - ripristino di un bit a 0, CPL - inversione di bit, ANL e ORL - AND logico e OR logico del contenuto del flag C e un bit indirizzato direttamente, MOV - trasferimento di bit.

V operazioni bit, il flag C funge da accumulatore booleano. Gli operandi sono il contenuto del flag C o il bit direttamente indirizzabile del BSEG. Le operazioni ANL e ORL possono utilizzare il contenuto di un bit (bit) indirizzabile diretto o l'inversione del contenuto (/ bit).

V questo gruppo include anche i comandi per il branching condizionale con relativo Offset 8 bit rel. Un salto condizionato può essere eseguito sia con bit impostato (comando JB) che con bit azzerato (comando JNB). Di particolare rilievo è il comando JBC, che quando bit impostato implementa la ramificazione e contemporaneamente azzera il bit a 0.

Gruppo di comandi per il trasferimento di controllo(tabelle A2.4 e A2.5) con-

contiene i comandi di salto incondizionato AJMP, LJMP, SJMP, JMP, salto condizionale JZ, JNZ, CJNE, chiamata ACALL, LCALL, ritorno RET, RETI e modifica con salto condizionale DJNZ. È incluso anche un comando NOP vuoto.

V i comandi di trasferimento del controllo sono ampiamente utilizzati indirizzamento relativo consentendo di creare moduli software riposizionabili. L'indirizzo relativo è L'offset a 8 bit rel è un byte con segno che fornisce un salto (–128 ... +127) byte rispetto alla posizione corrente del PC. È possibile utilizzare l'indirizzo addr16 diretto o l'indirizzo indiretto @A + DPTR per passare a qualsiasi altro punto nello spazio degli indirizzi di 64 KB. In quest'ultimo caso, il contenuto di A viene interpretato come intero senza segno. È stata introdotta una variante dell'indirizzamento diretto breve addr11 all'interno della pagina corrente da 2 KB per compatibilità con la famiglia MCS-48.

Tutti questi tipi di indirizzamento vengono utilizzati nelle istruzioni di salto. Nei comandi di chiamata vengono utilizzati solo i metodi di indirizzamento addr16 diretto e addr11 in-page. Tutti i comandi condizionali utilizzano solo l'indirizzamento relativo.

Quando il microcontrollore riconosce la richiesta di interruzione, genera l'istruzione LCALL addr16, che garantisce automaticamente che l'indirizzo di ritorno sia memorizzato nello stack. Le informazioni sullo stato del programma (contenuto del registro PSW) non vengono salvate automaticamente. in cui