Architektura rodziny MCS-51 jest w dużej mierze zdeterminowana przez jej przeznaczenie – budowanie kompaktowy oraz tani urządzenia cyfrowe... Wszystkie funkcje mikrokomputera są realizowane za pomocą jednego mikroukładu. Rodzina MCS-51 obejmuje szereg mikroukładów od najprostszych mikrokontrolerów do najbardziej złożonych. Mikrokontrolery z rodziny MCS-51 pozwalają wykonywać zarówno zadania sterowania dla różnych urządzeń, jak i implementować poszczególne węzły obwodu analogowego. Wszystkie mikroukłady z tej rodziny działają tak samo system dowodzenia MCS-51, większość z nich wykonywana jest w tych samych przypadkach z pasujący pinout(numeracja nóg do ciała). Pozwala to na użycie mikroukładów różnych firm do opracowanego urządzenia - Maxim, Atmel, NXP itp. (catalog..php? page = components_list & id = 39 "> patrz wyszukiwanie według parametrów) bez zmian schemat urządzenia i programy.

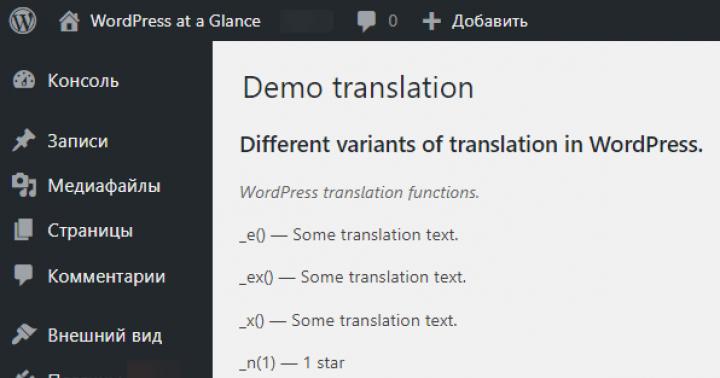

Obrazek 1. Schemat strukturalny kontroler I8751

Schemat blokowy sterownika jest przedstawiony na rysunku 1. i składa się z następujących głównych jednostek funkcjonalnych: jednostka sterująca, urządzenie arytmetyczno-logiczne, jednostka zegar/licznik, interfejs szeregowy i jednostka przerwań, licznik programu, pamięć danych i pamięć programu. Wymiana dwukierunkowa odbywa się za pomocą wewnętrznej 8-bitowej autostrady danych.

Przyjrzyjmy się bliżej celowi każdego bloku. Prawie wszyscy przedstawiciele rodziny MCS-51 są konstruowani zgodnie z tym schematem.... Różne mikroukłady z tej rodziny różnią się tylko rejestrami specjalnego przeznaczenia (w tym liczbą portów). Zestaw poleceń dla wszystkich kontrolerów rodziny MCS-51 zawiera 111 podstawowe polecenia o formacie 1, 2 lub 3 bajtów i nie zmienia się podczas przechodzenia z jednego mikroukładu do drugiego. Zapewnia to doskonałą przenośność programów z jednego mikroukładu do drugiego.

Jednostka sterująca i synchronizująca

Jednostka pomiaru czasu i kontroli jest przeznaczona do generowania sygnałów synchronizacji i sterowania w celu zapewnienia koordynacji pracować razem Jednostki OEVM we wszystkich dopuszczalnych trybach pracy Jednostka sterująca zawiera:

- - urządzenie do formowania przedziałów czasowych,

- - logika we/wy,

- - rejestr poleceń,

- - rejestr kontroli zużycia energii elektrycznej,

- - dekoder poleceń, logika sterowania komputerowego.

Urządzenie do kształtowania szczelin czasowych jest przeznaczony do tworzenia i wydawania wewnętrznych sygnałów synchronizacji faz, zegarów i cykli. Liczba cykli maszyny określa czas wykonania instrukcji. Prawie wszystkie polecenia OEVM są wykonywane w jednym lub dwóch cyklach maszynowych, z wyjątkiem poleceń mnożenia i dzielenia, których czas trwania wynosi cztery cykle maszynowe. Wyznaczmy częstotliwość oscylatora głównego przez F g. Wtedy czas trwania cyklu maszyny wynosi 12 / F g lub 12 okresów sygnału oscylatora głównego. Logika wejścia-wyjścia została zaprojektowana do odbierania i wysyłania sygnałów zapewniających wymianę informacji z urządzeniami zewnętrznymi poprzez porty wejścia/wyjścia P0-P3.

Rejestr poleceń służy do rejestrowania i przechowywania 8-bitowego kodu operacji wykonywanego polecenia. Kod operacji, za pomocą dekodera poleceń i logiki sterowania komputerem, jest przekształcany w mikroprogram do wykonywania poleceń.

Rejestr kontroli zużycia (PCON) pozwala na zatrzymanie mikrokontrolera w celu zmniejszenia zużycia energii i zmniejszenia poziomu szumów z mikrokontrolera. Dalszą redukcję zużycia energii i redukcję szumów można osiągnąć poprzez zatrzymanie głównego oscylatora mikrokontrolera. Można to osiągnąć przez odwrócenie nieco w rejestrze kontroli zużycia PCON. W przypadku wariantu n-MOS (seria 1816 lub obce układy bez „c” w środku), rejestr kontroli zużycia PCON zawiera tylko jeden bit, który kontroluje szybkość transmisji portu szeregowego SMOD i nie ma bitów sterowania mocą.

Jednostka arytmetyczno-logiczna (ALU) to równoległe ośmiobitowe urządzenie, które wykonuje operacje arytmetyczne i logiczne. ALU składa się z:

- - rejestry akumulatorowe, rejestry podtrzymujące TMP1 i TMP2,

- - stałe ROM,

- - sumator,

- - rejestr dodatkowy (rejestr B),

- - bateria (ACC),

- - rejestr statusu programu (PSW).

Zarejestrować bateria oraz księgi rachunkowe- ośmiobitowe rejestry przeznaczone do odbierania i przechowywania operandów na czas wykonywania na nich operacji. Te rejestry nie są dostępne programowo.

Stałe ROM zapewnia generowanie kodu korekcyjnego dla reprezentacji danych binarno-dziesiętnych, kodu maski dla operacji bitowych i kodu stałego.

Równoległy ośmiobitowy sumator reprezentuje obwód kombinowany z transferem sekwencyjnym, przeznaczony do wykonywania operacji arytmetycznych dodawania, odejmowania oraz operacji logicznych dodawania, mnożenia, nierównych i identycznych.

Zarejestruj się- ośmiobitowy rejestr używany podczas operacji mnożenia i dzielenia. W przypadku innych instrukcji można go traktować jako dodatkowy rejestr superoperacyjny.

Bateria- ośmiobitowy rejestr przeznaczony do odbierania i przechowywania wyniku uzyskanego podczas wykonywania operacji arytmetyczno-logicznych lub operacji przesuwnych

Interfejs szeregowy i blok przerwań (PIP) jest przeznaczony do organizacji wejścia-wyjścia sekwencyjnych strumieni informacji oraz organizacji systemu programów przerywających. W skład bloku wchodzą:

- - bufor PIP,

- - logika sterowania,

- - rejestr kontrolny,

- - bufor nadajnika,

- - bufor odbiornika,

- - transceiver portu szeregowego,

- - rejestr priorytetów przerwań,

- - rejestr włączania przerwań,

- - logika przetwarzania flag przerwań i układu generowania wektorów.

Licznik programu przeznaczony do tworzenia aktualnego 16-bitowego adresu wewnętrznej pamięci programu oraz 8/16-bitowego adresu pamięć zewnętrzna programy. Licznik instrukcji zawiera 16-bitowy bufor PC, rejestr PC i obwód inkrementacyjny (zwiększający zawartość o 1).

Pamięć danych (RAM) służy do tymczasowego przechowywania informacji wykorzystywanych w procesie wykonywania programu.

Porty P0, P1, P2, P3 są quasi-dwukierunkowymi portami wejścia-wyjścia i mają za zadanie zapewnić wymianę informacji między komputerem a urządzeniami zewnętrznymi, tworząc 32 linie wejścia-wyjścia.

Urządzenie czasowe V podstawowe modele Rodzina posiada dwa programowalne 16-bitowe timery/liczniki (T/C0 i T/C1), które mogą być używane zarówno jako timery, jak i jako zewnętrzne liczniki zdarzeń

Rejestr statusu programu (PSW) przeznaczony do przechowywania informacji o stanie jednostki ALU podczas wykonywania programu.

Pamięć programu (EPROM) jest przeznaczony do przechowywania programów i jest pamięcią tylko do odczytu (ROM). Różne mikroukłady używają pamięci ROM masek, usuwalnych przez promieniowanie ultrafioletowe lub LAMPA BŁYSKOWA ROM.

Rejestr wskaźników danych (DPTR) jest przeznaczony do przechowywania 16-bitowego adresu zewnętrznej pamięci danych lub pamięci programu.

Wskaźnik stosu (SP) to ośmiobitowy rejestr przeznaczony do organizowania specjalnego obszaru pamięci danych (stosu), w którym można tymczasowo przechowywać dowolną komórkę pamięci.

Wersja podstawowa MCS-51 Krótka informacja. Współczesne mikrokontrolery 8-bitowe (MC) posiadają takie zasoby sterowania w czasie rzeczywistym, które wcześniej uzyskiwano przy użyciu drogich układów wielochipowych w postaci osobnych płytek mikrokomputerowych, a mianowicie:

● posiadać wystarczającą pojemność pamięci, jej fizyczny i logiczny podział na pamięć programu i pamięć danych (architektura Harvarda) oraz system poleceń skoncentrowany na realizacji algorytmów sterowania;

● zawiera wszystkie urządzenia (procesor, ROM, RAM, porty we/wy, system przerwań, urządzenia do przetwarzania informacji bitowych itp.) wymagane do wdrożenia systemu sterowania mikroprocesorowego o minimalnej konfiguracji. W latach 70. ubiegłego wieku firma Intel opracował i opanował produkcję przemysłową rodziny 8-bitowych mikrokontrolerów MCS-48, których łączy szereg wspólnych cech (głębokość bitowa, system poleceń, zestaw podstawowych bloków funkcjonalnych itp.). Podstawowa wersja tej rodziny obejmuje:

● 8-bitowy procesor;

● wewnętrzna pamięć programu (1/2/4K bajtów);

● wewnętrzna pamięć danych (64/128/256 bajtów);

● do 27 wewnętrznych i 16 zewnętrznych linii I/O;

● jeden 8-bitowy licznik czasu;

● jednopoziomowy system przerwań z dwoma źródłami żądań. W 1980 roku ta sama firma opracowała nową rodzinę ośmiobitowych mikrokontrolerów MCS-51, która jest zgodna z architekturą rodziny MCS-48, ale ma większe możliwości.

Architektura rodziny MCS-51 okazała się na tyle udana, że nadal jest jednym ze standardów dla 8-bitowych MCU. Dlatego jako obiekt badań wybrano MC z tej rodziny, które rozpowszechniły się w stosunkowo prostych układach sterowania.

Dla rodziny MCS-51 opracowano różne narzędzia do przygotowywania programów (kompilatory, emulatory sprzętowo-programowe itp.) i istnieje duża liczba standardowych bibliotek podprogramów. Rodzina obejmuje różne modyfikacje mikroukładów (wersje kryształowe) mikrokontrolerów. W artykułach tego rozdziału podstawowa wersja mikrokontrolerów z rodziny MCS-51 (mikroukład 8051 odpowiada krajowemu analogowi KP1816BE51) jest rozważana wystarczająco szczegółowo, najprostsza pod względem konstrukcyjnym i funkcjonalnym oraz z punktu widzenia zrozumienia.

Kolejne serie mikroukładów, przy zachowaniu kompatybilności z wersją podstawową, różnią się od niej ulepszoną technologią wykonania, parametrami elektrycznymi, dodatkowym sprzętem i funkcjonalnością. Poniższe artykuły poświęcone są cechom konstrukcyjnym i funkcjonalnym kolejnych modyfikacji mikroukładów z rodziny MCS-51.  Uogólniony schemat blokowy MCS-51. Skład MC, którego uogólniony schemat blokowy pokazano na ryc. 7.1.1 obejmuje:

Uogólniony schemat blokowy MCS-51. Skład MC, którego uogólniony schemat blokowy pokazano na ryc. 7.1.1 obejmuje:

● 8-bitowy procesor Procesor składający się z ALU, urządzenia sterujące Uu i generator adresów F;

● maska ROM o pojemności 4K bajtów do przechowywania programów;

● RAM o pojemności 128 bajtów do przechowywania danych;

● cztery programowalne porty P0-P3 dla wejścia - informacje wyjściowe;

● blok interfejsu szeregowego BPI do wymiany informacji z urządzeniami zewnętrznymi za pośrednictwem linii dwuprzewodowej;

● blok timerów/liczników BT/C do utrzymywania trybu czasu rzeczywistego;

● blok przerwań BP do organizowania przerwań programów wykonywalnych. Te fundusze tworzą Mieszkaniec część mikrokontrolera umieszczona bezpośrednio na chipie. MC zawiera dużą liczbę rejestrów, które są przypisane do oddzielnych bloków funkcjonalnych i nie są pokazane na schemacie.

Schemat również nie pokazuje obwodów sterowania. Dwukierunkowa wymiana informacji między blokami odbywa się za pośrednictwem wewnętrznego 8-bitowego magistrala danych-8.

Wewnętrzny 16-bitowy autobus adresowy SHA-16 adres utworzony w CPU wyświetlany jest w ROM (12 bitów adresu) oraz w pamięci RAM (8 najmniej znaczących bitów).

W przypadku korzystania z pamięci zewnętrznej 8 najmniej znaczących bitów adresu jest wysyłanych do portu P0, a 3 lub 8 najbardziej znaczących bitów do portu P2.

Do logicznego rozszerzenia interfejsu wykorzystuje się kombinację funkcji linii portowych. Jako przykład, ryc. 7.1.1 linia przerywana pokazuje linie portu P3, wykonujące alternatywny funkcje przesyłania sygnałów sterujących, których cel zostanie omówiony poniżej. Aby utworzyć wewnętrzny generator zegara, rezonator kwarcowy i dwa kondensatory są podłączone do zacisków mikroukładu MK (ryc. 7.1.1). Zamiast wewnętrznego zegara do synchronizacji można użyć zewnętrznego oscylatora. Konwencjonalne oznaczenie graficzne mikroukładu MK pokazano na ryc. 2, oznaczenie i cel wniosków – w tabeli. 7.1.1. Rozważ bloki funkcjonalne MK i zasadę ich działania.  Jednostka arytmetyczno-logiczna. Jednostka arytmetyczno-logiczna jest przeznaczona do wykonywania operacji arytmetycznych (w tym mnożenia i dzielenia) i logicznych na ośmiobitowych operandach, a także operacji przesunięcia logicznego, zerowania, ustawiania itp. Schemat blokowy jednostki ALU pokazano na ryc. 7.1.3.

Jednostka arytmetyczno-logiczna. Jednostka arytmetyczno-logiczna jest przeznaczona do wykonywania operacji arytmetycznych (w tym mnożenia i dzielenia) i logicznych na ośmiobitowych operandach, a także operacji przesunięcia logicznego, zerowania, ustawiania itp. Schemat blokowy jednostki ALU pokazano na ryc. 7.1.3.

ALU zawiera

● równoległy ośmiobitowy sumator SM typu kombinacyjnego z sekwencyjnym przeniesieniem, wykonującym operacje arytmetyczne (dodawanie i odejmowanie) i logiczne (dodawanie, mnożenie, nierówne i identyczne);

● bateria A, udostępnianie funkcji głównego rejestru arytmetycznego;

● Zarejestruj się B, służący do realizacji operacji mnożenia i dzielenia lub jako dodatkowy rejestr nadoperacyjny, którego funkcje definiuje użytkownik;

● rejestry(niedostępne programowo) tymczasowe przechowywanieРВХ1, РВХ2, przeznaczone do odbioru i przechowywania operandów na czas operacji;

● ROM stałe ROMK, który przechowuje kod korekcyjny dla reprezentacji danych binarno-dziesiętnych, kod maskujący dla operacji bitowych i kod stały;

● Rejestr słów statusu programu PSW, który naprawia stan jednostki ALU po wykonanej operacji. Tabela 7.1.2 zawiera informacje o przydziale bitów poszczególnych bitów rejestru PSW. Urządzenie sterujące. Jednostka sterująca (CU) procesora centralnego przeznaczony koordynowanie wspólnej pracy wszystkich węzłów MK za pomocą generowanych impulsów synchronizacji i sygnałów sterujących. Obejmuje (rys. 7.1.4):

● synchronizacja i jednostka sterująca USU, który generuje impulsy synchronizacji ustawiające cykle maszyny i ich poszczególne stany (S) i fazy (P) oraz, w zależności od trybu pracy MC, generuje niezbędny zestaw sygnałów sterujących. Na wykonanie polecenia przydzielany jest jeden, dwa lub cztery cykle maszynowe.

Każdy cykl maszyny ma sześć stanów S1 – S6, A każdy stan zawiera dwie fazy P1, P2, którego czas trwania jest okresem oscylacji generatora zegara T 0SC.

Czas trwania cyklu maszyny to 12T 0SC. Wszystkie cykle maszyny są takie same, zaczynając od fazy S1P1 i kończąc na fazie S6P2.

Oprócz impulsów synchronizujących urządzenie synchronizujące w każdym cyklu maszyny generuje dwa (czasem jeden) sygnały strobujące niskiego bajtu adresu ALE w postaci impulsu dodatniego w fazach S1P2 – S2P1 i S4P2 – S5P1. Schematy czasowe na ryc. 7.1.5 ilustrują organizację cykli maszynowych;

● rejestr komend RK, dekoder poleceń DC i PLM, umożliwiające w każdym cyklu maszyny utworzenie zestawu mikrooperacji zgodnie z mikroprogramem wykonywanego polecenia;

● logiczne I/O LVV do odbierania i wydawania sygnałów zapewniających wymianę informacji MC z urządzeniami zewnętrznymi poprzez porty P0-P3;

● rejestr PCON z pojedynczym włączonym bitem SMOD w pozycji PCON.7 w celu podwojenia szybkości transmisji portu szeregowego. Pozostałe bity są zarezerwowane do wykorzystania w przyszłości.  Generator adresów. Generator adresów (FA) lub licznik poleceń PC, przeznaczony aby utworzyć aktualny 16-bitowy adres pamięci programu i 8/16-bitowy adres zewnętrznej pamięci danych. Obejmuje (ryc. 7.1.6):

Generator adresów. Generator adresów (FA) lub licznik poleceń PC, przeznaczony aby utworzyć aktualny 16-bitowy adres pamięci programu i 8/16-bitowy adres zewnętrznej pamięci danych. Obejmuje (ryc. 7.1.6):

● 16-bitowy bufor B, który komunikuje się między 8-bitową szyną danych modułu SM a 16-bitową szyną wewnętrzną (ID) generatora adresu;

● schemat inkrementacji SI zwiększający wartość aktualnego adresu pamięci programu o jeden;

● rejestr do przechowywania aktualnego adresu poleceń PTA pochodzących z SI;

● Rejestr wskaźników danych DPTR , składający się z dwóch 8-bitowych rejestrów DPH i DPL. Służy do przechowywania 16-bitowego adresu zewnętrznej pamięci danych i może być używany jako dwa niezależne RON dostępne z poziomu oprogramowania;

● rejestr układu XPA adresowania do przechowywania wykonawczego 16-bitowego adresu pamięci programu lub 8/16-bitowego adresu zewnętrznej pamięci danych. Rejestr ten jest również używany do przesyłania danych przez port P0 do urządzeń zewnętrznych podczas wykonywania poleceń MOVX @Rm, A i MOVX @DPRT, A.

Pamięć danych. Pamięć danych przeznaczony do odbierania, przechowywania i wydawania informacji wykorzystywanych w procesie wykonywania programu. Pamięć wewnętrzna (rezydentna) (rys. 7.1.7) dane składa się z pamięci RAM o pojemności 128 bajtów, wskaźnik stosu SP, rejestr adresów RAM RA i dekoder Dsz.  Stack Pointer SP to 8-bitowy rejestr przeznaczony do odbierania i przechowywania adresu komórki stosu, do której ostatnio uzyskano dostęp. Po resecie we wskaźniku stosu ustawiany jest adres 07H, który odpowiada początkowi stosu o adresie 08H. Rejestr adresu PA wraz z dekoderem Dsh umożliwia dostęp do wymaganej komórki pamięci zawierającej bajt lub bit informacji.

Stack Pointer SP to 8-bitowy rejestr przeznaczony do odbierania i przechowywania adresu komórki stosu, do której ostatnio uzyskano dostęp. Po resecie we wskaźniku stosu ustawiany jest adres 07H, który odpowiada początkowi stosu o adresie 08H. Rejestr adresu PA wraz z dekoderem Dsh umożliwia dostęp do wymaganej komórki pamięci zawierającej bajt lub bit informacji.

MK zapewnia możliwość zwiększenia ilości pamięci danych do 64 KB poprzez podłączenie zewnętrzne urządzenia pamięci masowej. Jako przykład, ryc. 7.1.8 pokazuje organizację strony zewnętrznej pamięci danych FPD o pojemności 2K bajtów za pomocą instrukcji typu MOVX @

Rm (m = 0; 1). W tym przypadku port P0 pracuje jako multipleksowana magistrala adresowa / danych, trzy linie portu P2 służą do adresowania strony zewnętrznej pamięci RAM, a pozostałe pięć można wykorzystać jako linie we/wy.  Na ryc. 7.1.9 pokazuje diagramy czasowe cykli odczytu i zapisu, gdy MK pracuje z zewnętrzną pamięcią RAM. Schematy wskazują:

Na ryc. 7.1.9 pokazuje diagramy czasowe cykli odczytu i zapisu, gdy MK pracuje z zewnętrzną pamięcią RAM. Schematy wskazują:

● PCN - starszy bajt licznika poleceń PC;

● DPL, DPH - młodsze i starsze bajty rejestru wskaźnika danych DPTR, który jest wykorzystywany jako rejestr do adresowania pośredniego w instrukcjach MOVX @DPTR, A i MOVX A, @DPTR;

● P2 SFR - zatrzaski portu P2;

● Rm (m = 0, 1) - rejestry używane w instrukcjach MOVX @Rm, A i MOVX A, @Rm jako rejestry adresów pośrednich;

● Z - stan wysokiej rezystancji;

● D - okres, w którym do mikrokontrolera wprowadzane są dane z portu P0.  Pamięć programu. Pamięć programu przeznaczona jest do przechowywania programów, posiada własną (oddzielną od pamięci danych) przestrzeń adresową i jest dostępna tylko do odczytu. Zawiera dekoder DSh i ROM (ryc. 7.1.10).

Pamięć programu. Pamięć programu przeznaczona jest do przechowywania programów, posiada własną (oddzielną od pamięci danych) przestrzeń adresową i jest dostępna tylko do odczytu. Zawiera dekoder DSh i ROM (ryc. 7.1.10).  Do adresowania pamięci programu wykorzystywany jest 16-bitowy licznik PC, więc jego maksymalna pojemność to 64K bajtów. Wewnętrzna pamięć programu składa się z 4 KB pamięci ROM i 12-bitowego dekodera. Pamięć zewnętrzną podłącza się zgodnie ze schematem na rys. 7.1.11.

Do adresowania pamięci programu wykorzystywany jest 16-bitowy licznik PC, więc jego maksymalna pojemność to 64K bajtów. Wewnętrzna pamięć programu składa się z 4 KB pamięci ROM i 12-bitowego dekodera. Pamięć zewnętrzną podłącza się zgodnie ze schematem na rys. 7.1.11.  Jeśli 0 V zostanie przyłożone do pinu ¯EA MK (jak pokazano na rys. 7.1.11), wewnętrzna pamięć programu jest wyłączona. Wszystkie dostępy do pamięci zaczynają się od adresu 0000h. Po podłączeniu do zasilania pinu EA następuje automatyczny dostęp do wewnętrznej pamięci programu o adresach 0000h – FFFFh oraz zewnętrznej pamięci programu o adresach 0FFFh – FFFFh.

Jeśli 0 V zostanie przyłożone do pinu ¯EA MK (jak pokazano na rys. 7.1.11), wewnętrzna pamięć programu jest wyłączona. Wszystkie dostępy do pamięci zaczynają się od adresu 0000h. Po podłączeniu do zasilania pinu EA następuje automatyczny dostęp do wewnętrznej pamięci programu o adresach 0000h – FFFFh oraz zewnętrznej pamięci programu o adresach 0FFFh – FFFFh.

Aby odczytać pamięć zewnętrzną programów MK, generowany jest sygnał ¯PSEN. Przy pracy z pamięcią wewnętrzną sygnał odczytu nie jest wykorzystywany. Przy dostępie do zewnętrznej pamięci programu zawsze tworzony jest adres 16-bitowy. Młodszy bajt adresu jest transmitowany przez port P0 w pierwszej połowie cyklu maszyny i jest ustalany na krawędzi strobu ALE w rejestrze.W drugiej połowie cyklu port P0 służy do wprowadzania bajt danych z pamięci zewnętrznej do MC.

Bajt wyższego rzędu adresu jest przesyłany przez port P2 przez cały czas dostępu do pamięci.

Wykresy czasowe cykli odczytu i zapisu, gdy MC pracuje z zewnętrzną pamięcią RAM, pokazano na rys. 7.1.12.  Schematy wskazują:

Schematy wskazują:

● PCL OUT - wydanie najmniej znaczącego bajtu licznika komend PC;

● РСН OUT - wysyłanie starszego bajtu licznika poleceń PC;

● DPH - starszy bajt rejestru wskaźnika danych DPTR, który jest wykorzystywany jako rejestr do adresowania pośredniego w instrukcjach MOVX @DPTR, A i MOVX A, @DPTR;

● P2 SFR - zatrzaski portu P2;

● INS IN - wprowadzenie bajtu instrukcji (polecenia) z pamięci programu;

● ADDR OUT - wydawanie młodszego bajtu adresu zewnętrznej pamięci danych z rejestrów Rm (m = 0, 1) lub z rejestru DPL (niski rejestr DPTR). Porty we/wy. Przypisanie portu. Porty P0, P1, P2, P3 przeznaczony do wymiany informacji między MK a urządzeniami zewnętrznymi, a także do wykonywania następujących funkcji:

● młodszy bajt adresu A7...A0 jest wyprowadzany przez port P0; wyjście z MC i wejście do bajtu danych MC przy pracy z zewnętrzną pamięcią programu i zewnętrzną pamięcią danych (z podziałem czasu);

● starszy bajt adresu A15 ... A8 jest wyprowadzany przez port P2 podczas pracy z zewnętrzną pamięcią programu i zewnętrzną pamięcią danych (tylko przy użyciu poleceń MOVX A, @DPTR i MOVX @DPTR, A);

● Linie portu P3 mogą być używane do wykonywania alternatywnych funkcji, jeśli w zatrzasku tej linii zostanie wprowadzone 1, w przeciwnym razie na wyjściu linii jest ustawione 0. Alternatywne funkcje wyjść portu P3 podano w tabeli. 7.1.3.

Schematyczne funkcje portów

Na ryc. 7.1.13 przedstawia schematy dla jednego kanału każdego z portów MK, w tym:

● zatrzask do zatrzaskiwania odebranego bitu danych;

● wzmacniacz wyjściowy kaskada(kierowca);

● węzeł wiąże się z stopień wyjściowy (z wyjątkiem P2);

● łańcuch do transmisji bitu danych od strony wyjścia portu, składający się z buforów B2 i B3 (dla portu P4). Zatrzask jest D-flip-flop taktowany wewnętrznym sygnałem „Zapisz do zatrzasku”. Bit danych z bezpośredniego wyjścia D-flip-flop może być odczytany programowo przez bufor B1 za pomocą sygnału „Read latch” do linii wewnętrznej magistrali danych (SD) MC.

Stopień wyjściowy port P0 to falownik, którego cechy przejawiają się w tym, że tranzystor obciążenia VT2 otwiera się tylko podczas dostępu do pamięci zewnętrznej (przy przesyłaniu adresów i danych przez port). We wszystkich innych trybach tranzystor obciążenia jest zamknięty. Dlatego, aby użyć P0 (ryc. 7.1.13, a) jako portu wyjściowego ogólny cel do jego zacisków należy podłączyć zewnętrzne rezystory obciążające. Podczas zapisywania 1 do zatrzasku portu tranzystor falownika VT1 jest blokowany, a wyjście zewnętrzne portu P0.X jest przełączane w stan wysokiej rezystancji. W tym trybie pin portu P0.X może służyć jako wejście. Jeśli port P0 jest używany jako port we/wy ogólnego przeznaczenia, każdy z jego pinów P0.X może działać niezależnie od innych jako wejście lub wyjście. Stopnie wyjściowe porty P1, P2, P3 (rys.7.1.13, b, c, d) wykonane zgodnie z obwodami falownika z wewnętrznym rezystorem obciążenia, który jest używany jako tranzystor VT2.

Aby skrócić czas przełączania podczas przejścia wyjść portu ze stanu 0 do stanu 1, dodatkowy tranzystor VT3 jest wprowadzany równolegle z tranzystorem obciążenia VT2. Tranzystor VT3 za pomocą elementów w obwodzie bramki jest odblokowywany na czas równy dwóm okresom oscylacji głównego oscylatora kwarcowego (podczas faz S1P1, S2P2 cyklu maszyny). Stopnie wyjściowe porty P0, P2 (rys.7.1.13,A,c) za pomocą multipleksera MX można podłączyć albo do zatrzasków, albo do magistral wewnętrznych „Adres/Dane” i „Adres”. Stopień wyjściowy portu P1 (rys.7.1.13, 6) jest na stałe połączony z zatrzaskiem.

Jeżeli pin portu P3 jest wyjściem, a jego zatrzask zawiera 1, to jego stopień wyjściowy jest sterowany sprzętowym sygnałem wewnętrznym „Alternative output function”, który zapewnia wykonanie odpowiedniej alternatywnej funkcji, tj. jeden z sygnałów WR, ¯RD lub RxD jest generowany na styku zewnętrznym. Jeśli pin portu jest używany jako wejście, wówczas alternatywny sygnał docierający do niego (TxD, ¯INT0, ¯INT1, T0, T1) jest przesyłany do rozszerzenia „Alternatywna funkcja wejścia”.

Tryb zapisu portu.

Po wykonaniu polecenia zapisu do portu nowa wartość jest zapisywana do zatrzasku w fazie S6P2 i jest wyprowadzana bezpośrednio na pin wyjściowy portu w fazie S1P1 następnego cyklu maszyny.

Tryb odczytu portu

Polecenia odczytu portu odczytują informacje bezpośrednio z kontakty zewnętrzne piny portu lub wyjścia zatrzaskowe. W pierwszym przypadku bit danych z wyjścia portu jest odczytywany programowo przez bufor B2 sygnałem „Odczyt pinów” na linię wewnętrznej magistrali danych (SD) MC. Należy zauważyć, że sygnały „Write to latch”, „Read latch”, „Read piny” są generowane przez sprzęt podczas wykonywania odpowiednich poleceń.

W drugim przypadku realizowany jest tak zwany tryb „odczyt-modyfikacja-zapis”, w którym polecenie odczytuje sygnał stanu zatrzasku, w razie potrzeby modyfikuje go, a następnie zapisuje z powrotem do zatrzasku. Tryb „Odczyt-Modyfikacja-Zapis” jest zaimplementowany, gdy wykonywane są następujące polecenia: ANL, ORL, XRL, JBC; CPL; INC; grudzień; DJNC; MOV PX, Y; CLR PX.Y; SETB PX, Y.

Odczytanie informacji z wyjść zatrzasków eliminuje błędy przy interpretacji poziomu logicznego na pinie portu. Przeczytaj kontynuację artykułu w.

Intel jest przodkiem architektury rodziny MCS-51, która swoją nazwę wzięła od pierwszego przedstawiciela tej rodziny - mikrokontrolera 8051, wydanego w 1980 roku w oparciu o technologię n-MOS. Udany zestaw urządzeń peryferyjnych, elastyczny wybór zewnętrznej lub wewnętrznej pamięci programu oraz przystępna cena zapewniły temu mikrokontrolerowi sukces na rynku. Z punktu widzenia technologii mikrokontroler 8051 był na swoje czasy produktem bardzo złożonym - w krysztale użyto 128 tysięcy tranzystorów, czyli 4 razy więcej niż liczba tranzystorów w 16-bitowym mikroprocesorze 8086. Ten mikrokontroler pozostaje trzon rodziny MCS-51 do dziś.

Główne elementy podstawowej architektury rodziny (architektura mikrokontrolera 8051) to:

8-bitowa jednostka ALU;

4 banki rejestrów po 8 w każdym;

Wewnętrzna (rezydentna) pamięć programu 4 KB, typu ROM lub EPROM (8751);

Wewnętrzna (rezydentna) pamięć danych 128 bajtów;

21 rejestrów funkcji specjalnych;

procesor logiczny;

Dwa 16-bitowe timery / liczniki

Kontroler portu szeregowego (UART);

Kontroler przerwań z dwoma poziomami priorytetu;

Cztery 8-bitowe porty I/O, z których dwa są używane jako magistrala adresowa/danych w celu uzyskania dostępu do zewnętrznego programu i pamięci danych;

Wbudowany generator zegara.

Następnie wydano mikrokontroler 8052, który wyróżniał się zwiększoną ilością rezydentnej pamięci programu i danych, wprowadzoną przez trzeci zegar i odpowiednio rozszerzony kontroler przerwań.

Kolejnym zasadniczym krokiem w rozwoju MCS-51 było przeniesienie technologii wytwarzania na CMOS (modyfikacja 8xC51). Umożliwiło to zaimplementowanie trybów Idl (idle) i Power Down (zmniejszony pobór), które zapewniają gwałtowny spadek poboru mocy kryształu i otworzyły drogę do wykorzystania mikrokontrolera w aplikacjach niestabilnych, na przykład w samodzielne urządzenia zasilane bateryjnie.

Ostatnim ważnym etapem rozwoju MK 8051 przez firmę Intel było wypuszczenie na rynek mikrokontrolerów 8xC51FA/FB/FC i 8xC51RA/RB/RC, które w skrócie są często określane jako 8xC51Fx i 8xC51Rx. Główny osobliwość ta grupa kryształów polega na tym, że mają dedykowany zegar/licznik (PCA). Dodatkowo mikrokontrolery 8xC51Rx zawierają dodatkowo watchdog timer (WDT). Przyjrzyjmy się bliżej architekturze i funkcjonalności PCA.

PCA obejmuje:

16-bitowy zegar / licznik;

Pięć 16-bitowych modułów próbkowania i porównywania, z których każdy jest podłączony do własnej linii portu I/O mikrokontrolera.

Timer / licznik obsługuje wszystkie pięć modułów próbkowania i porównania, które można zaprogramować do wykonywania jednej z następujących funkcji:

16-bitowe próbkowanie wartości timera na dodatnim zboczu sygnału zewnętrznego;

16-bitowe próbkowanie wartości timera na ujemnym zboczu sygnału zewnętrznego;

16-bitowe próbkowanie wartości timera na dowolnym zboczu sygnału zewnętrznego;

16-bitowy programowalny timer;

16-bitowe szybkie urządzenie wyjściowe;

8-bitowy PWM.

Wszystkie powyższe funkcje realizowane są w PCA na poziomie sprzętowym i nie obciążają procesora centralnego. Pozwala to na zwiększenie ogólnej przepustowości, poprawę dokładności pomiarów i przetwarzania sygnałów oraz skrócenie czasu reakcji mikrokontrolera na zdarzenia zewnętrzne, co jest szczególnie ważne w przypadku systemów czasu rzeczywistego. PCA zaimplementowany w 8xC51Fx (8xC51Rx) okazał się tak

|

Przeznaczenie |

Maks. częstotliwość (MHz) |

ROM / EPROM (bajt) |

liczniki | ||

na szczęście architektura tych mikrokontrolerów stała się standardem przemysłowym, a sam PCA był wielokrotnie powielany w różnych modyfikacjach MK 8051.

Niektóre cechy wielu mikrokontrolerów MCS-51 produkowanych przez firmę Intel przedstawiono w tabeli 1.1.

Początkowymi wąskimi gardłami architektury MCS-51 były 8-bitowe jednostki ALU oparte na bateriach i stosunkowo wolne wykonywanie instrukcji (najszybsze instrukcje wymagają 12

Tabela 1.1

|

wejście wyjście |

ADC, wejścia x bity |

obrzeże, osobliwości |

U dołu. (V) |

||

|

Opcja niskiego napięcia | |||||

|

4 poziomy IRQ, wyjście zegara | |||||

|

4 poziomy IRQ, wyjście zegara | |||||

|

Wersja niskonapięciowa 8xC51Fx | |||||

|

4 poziomy IRQ, wyjście zegara | |||||

|

4 poziomy IRQ, wyjście zegara | |||||

|

4 poziomy IRQ, wyjście zegara | |||||

częstotliwość zegara okresu (częstotliwość zegara MK)). Ograniczało to wykorzystanie mikrokontrolerów z tej rodziny w aplikacjach wymagających zwiększonej wydajności i złożonych obliczeń (16- i 32-bitowe). Pilną kwestią była zasadnicza modernizacja architektury MCS-51. Problem modernizacji komplikował fakt, że na początku lat 90. powstało już wiele zmian w zakresie oprogramowania i sprzętu rodziny MCS-51, w związku z czym jedno z głównych zadań projektowych nowa architektura było wdrożenie kompatybilności sprzętowej i programowej z rozwiązaniami opartymi na MCS-51.

Aby rozwiązać ten problem, powstała wspólna grupa specjalistów Intela i Philipsa, ale później drogi tych dwóch firm rozeszły się. W rezultacie w 1995 roku pojawiły się dwie znacząco różne rodziny: MCS-251/151 firmy Intel i MCS-51XA firmy Philips (patrz podrozdział 1.2).

Główne cechy architektury MCS-251:

24-bitowa liniowa przestrzeń adresowa do adresowania do 16 MB pamięci;

Architektura rejestrów, która umożliwia dostęp do rejestrów jako bajtów, słów i podwójnych słów;

tryb adresowania stron w celu przyspieszenia pobierania instrukcji z zewnętrznej pamięci programu;

Kolejka instrukcji;

Rozszerzony zestaw instrukcji obejmujący 16-bitowe operacje arytmetyczne i logiczne;

Rozszerzona przestrzeń adresowa stosu (do 64 KB);

Robisz najwięcej szybkie polecenie w 2 cyklach zegara.

Zestaw instrukcji MCS-251 zawiera dwa zestawy instrukcji - pierwszy zestaw jest kopią zestawu instrukcji MCS-51, a drugi składa się z rozszerzonych instrukcji wykorzystujących architekturę MCS-251. Przed użyciem mikrokontrolera należy go skonfigurować, tj. z pomocą programatora „wypal” bity konfiguracyjne określające, który z zestawów instrukcji stanie się aktywny po włączeniu zasilania. Jeśli zainstalujesz pierwszy zestaw instrukcji, to w e ta walizka MCS rodziny MCS-251 będzie kompatybilny binarnie z MCS-51. Ten tryb nazywa się trybem binarnym. Jeśli początkowo zainstalujesz zestaw rozszerzonych instrukcji (tryb źródłowy), programy napisane dla MCS-51 będą wymagały ponownej kompilacji na zasadzie cross-medium dla MCS-251. Tryb źródłowy pozwala w pełni wykorzystać architekturę MCS-251 i osiągnąć najwyższą wydajność.

Dla użytkowników skoncentrowanych na wykorzystaniu mikrokontrolerów MCS-251 jako mechanicznego zamiennika MCS-51, Intel produkuje mikrokontrolery MCS-151, już zaprogramowane w trybie Binary Mode.

Niektóre cechy wielu mikrokontrolerów MCS-251/151 przedstawiono w tabeli 1.1.

Obecnie Intel, dążąc do rynku procesorów Pentium, wycofuje produkcję kryształów MCS-51. Generalnie dla konkretnego dewelopera może to pozostać niezauważone, chyba że zastosuje mikrokontrolery 8xC51GB i 80C152Jx, które nie mają swoich dokładnych odpowiedników wśród produktów innych firm. Jak wszystkie inne mikrokontrolery z rodziny MCS-51, wszystkie były wielokrotnie powielane przez inne firmy.

Obecnie różne firmy produkują wiele modyfikacji i analogów tej rodziny, zarówno przez Intela, jak i innych producentów, częstotliwość zegara i pojemność pamięci wzrosły dziesięciokrotnie i nadal rosną. Uzupełniany jest również zestaw modułów wbudowanych w LSI, duża liczba nowoczesnych modeli jest wyposażona w rezydentny szybki ADC, który ma do 12 cyfr, a teraz może być ich więcej. Ale sercem rodziny MCS51 są BIS 8051, 80C51, 8751, 87C51, 8031, 80C31 firmy Intel, których pierwsze próbki zostały wydane w 1980 roku.

Mikrokontrolery z rodziny MCS51 wykonane są w wysokiej jakości technologii n-MOS (seria 8XXX, analogowa - seria 1816 w Rosji i na Białorusi) oraz k-MOS (seria 8ХСХХ, analogowa - seria 1830). Drugi znak po 8 oznacza: 0 - brak EPROM na chipie, 7 - EPROM 4K z wymazywaniem UV. Trzeci symbol: 3 - ROM zostanie skrystalizowany, 5 - jeśli nie ma EPROM, to na chipie będzie maska ROM.

I tak 80S51 - LSI według technologii k-MOS z zamaskowaną pamięcią ROM na chipie, 8031 - LSI n-MOS bez pamięci programu (ROM, EPROM) na chipie, 8751 - LSI n-MOS z rezydentną (umieszczoną na chip) EPROM z wymazywaniem ultrafioletowym. Dalej rozważymy LSI 8751, zgłaszając w razie potrzeby zastrzeżenia co do różnic w innych obwodach, podając parametry, które zostały opublikowane dla pierwszego szeregowego LSI. W razie potrzeby dodatkowe informacje o wszystkich nowoczesnych modyfikacjach można znaleźć w instrukcjach firmowych i dokumentacji technicznej.

A. Ogólna charakterystyka i przypisanie pinów

Rodzina MCS51 opiera się na pięciu modyfikacjach MK (posiadających identyczne podstawowe cechy), między którymi główną różnicą jest implementacja pamięci programu i pobór mocy (patrz Tabela 3.1). Mikrokontroler jest ośmiobitowy, tj. posiada komendy do przetwarzania ośmiobitowych słów, ma architekturę Harvarda, częstotliwość taktowania podstawowych próbek z rodziny wynosi 12 MHz.

Tabela 3.1.

|

Mikroukłady |

Wewnętrzna pamięć programu, bajty |

Typ pamięci programu |

Wewnętrzna pamięć danych, bajty |

Częstotliwość zegara, MHz |

Pobór prądu, mA |

MK 8051 i 80C51 zawierają programowalną maskę ROM pamięci programu o pojemności 4096 bajtów podczas produkcji kryształu i są przeznaczone do użytku w masowej produkcji. MK 8751 zawiera EPROM o pojemności 4096 bajtów z wymazywaniem w ultrafiolecie i jest wygodny na etapie rozwoju systemu podczas debugowania programów, a także przy produkcji w małych partiach lub przy tworzeniu systemów wymagających ponownego

okresowa korekta.

MK 8031 i 80C31 nie zawierają wbudowanej pamięci programu. Podobnie jak poprzednio opisane modyfikacje, mogą wykorzystywać do 64 KB zewnętrznej pamięci programu i mogą być skutecznie stosowane w systemach wymagających znacznie większej objętości (niż 4 KB na chipie) pamięci programu.

Każdy MC z rodziny zawiera rezydentną pamięć danych o pojemności 128 bajtów z możliwością rozszerzenia łącznej ilości pamięci RAM do 64 KB poprzez zastosowanie zewnętrznej pamięci IC RAM.

centralny ośmiobitowy procesor;

4 KB pamięci programu (tylko 8751 i 87C51);

pamięć danych 128 bajtów;

cztery ośmiobitowe programowalne porty we/wy;

dwa 16-bitowe wielotrybowe timery / liczniki;

system przerwań autowektorowych z pięcioma wektorami i dwoma kontrolowanymi przez oprogramowanie poziomami priorytetów;

interfejs szeregowy zawierający uniwersalny dupleksowy nadajnik-odbiornik zdolny do pracy w czterech trybach;

generator zegara.

System poleceń MK zawiera 111 podstawowych poleceń w formacie 1, 2 lub 3 bajtów. Mikrokontroler posiada:

32 rejestry ogólnego przeznaczenia RON, zorganizowane jako cztery banki po osiem rejestrów, każdy o nazwach R0 ... R7, wybór jednego lub drugiego banku jest określany przez program poprzez ustawienie odpowiednich bitów w rejestrze stanu programu PSW;

128 flag kontrolowanych przez oprogramowanie (procesor bitowy, patrz poniżej);

zestaw rejestrów funkcji specjalnych kontrolujących elementy MK. Istnieją następujące tryby pracy mikrokontrolera:

1). Reset ogólny. 2) Normalne funkcjonowanie. 3) Tryb niskiego poboru mocy i tryb bezczynności. 4). Tryb programowania rezydentnego EPROM, jeśli istnieje.

Tutaj skupimy się na pierwszych dwóch trybach działania, szczegółowy opis składu i działania MC we wszystkich trybach znajduje się w Dodatku A1.

RON i strefa procesora bitowego znajdują się w przestrzeni adresowej rezydentnej pamięci RAM o adresach od 0 do 80h.

W górnej strefie adresów rezydentnej pamięci o dostępie swobodnym znajdują się rejestry funkcji specjalnych (SFR, Special Function Registers). Ich cel podano w tabeli. 3.2.

Tabela 3.2.

|

Przeznaczenie |

Nazwa | |

|

Bateria | ||

|

Zarejestruj się | ||

|

Rejestr statusu programu | ||

|

Wskaźnik stosu | ||

|

Wskaźnik danych. 2 bajty: | ||

|

Najmniej znaczący bajt | ||

|

Wysoki bajt | ||

|

Rejestr priorytetów przerwań | ||

|

Przerwanie rejestru włączania | ||

|

Rejestr trybu timera / licznika | ||

|

Rejestr kontroli timera / licznika | ||

|

Timer / Licznik 0. Starszy bajt | ||

|

Timer / Licznik 0. Młodszy bajt | ||

|

Timer / Licznik 1. Starszy bajt | ||

|

Timer / Licznik 1. Młodszy bajt | ||

|

Kontrola portu szeregowego | ||

|

Bufor portu szeregowego | ||

|

Zarządzanie zużyciem |

* - rejestry, przyznać się bitowe adresowanie

Rzućmy okiem na funkcje rejestrów SFR pokazane w tabeli 3.2.

Bateria ACC - rejestr baterii. Polecenia zaprojektowane do działania

ty z baterią użyj mnemonika „A”, na przykład, MOV A, P2 ... Mnemonik „ACC” jest używany na przykład do bitowego adresowania baterii. Zatem symboliczna nazwa piątego bitu akumulatora przy użyciu asemblera A5M51 będzie następująca: ACC. 5. .

Zarejestrować V ... Używany podczas operacji mnożenia i dzielenia. W przypadku innych instrukcji rejestr B może być traktowany jako dodatkowy rejestr superoperacyjny.

Zarejestrować fortuny programy PSW zawiera informacje o stanie programu i jest instalowany częściowo automatycznie na podstawie wyniku wykonanej operacji, częściowo przez użytkownika. Oznaczenia i przeznaczenie bitów rejestru podano odpowiednio w tabelach 3.3 i 3.4.

Tabela 3.3.

|

Przeznaczenie |

Tabela 3.4.

|

Przeznaczenie |

Przypisanie bitów |

Dostęp do bitu |

||||

|

Noś flagę. Zmiany podczas wykonywania szeregu instrukcji arytmetycznych i logicznych. |

Sprzęt lub oprogramowanie |

|||||

|

Dodatkowa flaga przenoszenia. Sprzęt ustawiony / wyczyszczony podczas instrukcji dodawania lub odejmowania w celu wskazania przeniesienia lub pożyczenia w bicie 3, gdy generowany jest najmniej znaczący półbajt wyniku (D0-D3). |

Sprzęt lub oprogramowanie |

|||||

|

Flaga 0. Flaga zdefiniowana przez użytkownika. |

Programowo |

|||||

|

Programowo |

||||||

|

Wskaźnik banku rejestru pracy |

Programowo |

|||||

|

Bank 0 z adresami (00H - 07H) Bank 1 z adresami (08H - 0FH) Bank 2 z adresami (10H - 17H) Bank 3 z adresami (18H - 1FH) | ||||||

|

Flaga przepełnienia. Sprzęt jest ustawiany lub usuwany podczas wykonywania instrukcji arytmetycznych, aby wskazać stan przepełnienia |

Sprzęt lub oprogramowanie |

|||||

|

Zapasowy. Zawiera wyzwalacz odczytu/zapisu, którego można użyć | ||||||

|

Bit parzystości. Sprzęt kasowany lub ustawiany w każdym cyklu instrukcji, aby wskazać parzystą lub nieparzystą liczbę bitów baterii w stanie „1”. |

Sprzęt lub oprogramowanie |

|||||

Wskaźnik stos SP - Rejestr 8-bitowy, którego zawartość jest zwiększana przed zapisaniem danych na stos podczas wykonywania poleceń PUSH i CALL. Przy początkowym resecie wskaźnik stosu jest ustawiony na 07H, a obszar stosu w pamięci RAM danych zaczyna się od adresu 08H. W razie potrzeby, poprzez przedefiniowanie wskaźnika stosu, obszar stosu może być zlokalizowany w dowolnym miejscu wewnętrznej pamięci RAM mikrokontrolerów.

Wskaźnik dane DPTR składa się z wysokiego bajtu (DPH) i niskiego bajtu

(DPL). Zawiera 16-bitowy adres podczas dostępu do pamięci zewnętrznej. Może być użyty

być zapisane jako rejestr 16-bitowy lub jako dwa niezależne rejestry ośmiobitowe.

Port0 - PortZ. Oddzielnymi bitami rejestrów funkcji specjalnych P0, P1, P2, P3 są bity - "zatrzaski" wyjść portów P0, P1, P2, P3.

Bufor spójny Port SBUF to dwa oddzielne rejestry: bufor nadawczy i bufor odbiorczy. Gdy dane są zapisywane do SBUF, trafiają one do bufora nadajnika, a zapisanie bajtu do SBUF automatycznie inicjuje transmisję przez port szeregowy. Gdy dane są odczytywane z SBUF, są one pobierane z bufora odbiornika.

Rejestry regulator czasowy. Pary rejestrów (TH0, TL0) i (TH1, TL1) tworzą 16-

Rejestry zliczania bitowego odpowiednio dla timera / licznika 0 i timera / licznika 1.

Rejestry kierownictwo. Rejestry funkcji specjalnych IP, IE, TMOD, TCON, SCON i PCON zawierają bity sterujące i bity statusu systemu przerwań, timer

liczniki / liczniki i port szeregowy. Zostaną one szczegółowo omówione poniżej.

RxD TxD INT0 INT1 T0 T1 WR

P1.2 P1.3 P1.4 P1.5 P1.6 P1.7

RST BQ2 BQ 1 EA

P3.0 P3.1 P3.2 P3.3 P3.4 P3.5 P3.6 P3.7

P2.0 P2.1 P2.2 P2.3 P2.4 P2.5 P2.6 P2.7

P0.0 P0.1 P0.2 P0.3 P0.4 P0.5 P0.6 P0.7

Podczas pracy MK zapewnia:

minimalny czas wykonania poleceń dodawania wynosi 1 μs;

mnożenie i dzielenie sprzętowe z minimalnym czasem wykonania 4 μs.

MK zapewnia możliwość ustawienia częstotliwości wewnętrznego oscylatora za pomocą kwarcu, łańcucha LC lub zewnętrznego oscylatora.

Rozszerzony system instrukcji zapewnia adresowanie bajtowe i bitowe, arytmetykę binarną i binarno-dziesiętną, sygnalizację przepełnienia i parzystość/nieparzystość oraz możliwość implementacji procesora logicznego.

Najważniejszą i wyróżniającą cechą architektury rodziny MCS51 jest to, że ALU oprócz wykonywania operacji na 8-bitowych typach danych może manipulować danymi jednobitowymi. Poszczególne bity dostępne przez oprogramowanie mogą być ustawiane, kasowane lub zastępowane przez ich uzupełnienie, mogą być wysyłane, sprawdzane i

Rysunek 3.2. Wnioski zewnętrzne

mikrokontroler

wykorzystywane w obliczeniach logicznych. Natomiast obsługa prostych typów danych (z istniejącymi

tendencja do zwiększania długości słów) może na pierwszy rzut oka wydawać się krokiem wstecz, ta jakość sprawia, że rodzina mikrokontrolerów MCS51 szczególnie nadaje się do zastosowań wykorzystujących kontrolery. Algorytmy tych ostatnich na swój sposób zakładają obecność wejściowych i wyjściowych zmiennych boolowskich, które są trudne do zaimplementowania przy użyciu standardowych mikroprocesorów. Wszystkie te właściwości są zbiorczo określane jako rodzina procesorów logicznych MCS51. Dzięki tak potężnej jednostce ALU, rodzina instrukcji MCS51 jest równie dobrze przystosowana do aplikacji sterujących w czasie rzeczywistym i algorytmów intensywnie przetwarzających dane.

Schemat ideowy mikrokontrolera pokazano na ryc. 3.2. W wersji podstawowej zapakowany jest w 40-pinową obudowę DIP. Rozważmy cel wniosków.

Zacznijmy od pinów zasilania «0 V" oraz „5 V" , za który otrzymuje główne pożywienie. Pobór prądu podano w tabeli. 3.1.

Wyjście „RST” - reset mikrokontrolera. Gdy aktywny wysoki poziom zostanie zastosowany do tego pinu, tryb pospolity dumping a MK wykonuje następujące czynności:

Ustawia licznik poleceń PC i wszystkie rejestry funkcji specjalnych, z wyjątkiem zatrzasków portów P0-P3, wskaźnika stosu SP i rejestru SBUF, na zero;

wskaźnik stosu jest ustawiony na 07H;

wyłącza wszystkie źródła przerwań, liczniki czasowe i szeregowe

wybiera BANK 0 RAM, przygotowuje porty P0-P3 do odbioru danych i określa

rozdziela piny ALE i PME jako wejścia do zewnętrznej synchronizacji;

w rejestrach funkcji specjalnych PCON, IP i IE, zapasowe bity są ustawiane na wartości losowe, a wszystkie pozostałe bity są ustawiane na zero;

rejestr SBUF jest ustawiony na wartości losowe.

ustawia zatrzaski-zatrzaski portów P0-P3 na "1".

Stany rejestrów mikrokontrolera po zresetowaniu przedstawia tabela 3.5.

Tabela 3.5.

|

Informacja |

|

|

Nieokreślony |

|

|

0ХХХ0000В dla k-MOS 0XXXXXXXB dla n-MOS |

Pin RST pełni również funkcję alternatywną. Za jego pośrednictwem dostarczane jest zasilanie awaryjne, aby zachować niezmienioną zawartość pamięci RAM mikrokontrolera po usunięciu głównego.

wnioski BQ1, BQ2 – przeznaczony do podłączenia rezonatora kwarcowego, który określa częstotliwość zegara MK.

Wyjście EA` (mi zewnętrzne A sukienka – zewnętrzny adres) - przeznaczone do włączenia trybu odczytu kodów sterujących z zewnętrznej pamięci programu, gdy na to wyjście podany jest aktywny poziom niski. Kołek ma alternatywne przeznaczenie (funkcję). Zasilany jest napięciem programowania EPROM w trybie programowania.

Wyjście PME (P program m pamięć mi nabla – pozwolenie pamięć programy) - przeznaczony do sterowania cyklem odczytu z pamięci programu i jest automatycznie aktywowany przez MC w każdym cyklu maszyny.

Wyjście Ale (A sukienka L długość mi nabla – pozwolenie junior adresy) strobuje wyjście dolnej części adresu na porcie P0. Wyjście jest również wykorzystywane podczas programowania EPROM, gdy dostarczany jest do niego impuls strobujący.

MK zawiera cztery grupy portów: P0, P1, P2 i P3. To pozostałe 40 pinów mikrokontrolera. Porty te mogą służyć do przekazywania informacji we/wy bit po bicie, ale poza tym każdy z nich ma swoją własną specjalizację. Uogólniony schemat funkcjonalny portu pokazano na rys. 3.3. Port zawiera wyjściowe przełączniki FET podłączone do pinu, przełącznik funkcji, zatrzask na D-flip-flopie i logikę sterowania. Zatrzask na wewnętrznej magistrali MK można zapisać jeden lub zero. Ta informacja przechodzi przez przełącznik funkcji do klawiszy wyjściowych i wyjścia MK. W stanie jeden oba tranzystory N i N1 są wyłączone, ale N2 jest włączony. W stanie zero N otwiera się

Xia i N2 zamykają się. W momencie, gdy port wykonuje alternatywną funkcję, do której jest specjalizowany, stan pinu zostaje zwolniony. Mikrokontroler może oddzielnie odczytywać stan zatrzasku portu oraz stan jego wyjścia, ustawiany zewnętrznym sygnałem. W tym celu w asemblerze MK znajdują się specjalne polecenia, które aktywują odpowiednie linie. Aby odczytać stan pinów, odpowiedni zatrzask portu musi:

być wstępnie nagrane

Z wewnętrznego

Sterowanie zatrzaskiem

Selektor funkcji

Vcc

Weekendy

jednostka. Gdy linia "read latch" jest aktywowana na wyjściu komórki "AND", do której ta linia jest podłączona,

to opona MK D Q

Zatrzask napisz C Q

Czytanie zatrzasku

Pin portu

Stan zatrzasku, który jest dostarczany do wewnętrznej magistrali MC, jest aktywowany, gdy

„Odczyt wyjścia” - stan wyjścia zewnętrznego portu.

Port P0 - uniwersalny port dwukierunkowy

wejście wyjście. Poza tym portem

funkcja organizowania zewnętrznych magistral adresowych oraz

Ryż. 3.3. Schemat funkcjonalny portu mikrokontrolera

dane do rozszerzenia pamięci programu i pamięci danych

mikrokontroler. W przypadku dostępu do zewnętrznej pamięci programu lub wykonania polecenia dostępu do zewnętrznej pamięci danych, na kołkach portu ustawiana jest dolna część adresu (A0...A7), który jest bramkowany wysoko na kołku ALE. Następnie podczas zapisu do pamięci danych, zarejestrowane informacje z wewnętrznej magistrali MC są podawane na piny portu P0. W operacjach odczytu natomiast informacje z pinów portu trafiają do magistrali wewnętrznej. Cechą portu P0 jest brak „podciąganego” tranzystora N2, który zapewnia zasilanie na wyjściu. Pisanie do zatrzasku portu urządzenia po prostu wprowadza go w stan wysokiej impedancji, który jest niezbędny do prawidłowego działania magistrali danych. W przypadku konieczności zasilania urządzeń zewnętrznych przez wyjście należy doprowadzić zewnętrzne rezystory z obwodów zasilających na wyjście portu.

Port Р1 - uniwersalny dwukierunkowy port I/O bez alternatywnych funkcji.

Port P2 - uniwersalny dwukierunkowy port I / O, jako alternatywna funkcja, wykonująca wydawanie starszej części adresu (A8 ... A15) podczas dostępu do pamięci zewnętrznej.

Port P3 - uniwersalny dwukierunkowy port wejścia-wyjścia, którego każdy bit zapewnia realizację różnych alternatywnych funkcji. W tym przypadku funkcje alternatywne są implementowane tylko wtedy, gdy są one zapisane w zatrzaskach portu, w przeciwnym razie wykonywanie funkcji alternatywnych jest zablokowane. Wymieńmy je osobno dla każdego bitu:

P3.0 – RxD (r e x zewnętrzne D ate, read external data) - wejście wbudowanego nadajnika-odbiornika szeregowego.

P3.1 – TxD (T tak x zewnętrzne D ate, przesyłaj dane zewnętrzne) - wyjście wbudowanego nadajnika-odbiornika szeregowego.

P3.2 – INT0` (WEWN errupt, interrupt) - wejście zewnętrznego przerwania 0.

P3.3 – INT1` - wejście przerwania zewnętrznego 1.

P3.4 – C / T0 - wejście zera wbudowanego timera / licznika.

P3.5 – C / T1 - wejście pierwszego wbudowanego timera / licznika.

P3.6 – WR` (W rite, write) - wyjście sterujące cyklem zapisu w pamięci danych.

P3.7 – RD` (r ead, read) - sterowanie wyjściem cyklu odczytu z pamięci danych.

Piny portów P1, P2 i P3 są w stanie dostarczyć prąd około 0,2 mA w jednej jednostce i odbierać prąd 3 mA przy zerze, piny portu P0 są mocniejsze i mogą dostarczać prąd około 0,8 mA na jednostkę i otrzymywanie prądu 5 mA przy zerze. Krótka informacja o przeznaczeniu wyprowadzeń mikrokontrolera znajduje się w tabeli 3.6.

Tabela 3.6.

|

Przeznaczenie |

Przydzielenie pinu | ||

|

8-bitowy dwukierunkowy port P1. Wejście adresowe A0-A7 podczas sprawdzania wewnętrznej pamięci ROM (EPROM) |

wejdź do wyjścia |

||

|

Ogólny sygnał resetu. Wyjście zapasowej mocy RAM z zewnętrznego źródła (dla 1816) | |||

|

8-bitowy dwukierunkowy port P3 z dodatkowymi funkcjami |

wejdź do wyjścia |

||

|

Dane szeregowe odbiornika - RxD | |||

|

Dane szeregowe nadajnika - TxD | |||

|

Wejście przerwania zewnętrznego 0- INT0` | |||

|

Wejście przerwania zewnętrznego 1-INT1` | |||

|

Wejście timera / licznika 0: - T0 | |||

|

Timer / Licznik 1 Wejście: - T1 | |||

|

Wyjście sygnału stroboskopowego podczas zapisu do zewnętrznej pamięci danych: - WR` | |||

|

Wyjście sygnału stroboskopowego podczas odczytu z zewnętrznej pamięci danych - RD` | |||

|

Wyprowadzenia do podłączenia rezonatora kwarcowego. |

wyjście z wejścia |

||

|

Ogólny wniosek | |||

|

8-bitowy dwukierunkowy P2. Wyjście adresowe A8-A15 w trybie pracy z pamięcią zewnętrzną. W trybie kontroli wewnętrznej pamięci ROM piny P2.0 - P2.6 są używane jako wejście adresu A8-A14. Wniosek P2.7 - pozwolenie na odczyt ROM. |

wejdź do wyjścia |

||

|

Rozdzielczość pamięci programu | |||

|

Sygnał wyjściowy włączenia blokowania adresu. Podczas programowania sygnału EPROM: PROG |

wejdź do wyjścia |

||

|

Blokowanie pracy z pamięcią wewnętrzną. Podczas programowania EPROM podawany jest sygnał UPR |

wejdź do wyjścia |

||

|

8-bitowy dwukierunkowy port P0. Magistrala adresowa / danych r współpracuje z pamięcią zewnętrzną. Wyjście danych D7-D0 w trybie sprawdzania wewnętrznej pamięci ROM (EPROM). |

wejdź do wyjścia |

||

|

Moc wyjściowa ze źródła napięcia + 5 V |

Stan systemu przerwań jest odpytywany na końcu każdego cyklu maszyny w fazie S5P2, z wyjątkiem poleceń RETI i wszelkich poleceń odnoszących się do rejestrów IE i IP. Od momentu naprawienia żądania przerwania do obsługi przerwania trwa od 38 do 86 okresów częstotliwości fOSC, w zależności od fazy żądania i liczby cykli maszyny rozkazu, podczas którego wykonanie zostało odebrane żądanie .

Gdy przerwanie jest zaimplementowane sprzętowo, wykonywana jest instrukcja LCALL addr16, która zapewnia zapamiętanie na stosie aktualnego stanu licznika programu (przechowywanie adresu zwrotnego) i przejście do początkowego adresu addr16 odpowiedniej procedury obsługi. Każde źródło żądania przerwania ma swoje własne

adres początkowy (wektor przerwań): |

||||

Przerwanie zewnętrzne INT0. |

||||

Zegar przerwań / licznik TC0. |

||||

Przerwanie zewnętrzne INT1. |

||||

Zegar / licznik przerwań TC1. |

||||

Przerwanie portu szeregowego. |

||||

2.7. Metody adresowania i system poleceń rodziny MCS-51

System dowodzenia rodziny MCS-51 koncentruje się na organizacji elastycznego wprowadzania i wyprowadzania danych poprzez uniwersalne porty P0...P3 oraz podstawowe przetwarzanie informacji. Specjalna uwaga wypłacane na operacje z bitami i przekazywaniem kontroli według ich wartości. Instrukcje wykonujące takie operacje stanowią dużą grupę i wraz z odpowiednim sprzętem tworzą tzw. „procesor logiczny” w architekturze MCS-51.

System poleceń zapewnia programiście możliwość korzystania z większości operacji z komplet metody adresowania i dostępne za pomocą oprogramowania zasoby sprzętowe.

2.7.1. Metody adresowania

Każda instrukcja informuje procesor o operacji do wykonania i metodach dostępu do operandów. Kod polecenia ma kilka pól, które mają określony cel funkcjonalny. Najważniejszymi polami każdego polecenia są kod operacji (CPC), który określa działanie polecenia oraz część adresowa. Pola części adresowej zawierają informacje o adresach operandów i wyniku operacji, aw niektórych przypadkach informacje o adresie następnego polecenia.

Jeśli adres wskazuje na numer komórki pamięci, w której znajduje się operand lub gdzie jest zapisany, nazywa się to adresem bezpośrednim.

Metody adresowania to zbiór mechanizmów dostępu do operandów. Niektóre z nich są proste, prowadzą do kompaktowego formatu poleceń i szybki dostęp do operandu, ale mają ograniczoną ilość dostępnych zasobów. Inne pozwalają operować wszystkimi zasobami dostępnymi w systemie, ale komenda okazuje się długa, na jego

wejście i wykonanie jest czasochłonne. Zestaw metod adresowania w każdym zestawie instrukcji jest kompromisową kombinacją znanych mechanizmów adresowania wybranych przez architektów na podstawie zestawu zadań do rozwiązania.

Poniżej przedstawiono główne metody adresowania stosowane w rodzinie poleceń MCS-51.

Adresowanie niejawne... Polecenie nie zawiera wyraźnych instrukcji dotyczących adresu operandu uczestniczącego w operacji lub adresu, pod którym umieszczany jest wynik operacji, ale adres ten jest domniemany. W poleceniach akumulator jest najczęściej niejawnie adresowany jako odbiornik wyniku operacji. Na przykład wynik dodawania zawartości akumulatora (A) i rejestru R1 bieżącego banku danych za pomocą polecenia ADD A, R1 jest zapisywany w niejawnie adresowalnym akumulatorze. Całe podane polecenie zajmuje w pamięci jeden bajt, podczas gdy adres samego akumulatora (8Eh obszaru SFR) zawiera jeden bajt.

Adresowanie bezpośrednie... Pole adresu polecenia zawiera:

Adres nie jest adresem operandu, ale samym operandem. Adresowanie bezpośrednie jest oznaczone znakiem specjalnym # przed numerem. Na przykład za pomocą polecenia MOV A, # 15h do akumulatora ładowana jest liczba szesnastkowa 15 (drugi bajt polecenia). W systemie poleceń adresowanie bezpośrednie jest oznaczane jako #dane, gdzie dane są liczbą

(dane = 00h ... FFh).

Adresowanie bezpośrednie... Pole adresu polecenia wskazuje bezpośredni adres komórki pamięci danych, w której znajduje się operand lub gdzie jest zapisany. Np. poleceniem MOV A, 15h ładuje się do akumulatora zawartość komórki DSEG o adresie 15h. Komórka pamięci jest bezpośrednio adresowalna, podczas gdy akumulator jest niejawny. W zależności od lokalizacji adresowanego argumentu, adresowanie bezpośrednie dzieli się na rejestr bezpośredni i bezwzględny.

Bezpośrednie adresowanie rejestru... Pole adresu polecenia zawiera bezpośredni adres rejestru bieżącego banku rejestrów. W każdym banku jest osiem rejestrów i do ich adresowania wymagany jest trzybitowy adres przekazujący. W mnemotechnice poleceń rejestr adresowalny jest oznaczony Rn, gdzie n = 0 ... 7. Wszystkie pola poleceń mieszczą się w jednym bajcie. Nazywa się to adresowaniem krótkim. Na przykład MOV R4, R1.

Bezpośrednie adresowanie bezwzględne pozwala odnieść się do dowolnej komórki DSEG i obszaru SFR. Adres bezpośredni w tym przypadku zajmuje jeden bajt, a polecenie dwa bajty. W systemie poleceń bajt adresu bezpośredniego jest oznaczony słowem direct (direct = 00h… FFh). Na przykład, instrukcja MOV 80h, R2 (lub MOV P0, R2) ładuje zawartość rejestru R2 bieżącego banku danych do portu P0 (lokalizacja 80h obszaru SFR). Jeśli oba operandy mają bezpośrednie adresowanie bezwzględne, instrukcja staje się trzybajtowa (na przykład MOV 80h, 15h).

Adresowanie pośrednie... Pole adresu zawiera adres komórki pamięci, w której znajduje się bezpośredni adres operandu. W systemie poleceń specjalny symbol @ oznacza adresowanie pośrednie. Nieruchomość

adresy bezpośrednie posiadają rejestry R0 i R1 (@Ri, i = 0,1) każdego banku rejestrów. Np. jeżeli zawartość rejestru R1 bieżącego banku rejestrów wynosi 15h, to instrukcja MOV A,@R1 wykona tę samą akcję co powyższa instrukcja MOV A,15h - załaduje zawartość komórki pamięci DSEG z adresem 15h do akumulatora. Jednak komenda MOV A, @R1 jest jednobajtowa, ale co najważniejsze, jest tu możliwość programowo zmienić adres, zmieniając zawartość rejestru R1.

Adresowanie względne... W przypadku adresowania względnego adres bezpośredni jest tworzony przez dodanie adresu bazowego do pola adresu polecenia. Zawartość licznika programu jest używana jako adres bazowy, a pole adresu polecenia jest ośmiobitowym offsetem rel (względnym). Liczba rel jest interpretowana przez polecenie jako liczba całkowita ze znakiem, reprezentowana w uzupełnieniu do dwóch. Zakres jego prezentacji to (-128 ... + 127). Przy określaniu numeru rel należy pamiętać, że licznik programu wskazuje następne polecenie do wykonania. Adresowanie względne jest szeroko stosowane w poleceniach przekazywania sterowania, co pozwala na tworzenie relokowalnych modułów programu. Polecenia przesyłania sterowania z adresowaniem względnym umożliwiają organizowanie rozgałęzień względem aktualnej pozycji licznika programu PC w obu kierunkach o (-128 ... + 127) bajtów.

W programach asemblerowych, możesz określić etykietę do skoku w polu przesunięcia. W wyniku translacji asembler obliczy wartość offsetu, jeśli nie przekracza (-128 ... + 127). W przeciwnym razie zostanie wyświetlony komunikat o błędzie.

Adresowanie podstawowe reprezentuje rodzaj adresowania względnego. Adres bezpośredni w tym przypadku jest tworzony przez dodanie adresu określonego w poleceniu z zawartością rejestru bazowego, w którym przechowywany jest adres bazowy. Funkcją rejestru bazowego w rodzinie MCS-51 jest rejestr wskaźnika danych DPTR lub licznik programu PC. Ten rodzaj adresowania jest szczególnie przydatny podczas przetwarzania tabel i tablic danych. W instrukcjach MOVC A, @A + DPTR i MOVC A, @A + PC 16-bitowy adres do przodu jest tworzony jako suma zawartości DPTR i A lub PC i A.

Adresowanie stron... W przypadku korzystania ze stronicowania pamięć jest dzielona na serie stron o jednakowej długości. Strony są adresowane przez oddzielny rejestr stronicowania, a komórki pamięci w obrębie strony adresowane są przez adres zawarty w poleceniu. Adres bezpośredni jest tworzony przez łączenie (dodawanie) adresu stron i adresu komórki pamięci na stronie. W instrukcji MOVX A, @Ri, port P2 (starszy bajt adresu) pełni funkcję rejestru strony, a zawartość rejestru Ri (młodszy bajt adresu) ustawia adres w obrębie strony. W tym przypadku pamięć jest podzielona na 256 stron po 256 komórek w każdej z nich.

Adresowanie stosu jest używany w poleceniach nieadresowalnych i jest połączeniem metod adresowania auto-inkrementacji i auto-dekrementacji, działających na zasadzie LIFO (Last Input - First Out) - "ostatnie weszło - pierwsze wyszło". Stos znajduje się w DSEG i rośnie w kierunku zwiększania adresu. Adres wierzchołka stosu jest zawarty we wskaźniku stosu SP. Kiedy bajt jest zapisywany na stosie, zawartość SP jest najpierw zwiększana, a następnie wykonywany jest zapis pod ten adres. Podczas odczytu bajtu ze stosu najpierw odczytuje adres wskazany przez SP, a następnie dekrementuje SP. Używając stosu należy pamiętać, że głębokość stosu (maksymalna liczba komórek pamięci zajmowanych przez stos) nie jest sterowana sprzętowo. Przy nadmiernym wzroście stosu komórki pamięci, które nie są do tego przeznaczone, mogą być zajęte utratą zawartych w nich informacji. Stos sprzętowy jest używany do przechowywania adresu zwrotnego podczas obsługi przerwania.

2.7.2. Zestaw poleceń rodziny MCS-51

System dowodzenia przedstawiono w tabelach A2.1...A2.6 Załącznika 2. Tabele wskazują nazwę dowództwa, jego mnemoniki, kod binarny operacji, wpływ wykonanego polecenia na flagi C, OV, AC i P, długość polecenia w bajtach (B) i czas wykonania w cyklach maszyny (C), a także treść transformacji wykonywanej przez Komenda. Przecinek jest używany jako separator pól adresowych w poleceniach. Aby poprawić czytelność, możesz dodać spacje po przecinku, jeśli używany asembler je obsługuje.

Cały zestaw poleceń można podzielić na 5 grup: operacje przesyłania danych, operacje arytmetyczne, operacje logiczne, operacje na bitach i operacje przesyłania sterowania.

Grupa poleceń do operacji przesyłania danych(tabela A2.1) z-

posiada MOV (przesyłanie danych między DSEG i RSEG), MOVC (między CSEG i A), MOVX (między XSEG i A), polecenia dostępu do stosu PUSH i POP oraz dwa polecenia wymiany XCH i XCHD. Wszystkie rozkazy przesyłania danych, które odbierają baterię, ustawiają flagę parzystości P zawartości baterii, a rozkazy adresowania bezpośredniego, które odbierają rejestr PSW, zmieniają wszystkie flagi. Najbardziej pojemna jest instrukcja MOV, która wykorzystuje cztery metody adresowania: register direct (A, Rn, DPTR), direct (direct), indirect (@Ri), direct (#data, #data16). Drugi argument instrukcji to źródło, pierwszy to cel. Istnieją trzy metody adresowania (z wyjątkiem bezpośredniej) do wskazania miejsca docelowego i wszystkie cztery do wskazania źródła. Trzybajtowe bezpośrednie, bezpośrednie polecenie MOV przesyła między dowolnymi dwoma lokalizacjami pamięci (DSEG i SFR), w tym RSEG. Do wymiany z RSEG dostępne są specjalne formaty dwu- i jednobajtowe:

Specjalna instrukcja MOV DPTR, #data16, ładuje 16-bitowy wskaźnik DPTR z data16.

Instrukcja MOVC umożliwia odczytywanie informacji z pamięci programu CSEG nie do rejestru poleceń urządzenia sterującego, ale do baterii urządzenia operacyjnego. Polecenie wykorzystuje dwie metody adresowania: na podstawie DPTR i względem komputera. W obu przypadkach offset (indeks) bez znaku jest przechowywany w akumulatorze. Bateria służy również jako odbiornik wyniku. Polecenie umożliwia szybkie transkodowanie między tabelami.

Dostęp do pamięci zewnętrznej uzyskuje się za pomocą instrukcji MOVX. Wymiana odbywa się za pomocą bajtów między baterią a zewnętrznym XSEG. Komórka XSEG może być adresowana na dwa sposoby: pośrednio przez 16-bitowy wskaźnik DPTR oraz pośrednio przez 8-bitowy wskaźnik Ri, i = 0,1. W tym drugim przypadku rejestr P2 jest używany jako rejestr stronicowy.

Bezadresowe polecenia PUSH i POP zapewniają transfer danych

pomiędzy DSEG, RSEG i SFR.

Instrukcja wymiany XCH zapewnia dwukierunkową wymianę bajtów, a instrukcja XCHD najmniej znaczące tetrady operandów bajtowych.

Grupa poleceń arytmetycznych(tabela A2.2) współ-

zawiera instrukcje dodawania ADD, dodawania z przeniesieniem ADDC, odejmowania z pożyczonym SUBB, inkrementacji i dekrementacji o jeden INC i DEC, dodawania BCD w formacie spakowanym, mnożenia MUL i dzielenia DIV. Operacje są wykonywane na liczbach całkowitych bez znaku. W operacjach dodawania i odejmowania akumulator jest pierwszym argumentem i odbiornikiem wyniku. Rejestr bezpośredni, bezpośrednie adresowanie bezwzględne, bezpośrednie i pośrednie są używane do zdefiniowania drugiego argumentu. Operacje INC i DEC dotyczą akumulatora, bezpośrednio adresowalnego rejestru lub bezpośrednio lub pośrednio adresowalnej lokalizacji pamięci. Ponadto operacja INC dotyczy zawartości 16-bitowego rejestru wskaźników DPTR.

Operacje mnożenia i dzielenia liczb całkowitych bez znaku obejmują akumulator i rejestr B. W mnożeniu 8-bitowa wartość A jest mnożona przez 8-bitową wartość B, a 16-bitowy wynik jest zapisywany w parze BA. W takim przypadku rejestr B przechowuje górną część produktu. Flaga OV jest ustawiana, jeśli iloczyn jest większy niż 255. Gdy 8-bitowa wartość A jest podzielona przez 8-bitową wartość B, iloraz jest zapisywany w A, a reszta jest zapisywana w B. Po podjęciu próby aby podzielić przez 0, ustawiona jest flaga przepełnienia OV.

Polecenie korekcji dziesiętnej akumulatora DA jest umieszczane po poleceniu dodawania. Warunki muszą być przedstawione w kodzie BCD. Korekta wykonywana jest w standardowy sposób.

Grupa poleceń do operacji logicznych(tabela A2.3 ) zawiera trzy typowe operacje: ANL - logiczne AND, ORL - logiczne OR, XRL - logiczne wykluczające OR. Źródło pierwszego operandu

służy albo akumulator A albo bezpośrednio adresowalna komórka pamięci. Drugi argument jest określony przez jedną z czterech podstawowych metod adresowania. W skład grupy wchodzą również pojedyncze operacje nad zawartością akumulatora: CLR - wyczyść, CPL - inwersja, a także RL, RLC, RR i RRC - operacje przesunięć cyklicznych i rozszerzonych w prawo iw lewo. Obejmuje to również operację wymiany notebooków w akumulatorze SWAP, co można interpretować jako cykliczne przesunięcie bajtu o cztery cyfry.

Grupa poleceń operacji bitowych(tabela A2.6) zawiera współ-

komendy SETB - ustawienie bitu na 1, CLR - zerowanie bitu na 0, CPL - odwrócenie bitu, ANL i ORL - AND i logiczne OR zawartości flagi C i bitu adresowanego bezpośrednio, MOV - transfer bitów.

V operacji bitowych, flaga C działa jak akumulator logiczny. Operandy są zawartością flagi C lub bezpośrednio adresowanego bitu obszaru BSEG. Operacje ANL i ORL mogą wykorzystywać zawartość bezpośrednio adresowalnego bitu (bit) lub inwersję zawartości (bit).

V ta grupa obejmuje również polecenia warunkowego rozgałęzienia z względnym 8-bitowe przesunięcie rel. Skok warunkowy może być wykonany zarówno z bitem ustawionym (polecenie JB), jak i skasowanym (polecenie JNB). Na szczególną uwagę zasługuje polecenie JBC, które gdy ustaw bit implementuje rozgałęzienie i jednocześnie czyści bit do 0.

Grupa poleceń transferu sterowania(tabele A2.4 i A2.5) z:

zawiera polecenia skoku bezwarunkowego AJMP, LJMP, SJMP, JMP, skok warunkowy JZ, JNZ, CJNE, wywołanie ACALL, LCALL, powrót RET, RETI i modyfikację skokiem warunkowym DJNZ. Dołączone jest również puste polecenie NOP.

V polecenia transferu sterowania są szeroko stosowane adresowanie względne pozwalając na tworzenie relokowalnych modułów oprogramowania. Adres względny to 8-bitowe przesunięcie rel to bajt ze znakiem, który zapewnia skok (–128…+127) bajtów w stosunku do bieżącej pozycji komputera. Do przeskoku do dowolnego innego punktu w przestrzeni adresowej 64 KB można użyć bezpośredniego adresu 16 lub pośredniego adresu @A + DPTR. W tym drugim przypadku zawartość A jest interpretowana jako liczba całkowita bez znaku. W celu zapewnienia kompatybilności z rodziną MCS-48 wprowadzono krótki wariant adresowania bezpośredniego addr11 w ramach bieżącej strony o wielkości 2 KB.

Wszystkie te typy adresowania są używane w instrukcjach skoku. W poleceniach wywołania używane są tylko bezpośrednie metody adresowania addr16 i adresowanie na stronie addr11. Wszystkie polecenia warunkowe używają tylko adresowania względnego.

Gdy mikrokontroler rozpozna żądanie przerwania, generuje instrukcję LCALL addr16, która automatycznie zapewnia, że adres powrotny jest przechowywany w stosie. Informacje o stanie programu (zawartość rejestru PSW) nie są zapisywane automatycznie. W której